Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

Изобретение предназначено для использования в универсальных и спеко5 76, П вий Om6j. ка5 циализированных вычислительных машинах . Изобретение позволяет повысить быстродействие за счет сокращения числа формируемь х микрокоманд и сокращения цикла работы устройства путем совмещения во времени процесса формирования адреса микрокоманд. Устройство содержит счетчик 1 адреса, блок 2 памяти микрокоманд, регистр 3 микрокоманд, первый 4, второй 5, третий 6, четвертый 9 дешифраторы, регистр 7 возврата, регистр 8 адреса, первый 10, второй 11, третий 12 триггеры , элемент ИЛИ-НЕ 13, элемент НЕ 14, элемент И-НЕ 15, ключ 16 регистра возврата, ключ 17 константы. 2 ил. вылод (Л СО 4 /Яблоку (риг.1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

os> SU <а (51) 4 С 06 F 9/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

АчИ

Dm î87

17 д й7д

Bud

0m Ch бй7 5

Avd

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3993536/24-24 (22) 09.12.85 (46) 30.05.87 ° Бюл. № 20 (72) В.Г.Миронов, А.M.Áoéêåâè÷, Л.С.Косов, С.С.Свердлов и Т.A.Ëîáàчева (53) 681.3(088.8) (56) Авторское свидетельство СССР № 935959, кл. G 06 F 9/22, 1981.

Авторское свидетельство СССР

¹ 1019450, кл. G 06 F 9/22, 1982. (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО

УПРАВЛЕНИЯ (57) Изобретение предназначено для использования в универсальных и специализированных вычислительных машинах. Изобретение позволяет повысить быстродействие за счет сокращения числа формируемых микрокоманд и сокращения цикла работы устройства путем совмещения во времени процесса формирования адреса микрокоманд. Устройство содержит счетчик 1 адреса, блок 2 памяти микрокоманд, регистр 3 микрокоманд, первый 4, второй 5, третий 6, четвертый 9 дешифраторы, ре— гистр 7 возврата, регистр 8 адреса, первый 10, второй 11, третий 12 триггеры, элемент ИЛИ-НЕ 13, элемент НЕ

14, элемент И вЂ” НЕ 15, ключ 16 регистра возврата, ключ 17 константы. 2 ил.

1 !3!

Изобретение относится к вычислительной технике и может быть испопьзовано в универсальных и специализированных вычислительных машинах.

Целью изобретения является повышение быстродействия.

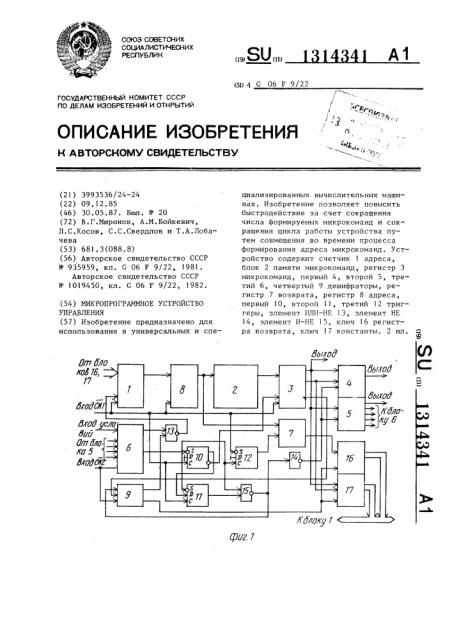

На фиг ° 1 представлена схема предлагаемого устройства; на фиг.2 — диаграмма работы устройства.

Микропрограммное устройство управления содержит счетчик 1 адреса, блок 2 памяти микрокоманд, регистр 3 микрокоманд, первый дешифратор 4, второй дешифратор 5, третий дешифратор 6, регистр 7 возврата, регистр 8 адреса, четвертый дешифратор 9, первый 10, второй 11, третий 12 тригге— ры, элемент ИЛИ-НЕ 13, элемент НЕ 14, И-НЕ 15, ключ 16 регистра возврата и ключ 17 константы.

Устройство работает следующим образом.

Работа устройства осуществляется двумя сериями синхроимпульсов: основными синхроимпульсами СИ 1 (фиг.2а) и вспомогательными СИ 2 (фиг.2о), которые смещены на полпериода относительно основных синхроимпульсов.

При последовательном исполнении микропрограммы формирование адреса микрокоманды А начинается по положиЬ тельному фронту каждого основного синхроимпульса СИ 1, поступающего на счетный вход счетчика 1 адреса, находившегося в состоянии А„, (фиг.26).

По положительному фронту следующего основного синхроимпульса CH 1, поступающего на первый вход регистра 8 адреса, содержимое счетчика 1 адреса

А„ переписывается в регистр 8 адреса (фиг.2 ) и одновременно в счетчике адреса формируется адрес следующей микрокоманды А „+, (фиг.2 6). По адресу А„ из блока 2 памяти осуществляется выборка микрокоманды А, которая записывается по первому входу в регистр 3 микрокоманд при поступлении на его второй вход положительного фронта основного синхроимпульса СИ 1 (фиг.2у). Таким образом, по каждому положительному фронту СИ 1 при последовательном исполнении микропрограммы одновременно происходит: в счетчик 1 адреса прибавляется единица, предыдущее содержимое счетчика 1 переписывается в регистр 8 адреса, выбранная из блока 2 памяти микрокоманда пере434) писывается

Импульс с первого выхода дешифратора

6 поступает на первый вход элемента

ИЛИ-НЕ 13 и с его выхода импульс инверсной полярности (фиг.2u) поступает на второй вход загрузки счетчика

1 адреса микрокоманд и потенциалом логического нуля записывает информацию с шины данных Ам в этот счетчик (фиг. 2 и к и 6 ) . .Тем самым в этом счетчике запишется адрес микрокоман10

f5

2 в регистр 3 микрокоманд.

Предположим, что микрокоманда А> (фиг.2 ) является микрокомандой безусловного перехода к микрокоманде

А без возврата. Адрес перехода находится во внешнем устройстве, адрес внешнего устройства содержится в микрокоманде и поступает на первый вход данных первого дешифратора 4. На втором выходе регистра 3 микрокоманд устанавливается потенциал логического нуля, определяется А микрокоманда, т.е, разрешена работа по второму управляющему входу первого дешифратора 4, а на выходе ключа 17 константы сигнал отсутствует. Внешнее устройство получает разрешающий потенциал с выхода первого дешифратора 4 и выдает адрес перехода на шину данных (фиг.2 к). Код команды безусловного перехода поступает с первого выхода данных регистра 3 микрокоманд на первый вход данных второго дешифратора

5, на первом выходе которого формируется потенциал логического нуля (фиг.2>k), поступающий на первый вход дешифратора 6, определяющий микрокоманду безусловного перехода. Последний формирует одновременно два управляющих импульса разной полярности.

На первом выходе формируется импульс положительной полярности, на втором инверсной полярности (фиг.2$). Эти импульсы равны по длительности импульсам вспомогательной серии СИ 2, поступающей на пятый управляющий вход дешифратора 6, и формируются одновременно с первым импульсом СИ 2 вспомогательной серии, поступающем за импульсом основной серии СИ !, по положительному фронту которого микрокоманда А безусловного перехода без возврата была принята на регистре 3 микрокоманд (фиг.28,),), W ). ды„ к которой переходит микропрограмма. По потенциалу логического нуля на втором выходе дешифратора 6, пер3 1314341 самым на втором выходе первого триггера 10 был сформирован инверсный импульс, который запретил запись в регистр 3 микрокоманд по управляющему третьему входу микрокоманду Ад., Тем самым нарушается последовательная выборка микрокоманд из блока 2 памяти. Микрокоманда А „ не запишется в регистр 3 микрокоманд, а микрокоманда А будет храниться в этом регистре второй период основной синхросерии СИ 1 (фиг.2g). По этому же фронту импульса основной синхросерии

СИ 1, поступающего на второй вход регистра 8 адреса и на первый вход мента НЕ 14 приходит на третий управ-30 счетчика 1 адреса к содержимому счетчика прибавляется единица, т.е. в нем формируется адрес А< а старое содержимое указанного счетчика А переписывается в регистр 8 адреса (фиг.2а, 1 и c ). основной серии СИ 1, следующего вторым за импульсом, по которому микрокоманда А была принята в регистр 3 микрокоманд, поступающего на С-вход второго триггера 11, он устанавливается в нулевое состояние (фиг.2м), а в счетчике 1 адреса формируется адрес Ам,, при этом в регистр 8 адреса записывается адрес Ам .. а в регистр 3 микрокоманд — микрокоманда

Ам фиг.2ц,6, q и ) . Потенциал логического нуля с выхода второго триггера 11 поступает на первый вход элемента И-НЕ 15, на выходе которого

35 формируется потенциал логической.единицы (фиг.2м,н), который формирует потенциал логического нуля на выходе элемента НЕ )4 и .поступает на третий

40 вход первого дешифратора 4 и на второй вход второго дешифратора 5, тем самым разрешается их работа.

Предположим, что микрокоманда А является микрокомандой безусловного перехода к микрокоманде А„ с возвратом, причем адрес перехода содержится в самой микрокоманде.

В период между- первым импульсом

50 основной серии СИ 1, по которому микрокоманд.. А была принята в регистр

3 микрокоманд, и вторым импульсом этой серии элементы устройства работают так же как и при исполнении мик55 рокоманды А„ за исключением первого дешифратора 4, ключа 16 регистра возврата, ключа 17 константы и дешифра— тора 9. После поступления положительвом выходе первого триггера 10 и выходе второго триггера 11 установятся в состояние "1", а на выходе элемента И-НЕ 15 будет подтвержден потенциал логической единицы (фиг.2),h,ì ин ).

По положительному фронту импульса, сформированного на втором выходе дешифратора 6, поступающего на С-вход третьего триггера 12 последний установится в состояние "0". Тогда на его выходе сформируется потенциал

"0", который поступает на второй управляющий вход регистра 7 возврата (фиг.2о). Этот потенциал запишет в регистр 7 возврата информацию с регистра 8 адреса. Тем самым в указанном регистре запомнится адрес микрокоманды, следующей за микрокомандой перехода (фиг.2.z, о и п ).

По окончанию положительного фронта импульса, сформированного на втором выходе дешифратора 6, поступившевый вход дешифратора 9 и вход элемента НЕ 14. Потенциал "1" с выхода элеляющий вход первого дешифратора 4 и второй вход второго дешифратора 5.

Этот потенциал "1" запрещает работу первого 4 и второго 5 дешифраторов и устанавливает на их выходах "1". Тем самым запрещая всем устройствам выдавать информацию на шину данных и принимать информацию с шины данных (фиг. 2ж, к, н), По отрицательному фронту импульса основной синхросерии СИ 1, поступающего на S-вход третьего триггера 12 и следующего за импульсом основной синхросерии СИ 1, по которому микрокоманда А„ была принята в регистр 3 микрокоманд, третий триггер 12 устанавливается в единичное состояние.

На его выходе появляется единичный потенциал, поступающий на второй вход регистра 7 возврата, и тем самым заканчивается запись с выхода регистра 8 адреса микрокоманд на первый вход данных регистра 7 возврата (фиг.2g,о) .

По положительному фронту этого же импульса, поступающего на С-вход первого триггера 10, он устанавливается в нулевое состояние (фиг.2а,к). Тем

По положительному фронту импульса

1314341

55 ного фронта импульса основной синхросерии СИ 1 (фиг.2)) на третий вход регистра 3 микрокоманд, по которому микрокоманда А„ записывается в регистр 3 микрокоманд и на его втором выходе устанавливается потенциал логической единицы, служащий признаком того, что в микрокоманде содержится информация, передаваемая на шину данных. Потенциал логической единицы с второго выхода регистра 3 микрокоманд поступает на второй вход первого дешифратора 4 и запрещает его работу, т.е. все внешние устройства относительно описываемого и соединенные с шиной данных получают с выхода первого дешифратора 4 потенциалы, запрещающие выдачу информации на ши ну данных.

Потенциал логической единицы с второго выхода регистра 3 микрокоманд поступает на второй вход ключа

17 константы и разрешает передачу информации с его выхода на шину данных (фиг.2 к). Запись информации с шины данных в счетчик 1 адреса микрокоманд осуществляется так же как при выполнении микрокоманды А„(фиг.2 3,7h, ,U, k,n, м и н ). В регистр 7 возврата запишется адрес микрокоманды А,„, в соответствии с временной диаграм-. мой (фиг.2а,S,o и и ). Для того, чтобы обеспечить возврат выполняемой микропрограммы к микрокоманде, хранящейся в блоке 2 памяти по адресу

А „, необходимо обеспечить передачу содержимого регистра 7 возврата через шину данных в счетчик адреса возврата в течение второго цикла исполнения микропрограммы А, т.е. в течение времени между первым импульссом, следующим за импульсом основной синхросерии СИ 1, по которому на регистр 3 микрокоманд была принята микрокоманда А» и вторым импульсом основной синхросерии СИ 1 (фиг.2 с! и

)). Управляющие сигналы для выполнения возврата формирует дешифратор 9.

После этого на третьем выходе регистра 3 микрокоманд появится потенциал логической единицы, служащий признаком того, что исполняемая микрокоманДа перехода с возвратом. С появлением потенциала логического нуля на выходе элемента И-НЕ 15 на втором выходе дешифратора 9 формируется потенциал логического нуля (фиг.2р), который запретит передачу информации с первого выхода. регистра 3 микрокоманды через ключ 17 константы на шину данных. Одновременно этот потенциал поступает на второй вход ключа 16 регистра возврата и разрешает передачу информации на шину данных (фиг.2 к и р).

На первом выходе дешифратора 9 возврата формируется положительный импульс, равный по длительности импульсу дополнительной синхросерии

СИ 2, который поступает на третий вход дешифратора 9 возврата (фиг.2с, а,!! и g ). Импульс с второго выхода дешифратора инверсной полярности поступает на первый вход счетчика l адреса и обеспечивает занесение информации с шины данных (фиг.2t.,и, к и 1 ), т.е. произойдет загрузка содержимого регистра 7 возврата на шину данных.

По положительному фронту второго импульса основной синхросерии СИ 1, поступающего на второй вход счетчика

1 адреса, на второй вход регистра 8 адреса и третий вход регистра 3 микрокоманд, прибавится единица к содержимому счетчика 1 адреса и его содержимое станет-равным А,+ . Старое сом+z держимое указанного счетчика перепишется в регистр 8 адреса, содержимое которого станет равным А „, а в регистр 3 микрокоманд запишется микрокоманда А (фиг.2а, 6; г и g ), В соответствии с принципом работы предлагаемого устройства следующей микрокомандой в регистре 3 микрокоманд будет записана MHKpoKQMBHpG

А, (фиг.2 ). Тем самым нет необходимости ставить после микрокоманды

А микрокоманду возврата к микрокоманде А,„„. формула изобретения

Микропрограммное устройство управления, содержащее счетчик адреса, блок памяти микрокоманд, регистр микрокоманд, с первого по четвертый дешифраторы, регистр возврата, первый и второй триггеры, причем выход блока памяти микрокоманц соединен с информационным входом регистра микрокоманд, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены регистр адреса, третий триггер, элемент И-НЕ, эле7 1314341 8 адреса, выход которого соединен с ин- 5 адресным входом блока памяти микрокоманд, выход поля микроопераций ре- 10

15 формационным входом второго дешифра-20 тора, первый выход которого соединен

25 ным входом третьего дешифратора, тре-45 тий выход второго дешифратора соедимент НЕ, элемент ИЛИ-НЕ, ключ регистра возврата, ключ константы, причем вход кода команды устройства соединен с информационным входом счетчика формационным входом регистра адреса., выход которого соединен с информационным. входом регистра возврата и с гистра микрокоманд соединен с первым выходом микроопераций устройства, выход поля кода источника информации регистра микрокоманд соединен с информационным входом первого дешифратора, выход которого соединен с вторым выходом микроопераций устройства, выход поля кода приемника информации регистра микрокоманд соединен с инс третьим выходом микроопераций устройства, выход поля признака типа микрокоманды регистра микрокоманд соединен с первым стробирующим входом первого дешифратора и первым управляющим входом ключа константы, выход поля константы регистра микрокоманд соединен с информационным входом ключа константы, выход которого соединен с выходом константы устройства, вход условий устройства соединен с первым информационным входом третьего дешифратора, первый выход которого соединен с первым входом элемента ИЛИ-НЕ, выход которого соединен с входом синхронизации счетчика адреса, выход поля кода возврата регистра микрокоманд соединен с первым информационным входом четвертого дешифратора, первый выход которого соединен с вторым входом элемента

ИЛИ-НЕ, второй выход второго дешифратора соединен с вторым информацион30

35 нен с третьим информационным входом третьего дешифратора, четвертый выход второго дешифратора соединен с четвертым информационным входом третьего дешифратора, пятый выход второго дешифратора соединен с пятым информационным входом третьего дешифратора, второй выход которого соединен с входом установки в 1 .первого триггера, прямой выход которого соединен с информационным входом второго триггера, выход которого соединен с первым входом элемента И-НЕ, выход которого соединен с вторым информационным входом четвертого дешифратора, второй выход которого соединен с вторым управляющим входом ключа константы и с управляющим входом ключа регистра возврата, выход которого соединен с выходом адреса возврата устройства, первый вход синхронизации устройства соединен со счетным входом счетчика адреса, с входами синхронизации регистра адреса, регистра микрокоманд, первого и второго триггеров, и с выходом установки в "1" третьего триггера, выход которого соединен с входом синхронизации регистра возврата, выход которого соединен с информационным входом ключа регистра возврата, второй вход синхронизации устройства соединен со стробирующими входами четвертого и третьего дешифраторов, второй выход которого соединен с входом установки в "1" второго триггера, с входом синхронизации третьего триггера и с вторым входом элемента И-НЕ, выход которого соединен с входом элемента .НЕ, выход которого соединен со стро.бирующим входом второго дешифратора и с вторым стробирующим входом первого дешифратора, инверсный выход первого триггера соединен с входом разрешения записи регистра микрокоманд.

1314341

Ъ

«Ю

Составитель A.ÌHõàéëoâ

Техред M.Ходанич

Редактор Ю.Середа

Корректор И.Шулла Заказ 2214/49

Тираж 673 Подписное

ИП1ИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, K-35, Раунская наб., ц. 4/5

Производственно †полиграфическ предприятие, г. Уж, >род, ул. Проектная, 4