Устройство для контроля состояния информационно- измерительной системы

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для оценки качества информационных трактов различных информационно-измерительных систем . Цель изобретения - повьшение достоверности контроля. В устройство, состоящее из генератора 1 тактовых импульсов, элемента И 2, блока 4 памяти , счетчика 6 циклов, первого блока 8 сравнения, элементов И 14 и 12, блока 23 индикации и дешифратора 24, введены блок 3 формирования адреса, триггер 10,цифроаналоговьй преобразователь 7, интегратор 9, анализатор 22 спектра частот, аналого-цифровой преобразователь 15, одновибраторы 5 и 13, компаратор 16, дифференцирующий блок 17, реверсивный счетчик. 19, второй блок сравнения 20, блок 11 задания числа циклов и блок 21 задания допустимой погрешности. Контроль состояния проверяемой информационно-измерительной системы производится периодически перед проведением эксперимента и после эксперимента без перемонтажа каких-либо узлов путем подачи сигнала на вход сброса 25 устройства . 1 з.п. ф-лы, 2 ил. с S (Л со со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (И) (gl) 4 G 06 F 11/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4025466/24-24 (22) 09. 01. 86 (46) 30,05,87. Бюл. 11 20 (72) С.Ф.Бабич, А.В.Васильев, А.А.Зыков и Ю.Г.Кравченко ,(53) 681.3(088.8) (56) Авторское свидетельство СССР

У 744582, кл. G 06 F 11/00, 1978.

Авторское свидетельство СССР

Ф 1141414, кл. G 06 F ll/16, 1983. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СОСТОЯНИЯ ИНФОРМАЦИОННО-ИЗМЕРИТЕЛЬНОЙ

СИСТЕМЫ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для оценки качества информационных трактов различных информационно-измерительных систем. Цель изобретения — повышение достоверности контроля. В устройство, состоящее из генератора 1 тактовых импульсов, элемента И 2, блока 4памяти, счетчика 6 циклов, первого блока

8 сравнения, элементов И 14 и 12, блока 23 индикации и дешифратора 24, введены блок 3 формирования адреса, триггер 10, цифроаналоговый преобразователь 7, интегратор 9, анализатор

22 спектра частот, аналого-цифровой преобразователь 15, одновибраторы 5 и 13, компаратор 16 дифференцирующий блок 17, реверсивный счетчик 19, второй блок сравнения 20, блок 11 задания числа циклов и блок 21 задания допустимой погрешности. Контроль состояния проверяемой информационно-измерительной системы производится периодически перед проведением эксперимента и после эксперимента без перемонтажа каких-либо узлов путем подачи сигнала на вход сброса 25 устройства. 1 з. п. ф-лы, 2 нл.

l 3! 4342

Изобретение относится к автоматике и вычислительной технике и может быть использовано для оценки качества информационных трактов различных информационно-измерительных систем.

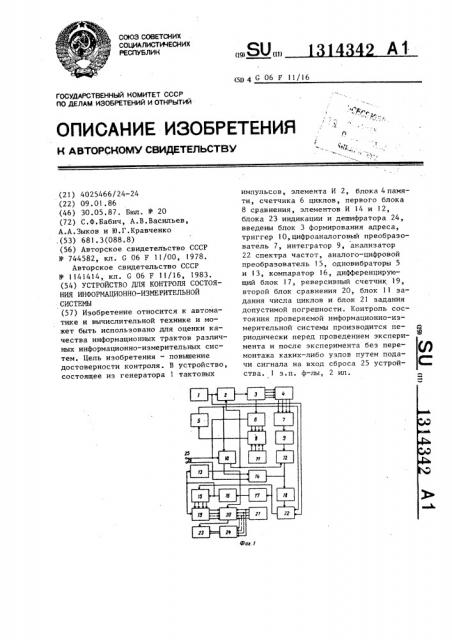

Целью изобретения является повышение достоверности контроля, Па фиг.! представлена структурная схема предлагаемого устройства; на фиг.2 — схема анализатора спектра частот.

Устройство содержит генератор 1 тактовых импульсов, первый элемент

И 2, блок 3 формирования адреса, блок 4 памяти, второй одновибратор 5, счетчик 6 циклов, цифроаналоговый преобразователь 7, первый блок 8 сравнения, интегратор 9, триггер 10, блок 11 задания числа циклов, второй элемент И 12, первый одновибратор 13. третий элемент И 14, аналого-цифровой преобразователь 15, компаратор

16, дифференцирующий блок 17, проверяемую систему 18,. реверсивный счетчик 19, второй блок 20 сравнения, блок 21 задания допустимой погрешности, анализатор 22 спектра частот, блок 23 индикации, дешифратор 24, вход 25 сброса устройства, информационный вход 26 устройства.

Анализатор 22 спектра частот содержит блок 27 фильтрации, триггер

28, элемент И 29, шифратор 30, блок

3l усреднения, коммутатор .32.

Устройство работает следующим образом.

С помощью входа 25 сброса устройство приводится в исходное состояние, соответственно счетчик 6 циклов обнуляется, а триггер 10 устанавливается в состояние, при котором на первом выходе присутствует логическая единица, а на втором — нуль. Это соответствует режиму "Проверка". При этом напряжение с второго выхода триггера

10, соответствующее "0", подается на управляющий вход элемента И 14, который отключает вход проверяемой системы от информационного входа устройства. Одновременно напряжение с первого выхода триггера 10, соответствующее

1, подается.на второй вход элемента И 12 и второй вход элемента И 2, который начинает пропускать тактовые импульсы с генератора 1 тактовых импульсов на вход блока 3 формирования адреса. При этом элемент И 12 подклю5 !

О !

55 чает выход интегратора 9 к входу проверяемой системы 18

В свою очередь блок 3 формирования адреса последовательно формирует, начиная с нулевого, все адреса блока

4 памяти, в которые занесена информация о принятой сигнатуре, обеспечивающей проверку работоспособности информационного тракта по всему частотному диапазону. Это должно быть произведено при получении одной оценки частотного спектра с помощью анализатора 22 спектра частот. Считываемые таким образом из блока 4 памяти числовые значения в двоичном коде подаются на входы цифроаналогового преобразователя 7, на выходе которого получаем амплитудные значения эталонного сигнала, которые подаются для усреднения на интегратор 9. С выхода интегратора 9 аналоговый сигнал подается на первый вход элемента И 12, Импульсы с второго выхода блока 3 формирования адреса подаются на первый вход счетчика 6 циклов, в качестве которого можно использовать, например, серийно изготавливаемую интегральную микросхему К155ИЕ7. Тактовые импульсы подаются на вход блока

3 формирования адреса, который последовательно формирует следующие кодовые группы, начиная с .00000000 и до 11111111 (в качестве. примера приводится двоичный восьмиразрядный счетчик).

Указанное изменение состояния блока 3 формирования адреса соответствует одному циклу, количество которых N обычно задается, исходя из практических требований к точности спектрального анализа и времени проведения контроля достоверности данных, передаваемых через информационный тракт проверяемой системы 18.

При совпадении параллельньгх кодов, один из которых соответствует числу

N, а второй считывается со счетчика

6 циклов, первый блок 8 сравнения выдает импульс. Этот сигнал с выхода первого блока сравнения подается на вход одновибратора 5, где он формируется и задерживается на время, необходимое на анализ полученных результатов и принятие решения о нормальном состоянии проверяемой информационно-измерительной системы 18.

Импульс с выхода одновибратора 5 подается на единичный вход триггера

1314342

10, который перебрасывается при наличии импульса на выходе одновибратора

5. К прямому выходу триггера 10 параллельно подсоединень! второй вход элемента И 2 и второй вход элемента

И 12, который в открытом состоянии пропускает заданную сигнатуру на вход проверяемой системы 18, Триггер

1О управляет также работой элемента

И 14, который подключает к входу про- 10 веряемой системы 18 информационный вход устройства 26 (режим работы устройства "Работа" ). В режиме "Проверка информационный вход устройства

26 отключается и к входу проверяемой системы 18 подсоединяется выход интегратора 9. Сигнатура, прошедшая информационный тракт проверяемой системы 18, подается на первый вход анали20 затора 22 спектра частот, частотный спектр с выхода которого является оценкой спектра периодического сигнала и, соответственно, имеет явно выраженные модальные составляющие, величины которых равны шкале сигнала (для сигнатуры на входе проверяемой

25 системы 18). В зависимости от состояния информационного тракта и отдельных узлов проверяемой системы амплитудное значение различных составляющих меняется. Оценка степени изменения частотного спектра на выходе проверяемой системы 18 производится

30 путем сравнения. получаемых значений

coставляющих частотного спектра с эталонными. Затем величину получен35 ной разности сопоставляют с допустимым порогом изменений и делается автоматизированный вывод о пригодности проверяемой системы 18 к дальнейшей работе.

40 составляющих, находящихся в начале и конце рабочего диапазона частот исследуемой системы.

Выходной сигнал с анализатора 22 спектра частот подается на вход дифференцирующего блока 17 и информационный вход аналого-цифрового преобразователя 15.

Так как производится сквозная проверка информационного тракта проверяемой системы, то создается такая

45 структура сигнатуры, которая характеризуется линейчатым частотным спектром, наиболее простым вариантом является, например, сигнатура, частотный спектр которой состоит из двух равных50

Дифференцирующий блок 17 состоит из операционного усилителя, в цепи обратной связи которого стоит дифференцирующая цепочка RC. С помощью дифференцирующего блока 17 выделяются максимальные значения откликов, получаемых с выхода анализатора 22 спектра частот.

Сигналы с выхода дифференцирующего блока 17 подаются на вход компаратора 16, состоящего, например, из делителя напряжения, который может быть использован в качестве источника опорного напряжения, и микросхемы

52lCA2, первый вход которой подсоединен к входу компаратора 16, а второй вход микросхемы — к выходу источника опорного напряжения. Сформированные компаратором 16 синхроимпульсы одновременно подаются на вход одновибратора 13, второй вход счетчика 19 и второй вход аналого-цифрового преобразователя 15, в который подаются с выхода компаратора 16 импульсы синхронизации, благодаря импульсам синхронизации преобразование осуществляется в моменты досчижения откликами фильтров анализатора 22 спектра частот максимальных значений. Импульсы с выхода компаратора 16 параллельно подаются также на вход одновибратора 13 и на второй вход счетчика 19, в качестве которого можно использовать интегральную микросхему 155ИЕ7, первые входы которой подсоединены параллельно к второму входу счетчика

19, а вторые входы микросхемы 155ИЕ7 являются первыми входами счетчика 19, выходы микросхемы 155ИЕ7 являются выходами счетчика 19.

Таким образом, во все разряды реверсивного счетчика 19 одновременно записываются единицы. Затем с выхода аналого-цифрового преобразователя 15 на входы реверсивного счетчика подается текущее значение кода, соответствующее отклику с фильтра анализатора 22 спектра частот.

Таким образом, в реверсивном счетчике оказывается разность, которая с выходов реверсивного счетчика подается на.первую группу входов второго блока 20 сравнения. Соответственно, вторая группа входов второго блока 20 сравнения подсоединена к группе выходов блока 21 задания допустимой погрешности.

1314342

25

35

50

Сигнал с выхода первого блока 8 сравнения, задержанный и сформированный одновибратором 5 на время, необходимое для анализа и индикации результатов проверки информационного тракта исследуемой системы 18, подается на единичный вход триггера 10.

В результате триггер 10 перебрасывается и закрывает элемент И 12, а элемент И 14 открывается и соединяет информационный вход устройства 26 с входом проверяемой системы 18, и таким образом система переходит в режим "Работа".

Формула изобретения

1. Устройство для контроля состояния информационно-измерительной системы, содержащее генератор тактовых импульсов, три элемента И, блок памяти, счетчик циклов, первый блок сравнения, дешифратор, причем выход генератора тактовых импульсов подключен к первому входу первого элемента И, вход сброса счетчика циклов соединен с входом сброса устройства, выход дешифратора является выходом результата контроля устройства, группа разрядных выходов счетчика циклов соедииена с первой группой входов первого блока сравнения, о т л и ч а ю щ е ес я тем, что, с целью повышения достоверности контроля, в устройство введены блок формирования адреса, первый и второй одновибраторы, цифроаналоговый преобразователь, интегратор, триггер, блок задания числа циклов, аналого-цифровой преобразователь, компаратор, дифференцирующий блок, реверсивный счетчик, второй блок сравнения, блок задания допустимой погрешности, анализатор спектра частот, причем выход первого элемента И подключен к входу разрешения блока формирования адреса, группа выходов которого соединена с группои адресных входов блока памяти, группа информационных выходов которого соединена с группой входов цифроаналогового преобразователя, выход которого через интегратор подключен к первому.входу второго элемента И, второй вход которого объединен с вторым входом первого элемента И и подключен к прямому выходу триггера, инверсный выход которого соединен с первым входом третьего элемента И, первая и 10

15 вторая группы информационных входов и вход разрешения второго блока сравнения подключены соответственно к группам выходов реверсивного счетчика и блока задания допустимой погрешности и выходу первого одновибратора, информационные входы второй группы второго блока сравнения объединены с соответствующими входами дешифратора„группа выходов аналого-цифрового преобразователя подключена к группе информационных входов реверсивного счетчика, вычитающий вход которого объединен с входом первого одновибратора и входом разрешения аналого-цифрового преобразователя и подключен к выходу компаратора, вход которого соединен с выходом дифференцирующего блока, вход которого объединен с информационным входом аналого-цифрового преобразователя и подключен к выходу анализатора спектра частот, информационный вход которого является первым информационным входом устрдйства для подключения к проверяемой системе, вход запуска и тактовый вход анализатора спектра частот соединены соответственно с выходом второго одновибратора и выходом генератора тактовых импульсов, вторая группа входов и выход равенства первого блока сравнения соединены соответственно с группой выходов блока задания числа циклов и входом второго одновибратора, второй вход третьего элемента И соединен .с вторым информационным входом устройства, выходы второго и третьего элементов И объединены и являются информационным выходом устройства для подключения к входу проверяемой системы, нулевой и единичный входы триггера подключены соответственно к. входу сброса устройства и выходу второго одновибратора, выход равенства второго блока сравнения является выходом признака выхода за пределы допустимой погрешности устройства.

2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что анализатор спектра частот содержит блок фильтрации, триггер, элемент И, шифратор, блок усреднения и коммутатор, причем вход блока фильтрации, счетный вход триггера и первый вход элемента И являются соответственно информационным входом, входом запуска и тактовым входом анализатора, группа выходов блока фи. ьтрации соединена с

1314342 ра. фиг. 2

Составитель И.Сафронова

Техред М.Ходанич Корректор И.Шулла

Редактор 1О.Середа

Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 2214/49

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 группой входов шифратора, группа выходов которого подключена к группе входов блока усреднения, группа выходов которого подключена к группе информационных входов коммутатора, управляющий вход которого соединен с выходом элемента И, второй вход которого соединен с выходом триггера, вход сброса которого соединен с выходом коммутатора, выход .которого является выходом анализатор