Цифровой нерекурсивный фильтр нечетного порядка

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике . Цель изобретения - повьшение быстродействия. Устр-во содержит два коммутатора 1 и 2, два регистра сдвига (PC) 3 и 4, сумматор 5, два . накапливающих сумматора 6 и 7, два умножителя 8 и 9, блок памяти 10 приращений коэффициентов, блок памяти 11 знаков коэффициентов и блок синхронизации (БС) 12. Для формирования каждого выходного отсчета в устр-ве осуществляются следующие операции: суммирование симметрично расположенных выборок входных сигналов, формирование произведения полученных сумм на знаки соответствующих коэффициентов , из которых затем формируют частичные суммы входных выборок, умножение их на соответствующие приращения коэффициентов и сложение результатов между собой. Цель достигается введением коммутатора 2, PC 4 и сумматора 5. Дана схема БС 12. 2 ид. 1 табл. СЛ 8ьао, : 4 4 СЛ

C0IO3 СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

А1 (19) (11) (50 4 Н 03 Н 17 06

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 3977438/24-09 (22) 18. 11.85 (46) 30.05.87. Бюл. № 20 (72) С.Л. Титов (53) 621.32(088.8) (56) Авторское свидетельство СССР № 942247, кл. Н 03 Н 17/06, 1982.

Авторское свидетельство СССР

¹ 1124430, кл. Н 03 Н 17/06, 1984. (54) ЦИФРОВОЙ НЕРЕКУРСИВНЫЙ ФИЛЬТР

НЕЧЕТНОГО ПОРЯДКА (57) Изобретение относится к радиотехнике. Цель изобретения — повышение быстродействия. Устр-во содержит два коммутатора 1 и 2, два регистра сдвига (РС) 3 и 4, сумматор 5, два накапливающих сумматора 6 и 7, два умножителя 8 и 9, блок памяти 10 приращений коэффициентов, блок памя- ти 11 знаков коэффициентов и блок синхронизации (БС) 12. Для формирования каждого выходного отсчета в устр-ве осуществляются следующие операции: суммирование симметрично расположенных выборок входных сигналов, формирование произведения полученных сумм на знаки соответствующих коэффициентов, иэ которых затем формируют частичные суммы входных выборок, умножение их на соответствующие приращения коэффициентов и сложение результатов между собой. Цель достигается введением коммутатора 2, PC 4 и сумматора 5. Дана схема БС 12. 2 ил.

1 табл.

1 13144

Изобретение относится к радиотехнике и может быть использовано в сис темах цифровой обработки сигналов.

Цель изобретения — повышение быстродействия. 5

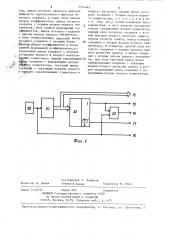

На фиг. 1 представлена структурная электрическая схема цифрового нере-, курсивного фильтра нечетного порядка; на фиг. 2 — схема блока синхронизации.

Пифровой нерекурсивный фильтр нечетного порядка (фиг. 1) содержит первый и второй коммутаторы 1 и 2, первый и второй регистры 3 и 4 сдвига, сумматор 5, первый и второй на— капливающие сумматоры 6 и 7, второй умножитель 8, первый умножитель 9, блок 10 памяти приращений коэффициентов, блок 11 памяти знаков коэффициентов, блок 12 синхронизации, адресный выход 13 блока синхронизации,установочный выход 14 блока синхронизации, первый управляющий выход 15 блока синхронизации, тактовый выход 16 блока синхронизации, второй управляющий выход 17 блока синхронизации, вход 18 и выход 19 цифрового нерекурсивного фильтра нечетного порядка..

45 2

Блок 12 синхронизации (фиг. 2) содержит генератор 20 тактовых импульсов, счетчик 21, дешифратор 22, элемент И 23, Цифровой нерекурсивный фильтр нечетного порядка работает следующим образом.

I

Рассмотрим алгоритм его работы, который получим на основе алгоритма свертки:

Учитывая, что коэффициенты фильтрации нерекурсивных фильтров, как правило, симметричны, то (1) можно преобразовать для фильтра нечетного к виду (м+1)!7-1

У„=rа; (Х,— Х„;). (2) =о

Выражение (2) можно преобразовать путем замены весовых коэффициентов а, их приращениями g а; = а; — а;,, где 6 а, = a» и их знаками sign(a;): л aaosign(ag) (X + Х м)+(Ьа,+ca, ) sign(a,) (Х„+ y„)+

° + о а + а, + ° ° ° + а(,0,)sigп(а< „,,1 )(Х„< +Х„> ) = (М ф-1

=; а sign(a ) (Х „„. +Х„, .) (3)

j=o

Из выражения (3) видно, что для числения в правой (выходной) ячейке формирования каждого выходного отсче- 3 памяти первого регистра 3 сдвига та необходимо просуммировать симмет- хранится значение п-(М+1)/2-1-ro рично расположенные выборки входных входного отсчета, а н каждой ячейке сигналов, сформировать произведения ленее — значения отсчетов с номераполученных сумм на знаки соотнетст- ми на единицу меньше. В то же время вующих коэффициентов, из которых за- 40 в правой ячейке памяти второго реги- тем сформировать (M+1)/2 частичных стра 4 сдвига записано значение сумм входных выборок, умножить их и-(М+1)/2-го входного отсчета, а в на соответствующие приращения коэф- каждой ячейке левее — значения отсчефициентов и результаты сложить между тов с номерами на единицу больше. Пособой, причем формирование сумм сим- 45 этому в первом такте вычисления в метрично расположенных входных выбо- первый накапливающий сумматор 6 черок необходимо начинать с суммы рез первый умножитель 9 на +1 и суми-(М+1)/2 — 1 и и-(М+1)/2 отсчетов, а матор 5 с выходов первого и второго заканчивать суммой и и и-М отсчетов. регистрон 3 и 4 сдвига поступает проУказанный алгоритм реализуется 50 изведение суммы и†(М+1)/2 — 1-го и следующим образом. п-(М+1)/2-го входных отсчетов, умноВ начале каждого цикла вычисления женной на знак (М+1)/2-1-го коэффисигнал, поступающий с установочного циента. ныхода 14 блока 12 синхронизации, Одновременно с этим сигнал, поступроизводит обнуление первого и второ- 5 лающий с первого управляющего выхода го накапливающих сумматоров 6 и 7, 15 блока 12 синхронизации, переклюЗапись в первый и второй регистры 3 чает первый коммутатор 1 в режим коми 4 сдвига организована таким обра- мутации сигнала с входа 18 и на вход зом, что в начале каждого цикла вы- первого регистра 3 сдвига поступает

1314445

Продолжение таблицы

Цикл

Такт

Р второго (4) первого (3) II! 2 3

1 2 3 4 5 значение текущего входного сигнала

Х„. На управляющий вход второго коммутатора 2 с второго управляющего выхода 17 блока 12 синхронизации начинает поступать сигнал, который удерживает второй коммутатор 2 в режиме коммутации сигнала с выхода второго регистра 4 сдвига вплоть до начала последнего такта вычисления. Поэтому в конце первого такта вычисления в 10 первую ячейку второго регистра 4 сдвига no сигналу с тактового выхода 16 блока 12 синхронизации записывается значение и-(М+1)/2-го входного отсчета, а в первую ячейку первого регист- 15 ра 3 сдвига — значение текущего входного отсчета Х . При этом значение

n и-(M+1) /2-1-го отсчета из первого регистра 3 сдвига выводится.

Начиная с начала второго такта вы-20 числения и до конца последнего такта вычисления, сигнал, поступающий с первого управляющего выхода 15 блока

12 синхронизации на управляющий вход первого коммутатора 1, удерживает 25 его в режиме коммутации сигнала с выхода первого-регистра 3 сдвига.Поэтому в течение (M+1)/2 тактов вычисления данные с выходов первого и второго регистров 3 и 4 сдвига цикличес- 30 ки переписываются в свои первые ячейки. В последнем такте вычисления сигнал, поступающий с второго управляющего выхода 17 блока 12 синхронизации, переводит второй коммутатор 2 в режим коммутации сигнала с выхода (M-1)/2-1-й ячейки памяти первого регистра 3 сдвига. Вследствие этого в конце последнего такта вычисления в первую ячейку второго регистра 4 сдвига записывается значение и-(M+1))

/2-1-ro входного отсчета, а.п-M-й отсчет из второго регистра 4 сдвига выводится °

В таблице приведено расположение 45 входных n-i-х отсчетов в каждом из тактов n-ro цикла вь|числения в регистрах 3 и 4 сдвига для фильтра седьмого порядка (приведено значение i).

Ячейки регистров сдвига

2 0 1 2 4 3 7 б 5

3 2 0 1 5 4 3 7 6

4 1 2 0 6 5 4 3 7

+1 1 0 1 2 2 6 5 4 3

В течение (M+1)/2 тактов каждого цикла вычисления на выходе первого накапливаюшего сумматора 6 последовательно формируются частичные суммы: (мм) (х-1

sign(a ) (Х„„+ Х„м+,,);

1 (мб1) 1-1 (м ф 2-1

sign(a;)(Х„;+ Х„° );

i=(м+ ф-z (МИ)(2 -1

sign(a; ) (Х „; + Х„„) у

„ «о которые во втором умножителе 8 умножаются на малоразрядные приращения коэффициентов 5 3(„) (g а „ ..., Ьа, поступающие из блока 10 памяти приращений коэффициентов синхронно с частичными суммами с выхода первого накапливающего сумматора 6.

Вычисляемые произведения в течение (И+1)/2 тактов вычисления суммируются во втором накапливающем сумматоре 7, где в конце последнего (И+1)/2 такта каждого цикла вычисле- . ния формируется очередной отсчет выходного сигнала Y поступающий на выход 19. С приходам следующего входного отсчета Х „ „ цикл вычисления повторяется.

Формула и з обре т е н и я

Такт

Цикл

)Ж второго (4) первого (3) 1 2 3

Ячейки регистров сдвига 50

1 2 3 4 555

4 2 3 1 7 6 5 4 8

1 1 2 3 3 7 6 5 4

Цифровой нерекурсивный фильтр нечетного порядка, содержащий последовательно соединенные первый коммутатор, первый вход которого является входом цифрового нерекурсивного фильтра нечетного порядка, и первый регистр сдвига, последовательно соединенные первый умножитель, первый накапливающий сумматор, второй умножитель и второй накапливающий сумма1314445

Составитель Э. Борисов

Техред Е.Кадар

Корректор М. Пожо

Редактор М. Дылын

Заказ 2219/55 Тираж 902 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 тор, выход которого является выходом, цифрового нерекурсивного фильтра не четного порядка, а также блок памяти знаков коэффициентов, выход которого соединен с первым входом первого умножителя, блок памяти приращений коэффициентов, выход которого соединен с другим входом второго умножителя> и блок синхронизации, адресный выход ..которего соединен с входами блока

° 3

,памяти :зйаков коэффициентов и блока

- Г " памятй .приращений коэффициентов,установочный выход соединен с входами установки первого и второго накаплиk вающих сумматоров, первый управляющий в ер соединен с управляющим входом тйирЬоуо коммутатора, тактовый выход соедйнеН с тактовыми входами первого ! и вторфо накапливающих сумматоров и » первого регистра, первый выход которого соединен с вторым входом первого коммутатора, о т л и ч а ю щ и и с я тем, что,с целью повышения быстродействия, в него введены последовательно соединенные второй коммутатор, первый вход которого соединен с вторым выходом первого регистра сдвига, второй регистр сдвига, выход которого

10 соединен с вторым входом второго коммутатора, и сумматор, другой вход которого соединен с первым выходом первого регистра сдвига, а выход соединен с вторым входом первого умножите15 ля, при этом тактовый выход блока синхронизации соединен с тактовым входом второго регистра сдвига а вто— рой управляющий выход соединен с уп— равляющим входом второго коммутатора .