Устройство синхронизации

Иллюстрации

Показать всеРеферат

Изобретение относится к технике дискретной информации. Цель изобретения - повышение устойчивости синхронизации. Устр-во содержит четыре смесителя 1-4, два блока фазовой автоподстройки частоты 5 и 6, два делителя 7 и В частоты, умножитель 9 частоты,сумматор 10, два полосовых фильтра 11 и 12 и три эл-та задержки 13, 14 и 15. Цель достигается введением смесителей 3 и 4, устраняющих срыв синхронизации , сумматора 10, выходной сигнал которого содержит все частотные составляющие , имеющиеся во входных сигналах , полосового фильтра 12, выделяющего разностную частоту, и эл-тов задержки 13, 14 и 15, каждый из которых осуществляет задержку сигнала на период Т тактовой частоты. 2 ил. (Л 00 s 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (1D

СЮ 4 H 04 L 7 02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Фиг. 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3919522/24-09 (22) 27. 06. 85 (46) 30.05,87.Бюл. Ф 20 (71) Таллинский политехнический институт (72) И.О.Арро, О.Э.Кангур и Л.Э,Смолянский (53) 621,394.662.2 (088.8) (56) Патент США 1(3743775, кл. Н 04 Ь 7/02, 1973.

1 (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ (57) Изобретение относится к технике дискретной информации. Цель изобретения — повьппение устойчивости синхронизации, Устр-во содержит четыре смесителя 1-4, два блока фазовой автоподстройки частоты 5 и 6, два делителя 7 и 8 частоты, умножитель 9 частоты, сумматор 1О, два полосовых фильтра 11 и

12 и три эл-та задержки 13, 14 и 15.

Цель достигается введением смесителей 3 и 4, устраняющих срыв синхронизации, сумматора 10 выходной сигнал которого содержит все частотные составляющие, имеющиеся во входных сигналах, полосового фильтра 12, выделяющего раэностную частоту, и эл-тов задержки 13, 14 и 15, каждый иэ которых осуществляет задержку сигнала на период Т тактовой частоты. 2 ил, ! 3! 4473

ВРеMR 1

Т вЂ” длительность тактового интервала; (д, — средняя угловая частота сигнала;

А — амплитуда; л 1

x„= х„, + (UÄ, - V) - — начальная фаза постоянная в течение k-го у! () = у<> (") у (t T) ° я Uê

S(t) = A sin (u t + — — - t + x )

2Т

В зависимости от того, какими являются соседние информационные символы, сигнал у, (t) содержит разные частотные составляющие, Возможны три случая (фиг.2в):

1ст ы t (k+1)T, где (Я= +1- последовательность информационных символов;

k — целые числа;

U« (t) содержит частоты 2 (д и — ;— ! О Т 1

-П! П!,, -1 у, () содержит частоту 2 (ц — — — ) °

2Т с

1 у, (t) содержит частоту 2(у + —,— ) ..

Блоки ФАПЧ 5 и 6 настроены соот- нить который позволяет введение ветстненно на удвоенную несущую час- смесителей 3 и 4. тоту (2 р ) и половинную тактовую Выходной сигнал блока ФАПЧ 5 у (t)

5 содержит только одну частотную сосчастоту (" †). На фиг. 2в выходной тавляющую — 2Q,. Этот сигнал подается на второй вход смесителя 3 с за— сигнал смесителя 1, поступающий на держкой на время Т, а также на вход входы блоков ФАПЧ 5 и 6 через сумма- делителя 7 частоты, Выходной сигнал тор 10, содержит зти частотные сос- смесителя 3 содержит суммарные и тавляю е щи только в случае. U -Пк-i разностные частотные составляющие

Поэтому в случае 11 = П!,, мог бы сигналов у1 (t) и у (с-Т). Возможны произойти срыв синхронизации, устра- три случая (фиг.2ж): при U> = -U„- у (t) содержит частоты 4с2 2(и + — — ) 2(У )

5 os о 2Т р

1I

11 при Ц„= U = -1 — У (t) содеРжит частоты 2 (2И вЂ” — -) и ——

К-1 о 2Т Т ю Г

И II при П„= и„= 1 — у (t) содержит частоты 2 (2 7 + — --) и — °

Ъ 2Т Т

Изобретение относится к технике передачи дискретной информации и предназначено для синхронизации в системах синхронной связи с минимальной частотной манипуляцией. 5

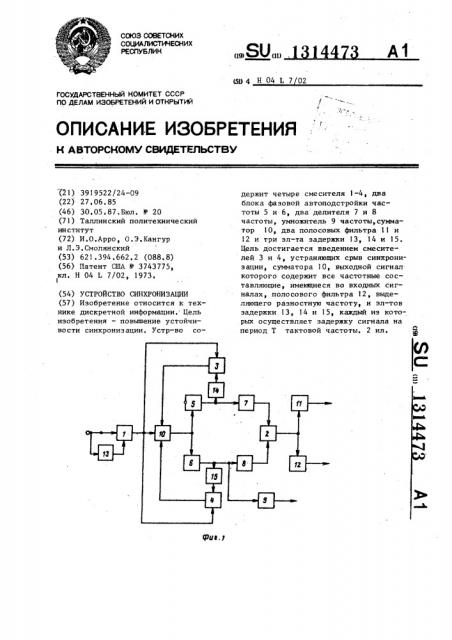

Целью изобретения янляется повышение устойчивости синхронизации, На фиг. 1 представлена схема устройства синхронизации; на фиг. 2 график образования дискретных спектральных составляющих н различных точ. ках схемы.

Устройство синхронизации содержит первый, второй, третий и четверf5 тый смесители 1 — 4, первый и второй блоки ФАПЧ 5 и 6, первый и второй делители 7 и 8 частоты, умножитель

9 частоты, сумматор 10, первый и вто рой полосовые фильтры 11 и 12, первый, второй и третий элементы задержки на Т 13, 14 и 15.

Устройство работает следующим образом.

Сигнал с минимальной частотной манипуляцией нида тактового интервала, при (k-1)T

II мгновенной частотой (д + ---- при

2Т

U„= +1 (фиг.2 а, б), подается на входы смесителя 1, по одному из которых введена задержка на длительность тактоного интервала Т. На выходе смесителя 1 сигнал равен

1314473

11 держит только частоту — — — . Таким

Т образом, у (t) содержит следующие частотные составляющие (фиг,2з):

i к 2 Г

----) 2 (Q )

27 ° 0 27 7 при У„= -П, — 2(яо+ при U = U = -1 — 2<) и 2((й — — -- )

К-1 о 0 т

1

П при U» U„ i 2 оH 2(u0+

Сигналы y (t) у (t) и у (t) сум- 15 ные составляющие, которые мируются в сумматоре 10 и его выход- ются во входных сигналах, ной сигнал у (t) содержит все частот- но (фиг.2г}: имеа именпри U -U», — частотные составляющие

2i

4и у о к

Н il

2(сд - — --) 2(д + — — )

° о 27 . 27

И

26)

ol т при U U, = -1 — частотные составляющие

3" И Ч

2g — — 2 (и — — --.) 2 (2у — ---) 2 ((,) — — - )

Т к о 27 к 2т т при U U, = 1 — частотные составляющие

И И !! я

2u — — 2(u + — — ) 2(2и + — --) 2(ц + ) е оэ 7 в о 27 о 27 о 7

Аналогично образуются частотные составляющие выходного сигнала y4(t) смесителя 4, Выходной сигнал у, () блока ФАПЧ 6 на любом интервале со—

Выходной сигнал сумматора 10 у (t)

2 содержит составляющие с частотами

Ii

2 ы и ---, на которые настроены со-35 ответствующие блоки ФАПЧ 5 и 6, йеза- висимо от последовательности информационных символов U Òàêèì образом обеспечивается устойчивая синхрониза-4О ция при сколь угодно длинной последовательности одинаковых символов, Захват синхронизации после подачи сигнала уо(t) на вход устройства происходит после первой смены символа Б (фиг ° 2 дк е) °

В делителях 7 и 8 частоты происходит деление частот входных сигналов на два. После этого на выходе делителя 7 всегда имеется сигнал с часто- 50 той »к3, а на выходе делителя 8—

1( сигнал с частотой ††. Эти сигналы

2Т поступают на входы смесителя 2, выходной сигнал которого содержит сум- 55 марную частоту сэ, + -- — и разност2Т ную частоту И вЂ” — —. Эти частоты

2Т выделяются соответствующими фильтрами 11 и 12. В умножителе 9 частоты происходит умножение частоты ыа два.

Следовательно, на его выходе сигнал

2 Г имеет частоту -- —.

Т

Таким образом, независимо от последовательности мгновенных частот во входном сигнале у (t), устройство о устойчиво выделяет три частоты: так-!

2о товую частоту — — — на выходе умноT li жителя 9 частоты частоту u + —— к е соответствующую U 1, на выходе полосового фильтра 11; частоту о — c0oTseT T óêéióþ Uê

= -1, на выходе полосового фильтра 12.

Наилучший режим работы блоков

ФАПЧ 5 и 6 обеспечивается при постоянстве амплитуд составляющих с, II частотами 2 И и — — — соответствено

Т но, на их входах. Это достигается выбором коэффициентов передачи по

1314473

А@

А»

1(Ц т -! (/ !)т 1 (к.г)т р.зт -! (/!.//)т fg«5)T -1 (ge())f 1(.т)т

à — Т вЂ” Г—

Т вЂ” !-,!

) м-Х/г«| - X/Í

Т /) -М7гг ., ° гйо

-Я/2/

+ !я/г у фр- ,Ж -.Х/2ф)

/-. «л //

2(/ь «худ аь!2я1;

Щ. рЯ,"2((ь-м/гф

2(Ьо «.УЩ гйЬ «Х/2«! сч ь гм/т аь!2ж/ 2

Фио -Х7 2(/////- /

2@Ь Х/гт/ Щ/р«Х2 I2 — +! у (е) 1

Ул(E х/т х/т х/т; 1 ь - Фрфй p г(а ++ +x r ймлЩ(21ц ster) г(ь л л)(г(щ, Х4фг/ь4, )l ю ая/rï а/r zr/г; Т м

2//о, 2(а -Лф 1;llf< фРЩ гйф NW 2йК фщ-х (Qx «/««/ ) w lEge/Ре-«/

Ри8 ф

ВНИИПИ Заказ 2221/56 Тираж 639 Подписное

Произв.-полигр. пр-тне, r. Ужгород, ул. Проектная, 4 входам сумматора 10, Амплитуды будут постоянны, если где k — коэффициент передачи сумматора 10 по входу, соединенному с выходом смесителя 1;

k> " коэффициент передачи сумматора 10 по входу, соединенному с выходом смесителя 3;k — коэффициент передачи сумматора 10 по вхоДу,- соединенному с выходом смесителя 4;

А — амплитуда сигнала на выходе блока ФАПЧ 5;

А — амплитуда сигнала на выхо6 де блока ФАПЧ 6, Формула изобретения

Устройство синхронизации, содержащее первый смеситель, первый и .второй блоки ФАПЧ, выходы которых через соответствующие первый и второй делители частоты подключены соответственно к первому и второму входам второго смесителя, выход которого подключен к входу первого полосового фильтра, умножитель частоты, выход которого является первым выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения устойчивости синхронизации, в него введены третий и четвертый смеситали, второй полосовой фильтр,первый, второй и третий элементы задержки на Т, где Т вЂ” период тактовой частоты, и сумматор, первый вход которого подключен к выходу первого смесителя и соединен с первыми входами третьего и четвертого смесителей,выходы которых подключены соответственно к второму и третьему входам сумматора, выход которого подключен к входам первого и второго блоков ФАПЧ, выходы которых через второй и третий элементы задержки на Т соединены соответственно с вторыми входами третьего и четвертого смеси20 телей, выход BToporo блока ФАПЧ соединен с входом умножителя, а выход второго смесителя соединен с вторым полосовым фильтром, вход устройства подключен к одному входу первого

25 смесителя и через первый элемент за. держки на Т вЂ” к другому входу первого смесителя, а выходы первого и второго полосовых фильтров являются соответственно вторым и третьим выходаЗ0 ми устройства.