Фильтр токов обратной последовательности

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике , а именно к релейной защите. Цель изобретения - снижение погрешности вьщеления токов обратной последовательности в широком диапазоне частот. Это достигается за счет того , что выходные сигналы блока дифференцирования и интегратора преобразуются при помощи аналого-цифровых преобразователей 9 и 10 в числовые эквиваленты, из которых производится цифровой набор максимумов блоками 11 и 12. Деление осуществляет двоичный делитель 13. Код частного преобразуется цифроаналоговым преобразователем 14 в напряжение, которое не зависит от частоты входных сигналов. 2 ил. (Л 11 - 73 74 JO 12 tpue.Z

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 ф з

I

)y

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

M А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3876486/24-07 ll (22) 03. 04. 85 (46) 15.06.87. Бюл. Ф 22 (72) Г.Е. Иванов, В.И. Нагай, М.А. Полторацкий и Д.Е. Синельников (53) 621.316.925(088.8) (56) Авторское свидетельство СССР

1! 898552, кл. Н 02 Н 3/26, 1980.

Авторское свидетельство СССР

9 643813, кл. G 01 R 29/16, 1976.

Атабаков Г.И. Теоретические основы релейной защиты высоковольтных сетей. M. ГЭИ, 1957, с. 99, рис. 4 — 15. (5ц 4 G 01 R 29/16 Н 02 Н 3/26 (54) ФИЛЬТР ТОКОВ ОБРАТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ (57) Изобретение относится к электротехнике, а именно к релейной. защите.

Цель изобретения — снижение погрешности выделения токов обратной последовательности в широком диапазоне частот. Это достигается за счет того, что выходные сигналы блока дифференцирования и интегратора преобразуются при помощи аналого-цифровых преобразователей 9 и !О в числовые эквиваленты, из которых производится цифровой набор максимумов блоками

11 и 12, Деление осуществляет двоичный делитель 13. Код частного преобразуется цифроаналоговым преобразователем 14 в напряжение, которое не зависит от частоты входных сигналов.

2 ил.

1 1317373

Изобретение относится к электротехнике, а именно к релейной защите энергетических систем, и может быть использовано в качестве фильтров симметричных составляющих обратной последовательности.

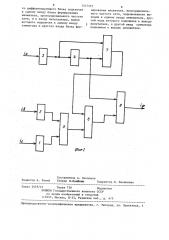

Цель изобретения — снижение погрешности выделения токов обратной последовательности в широком диапазоне частот. !О ствляться, например, в соответствии со схемой на фиг. 2 посредством измерения амплитуд напряжений, пропорциональных амплитуде восстановленного тока и его производной, а затем последующего деления первого на второе по выражению (3)

Выходные сигналы блока 3 дифференцирования и интегратора 4 преобразуются при помощи аналого-цифровых преобразователей 9 и 10 (фиг. 2) в числовые эквиваленты, из которых блоками 11 и 12 производится цифровой выбор максимумов, деление которых осуществляет двоичный делитель 13.

Код частного, пропорциональный вели1 чине -- преобразуется цифроаналого(.> вым преобразователем 14 в напряжение.

Умножитель 6 реализует операцию

1 1 d (1в (1 в < 2 !3" д (с ь)

1 1 — — — и 1 cos (at+ ц> )— (> 2 17 L "пc

ic

ЫТ Cos (Qt+Ep )) = (1

;со$ ({vt+u>,) -I всо$ (о +(рв) . (4)

На выходах сумматора 8 формируется напряжение

U =U +U = — I sin(at+(1> )+ в 2 (I„.co ((Dt+g )—

-I cos (у +g„)) . (5)

Данное выражение не содержит коэффициентов зависящих от частоты сети, т.е. функционирование предлагаемого фильтра токов обратной последовательности не зависит от частоты

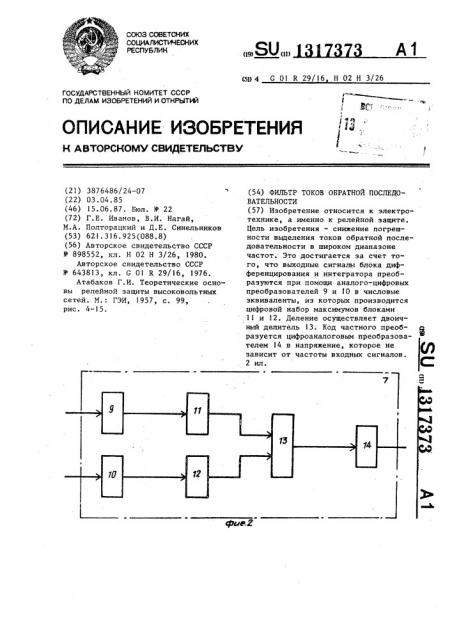

На фиг. изображена функциональная схема предлагаемого фильтра; на фиг. 2 — один из вариантов реализации блока формирования множителя, пропорционального частоте сети.

Фильтр содержит первый 1, второй

2 и третий 3 дифференцирующие блоки, интегратор 4 и вычитатель 5, подключенный входами к выходам дифферен- 2р цирующих блоков 1 и 2, умножитель

6, подключенный одним входом к выходу вычитателя 5,блок 7 формирования множителя, пропорционального частоте сети, подключенный сцним входом к 25 выходу интегратора 4, а другим входом — к выходу третьего дифференцирующего блока 3, и сумматор 8, подключенный одним входом к выходу умножителя 6, а другим входом — к выхо- 3р ду интегратора 4.

Фильтр работает следующим образом.

Вторичные токи фаз С и В после дифференциирования блоками и 2 поступают на входы вычитателя 5, выход- 35 ное напряжение которого определяется выражением с в)

1 d

2 ГР и где 1 и i — мгновенные значения с Ъ вторичных токов в фазах С и В.

Напряжение на выходе третьего дифференцирующего блока 3 равно

1 di 1

U = — = — cDI i os(at+a ), 2 dt 2 а где I,,и и ц>а — амплитуда, круговая частота и начальная фаза тока фазы А.

Интегратор 4 предназначен для вос- 5О становления формы тока фазы А и одновременно для выделения множителя, пропорционального круговой частоте сети. Напряжение И на его выходе равно 55 вхоцных сигналов.

Формула и з обретения

1 и4 2 I $1п(+Ч.) (2) Формирование множителя, пропорционального частоте сети, может осущеФильтр токов обратной последовательности, содержащий первый и второй дифференцирующие блоки, подключенные выходами к входам вычитателя, и сумматор, выход которого является выходом фильтра, о т л и ч а ю щ и йс я тем,что, с целью снижения погрешности выделения токов обратной последовательности в широком диапазоне частот, в него дополнительно введены третий дифференцирующий блок, интегратор, умножитель и блок формирования множителя, пропорционального частоте сети, при этом выход ;ретье1317373

Составитель А. Васильев

Редактор А. Ревин Техред Л.Олийнык Корректор Л. Пилипенко

Заказ 2419/41 Тираж 730 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проект ая, оектная 4 го дифференцирующего блока подключен к одному входу блока формирования множителя, пропорционального частоте сети, и к входу интегратора, выход которого подключен к одному входу 5 сумматора и другому входу блока формирования множителя. пропорционального частоте сети,.подключенного выходом к одному входу умножителя, другой вход которого подключен к выходу вычитателя, а другой вход сумматора подключен к выходу умножителя.