Цифровой квадратичный интерполятор

Иллюстрации

Показать всеРеферат

Изобретение относится к средствам автоматики, вычислительной техники и средствам обработки информации. Интерполятор может применяться при обработке экспериментальной информации , в вычислительной технике, автоматических устройствах управления. Целью изобретения является увеличение быстродействия и сокращение объема аппаратуры интерполятора за счет реализации интерполяции только одномерных функций. Интерполятор содержит два счетчика 1, 2, блок управления 3, блок памяти 4, четьфе регистра 5- 8, операционный блок 9 и новые связи между ними, что позволяет достичь цель изобретения. 4 ил. (Л uroff Дгв«74 со 4 сл Ю Oaixod Puf. J

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (зц 4 С 06 Е 15/353 е

1

° ф

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ

mays c os л Фу

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

llO ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 3904638/24-24 (22) 05.06.85 (46) 15.06.87. Бюл, У 22 (71) Ленинградский институт авиационного приборостроения (72) В. А. Лозицкий, И. А. Корнеев, Д. В. Захаренков, Д. В. Иумилин и Г. М. Марголин (53) 682.14(088,8) (56) Ивахненко А. Г., Лапа В. Г,.

Предсказание случайных процессов, Киев: Наукова думка, 1971, с. 55, рис ° 24, 25.

Авторское свидетельство СССР

И 1290354, кл. G 06 F 15/353, 1986. (54) ЦИФРОВОЙ КВАДРАТИЧНЫЙ ИНТЕРПОЛЯТОР

„„SU„„1317452 А 1 (57) Изобретение относится к средствам автоматики, вычислительной техники и средствам обработки информации.

Интерполятор может применяться при обработке экспериментальной информации, в вычислительной технике, автоматических устройствах управления.

Целью изобретения является увеличение быстродействия и сокращение объема аппаратуры интерполятора за счет реализации интерполяции только одномерных функций, Интерполятор содержит два счетчика 1, 2, блок управления

3, блок памяти 4, четыре регистра 58, операционный блок 9 и новые связи между ними, что позволяет достичь цель изобретения. 4 ил, 52 2 у. — значение функции в (i+2)-й

1+2 точке интерполяции; х — значение аргумента в интерполируемой точке; у(х) — интерполированное значение функции, dx — шаг дискретизации интервала между точками интерполяции; йх — значение интервала между точками интерполяции; U — значение интервала между аргументом в интерполируемой точке и предшествующей точкой интерполяции; Р, (х) — первый интерполяционный полином, Р (х) — второй

2 интерполяционный полином, Цифровой квадратичный интерполятор работает в двух режимах: в режиме линейного развертывания аргумента и режиме внешнего запуска.

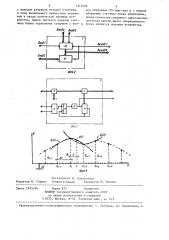

Рассмотрим работу устройства в режиме линейного развертывания аргумента, Обрабатываемый процесс у(х), заданный в точках интерполяции у(х,), 1 в параллельном двоичном коде записывается в блок памяти 4. Эпюра процес. са приведена на фиг. 4. На первый вход устройства подается в параллельном двоичном коде значение интервала между точками интерполяции, На второй вход устройства подается последовательность синхрониэирующих импульссв, Блок 1 пересчета производит дискретизацию интервала между точками интерполяции и формирует значение интервала между аргументом интерполируемой точки и предшествующей точкой интерполяции, которое на фиг, 4 обозначено как и. На первом выходе блока 1 пересчета формируется импульс, соответствующий следующей точке интерполяции. На втором входе блока 1 пересчета Формируется в параллельном двоичном коде значение интервала между аргументом интерполируемой точки и предшествующей точкой интерполяции, которое поступает на первый вход операционного блока 9.

Счетчик 2 формирует в параллельном двоичном коде номер точки, предшествующей интерполируемой точке (на фиг. 4 номер предшествующей точки обозначен через i).

На фиг. 1 показана структурная схема предлагаемого устройства, на фиг, 2 — структурная схема блока пересчета, на фиг. 3 — структурная схема блока управления; на фиг. 4— принцип интерполяции.

Цифровой квадратичный интерполятор содержит блок пересчета 1„ второй счетчик 2, блок управления 3, блок памяти 4, первый регистр 5, второй регистр 6, третий регистр 7, четвер- 4О тый регистр 8, операционный блок 9.

Пересчетный блок вк. †:охает (фиг, 2) двоичный счетчик 10, схему сравнения 11.

Блок управления (фиг. 3) содержит: 45 вычитатель 12, сумматор 13, элемент

ИЛИ 14, RS-триггер 15, генератор импульсов 16, трехразрядныи двоичный счетчик 17, Операционный блок выполнен аналогично прототипу.

На фиг. 4 обозначены . х . — (i—

1- 1

1)-я — точка интерполяции, х; — i-я— точка интерполяции; х;„ — (i+1) точка интерполяции; х, -(х+2)я точка интерполяции; у . — значение функции в (i-1)-ой точке интерполяции; y. — значение функции в i-ой

1 точке интерполяции; у. — значение

"111 функции в (i+1)-й точке интерполяции;

Блок управления 2 формирует в параллельном двоичном коде адреса четырех точек (."" — 1)-й, -й, (+1)-й, (i+ )-й, по которым производится интерполяция, причем значение аргумента интерполируе>"ой точки находится в интервале х;а х < х;,„. На втором

1 13174

Изобретение относится к средствам обработки экспериментальной информации и может быть использовано для интерполирования случайных процессов кривой второго порядка.

В практике обработки экспериментальной информации, представленной в

I виде случайных процессов, часто возникают ситуации, когда обрабатываемый процесс известен только в определенных значениях аргумента, т.е. у.

f(х.) при i = О, и. По данным энаE чениям в точках (узлах) интерполяции определяется величина функции в любой точке аргумента. Предлагаемый !5 цифровой квадратичный интерполятор может быть использован в автоматичес. ких системах обработки информации в радиолокации, телеметрии, связи, а также в вычислительных устройствах 20 при обработке экспериментальной информации, представленной в виде случайных процессов.

Целью изобретения является увеличение быстродействия и сокращение объема аппаратуры интерполятора за счет реализации интерполяции только одномерных функций. и(дх + u) 20

ЙУ; =У;,1 -У;

У 1! У;< 1 1 у = у. где

40

Формул а

3 13174 выходе блока 3 формируются сннхроимлульсы для работы первого 5, второго

6, третьего 7, четвертого 8 регистров.

По адресам опроса блок памяти 4 выдает в параллельном двоичном коде значение функции у., у., у, у.

1 + и

Данные значения поступают в регистры последовательно. Запись происходит с приходом синхроимпульсов из 10 блока 3. Далее значения функции у. у., у., у. поступают на входы

I 141 Э 1б1 операционного блока 9. Операционный блок 9 вычисляет два полинома второй степени 15

Р, (х) = у. + ax+a) P (х) =у.

1 1 дх

u(u — а х) 2 (а х 2, Интерполяционные полиномы приведены на фиг. 4.

На выходах операционного блока 9 формируется интерполированное значение функции y(x) в виде у(х) = — (Р (х) + Р (хЦ

Первый режим работы устройства— режим линейного развертывания аргумента отличается от второго режима — 45 режима внешнего запуска только тем, что при работе в режиме внешнегб за.пуска интерполятор определяет значение функции только в той точке аргумента, координаты которой устанавли- 50 ваются заранее на входах устройства.

В остальном принцип работы квадратичного интерполятора в обоих, указанных режимах идентичен.

55 изобретения

Цифровой квадратичный интерполятор, содержаШий первый и второй счетчики, 52 4 блок памяти, операционный блок, перBbIH второй, третий и четвертый регистры, схему сравнения, причем информационный вход первого счетчика соединен с входом номера интерполируемой точки устройства, счетный вход первого счетчика соединен с входом признака перехода к следующей интерполируемой точке устройства, вход записи счета первого счетчика соединен с входом пуска устройства и с входом записи счета второго счетчика, информационный вход которого соединен с входом задания координаты точки интерполяции устройства, информационный выход первого счетчика со- единен с первым информационным входом операционного блока и с первым входом схемы сравнения, второй вход которой соединен с вторым информационным входом операционного блока и с входом расстояния между точками интерполяции и устройства, вход "Равно" схемы сравнения соединен с входом обнуления первого счетчика с счетным входом второго счетчика, выход блока памяти соединен с информационным входом первого регистра, выход которого подключен к информационному входу второго регистра и к третьему информационному входу операционного блока, выход второго регистра подключен к информационному входу операционного блока, выход третьего регистра подключен к входу четвертого регистра и к пятому информационному входу операционного блока, выход четвертого регистра подключен к шестому входу операционного блока, отличающийся тем, что, с целью увеличения быстродействия, в него введены RS-триггер, вычитатель, сумматор, элемент ИЛИ, генератор тактовых импульсов, счетчик, причем первый вход элемента ЙЛИ подключен к входу пуска устройства, второй вход элемента ИЛИ подключен .к выходу Равно схемы сравнения, выход элемента ИЛИ соединен с установочным входом RS-триггера, выход которого соединен с входом запуска генератора импульсов, выход которого соединен с входами записи первого, второго, третьего и четвертого регистров и с счетным входом счетчика, блока управления, выходы первого и второго разрядов которого подключены к первому входу сумматора, к второму входу .которого подключен выход вычитателя, вход уменьшаемого которого соединен

)3I

7452

ЮюЮ4 д р

Jgyg 4я

Составитель В, Коряковцев

Редактор Н. Горват Техред В.Кадар Корректор М, Шароши

Заказ 2425/44

Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

PpoHsBopcTBeHHo-ïoëèãðàôè÷åñêîå предприятие, г, Ужгород, ул. Проектная, 4 с выходом разрядов второго счетчика, а вход вычитаемое о вычитателя подключен к входу логической единицы устройства, выход третьего разряда счетчика блока управления соединен с вхо6 дом обнуления RS-триггера и с входом обнуления счетчика блока управления, выход сумматора соединен с адресным входом блока памяти, выход операционного блока является выходом устройства.!

I y ! 1 1 фz ! !

|»