Устройство формирования маскирующих сигналов для доменной памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано при построении запоминающих устройств на цилиндрических магнитных доменах (ЦМД). Целью изобретения является повыщение быстродействия и надежности устройства формирования маскирующих сигналов для доменной памяти. Устройство формирования маскирующих сигналов для доменной памяти содержит элемент И 1, элемент ИЛИ 2, коммутатор 3, блок памяти кода маски 4 (ОЗУ m X 1 бит), триггер 5 jl (D-триггер), триггер 6 (Т-триггер), счетчик 7 по модулю Шп. Первые входы элементов И 1 и ИЛИ 2 соединены с инверсным выходом триггера 6, вторые входы элементов И 1 и ИЛИ 2 соединены с первым входом коммутатора 3 и выходом накопителя 8 (информационным входом устройства), выход элемента и 1 соединен с информационным входом блока памяти кода маски 4, выход элемента ИЛИ 2 соединен со счетным входом триггера 5, управляющий вход триггера 5 соединен с синхровходом счетчика 7 и с управляющей шиной 9 (в.ход синхронизации устройства), вход сброса триггера 5 соединен с информационным, входом счетчика 7, входом сброса триггера 6 и щиной 10 «Установка «О, выходы счетчика 7 соединены с соответствующими адресными входами блока хранения кода маски 4, причем последний выход счетчика адреса 7 соединен с счетным входом триггера 6, выход триггера 5 соединен со входом управления режимом запись-чтение блока памяти кода маски 4, выход которого соединен со вторым входом коммутатора, выход которого является вы.ходом устройства . 1 ил. (Л со оо /77 /TJj /77f /77.,

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU,„, 1317480 А 1 (5D 4 G 11 С 11 14

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АBTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4006679/24-24 (22) 06.01.86 (46) 15.06.87. Бюл. № 22 (71) Институт электронных управляющих машин (72) С. М. Захарян, С. В. Замковец, В. Е. Красовский и Г. И. Маркаров (53) 681.327.66 (088.8) (56) Патент США № 4090251, кл. G 11 С 19)08, опублик. 1979.

Авторское свидетельство СССР № 1020861, кл. G 1! С 11)14, 1981. (54) УСТРОЙСТВО ФОРМИРОВАНИЯ

МАСКИРУЮЩИХ СИГНАЛОВ ДЛЯ

ДОМ Е Н НО И ПАМЯ Т И (57) Изобретение относится к области вычислительной техники и может быть использовано при построении запоминающих устройств на цилиндрических магнитных доменах (ЦМД). Целью изобретения является повышение быстродействия и надежности устройства формирования маскирующих сигналов для доменной памяти. Устройство формирования маскирующих сигналов для доменной памяти содержит элемент И 1, элемент ИЛИ 2, коммутатор 3, блок памяти кода маски 4 (ОЗУm Х 1 бит), триггер 5 (D-триггер), триггер 6 (Т-триггер), счетчик 7 по модулю m Первые входы элементов И 1 и ИЛИ 2 соединены с инверсным выходом триггера 6, вторые входы элементов И 1 и ИЛИ 2 соединены с первым входом коммутатора 3 и выходом накопителя 8 (информационным входом устройства), выход элемента И 1 соединен с информационным входом блока памяти кода маски 4, выход элемента ИЛИ 2 соединен со счетным входом триггера 5, управляющий вход триггера 5 соединен с синхровходом счетчика 7 и с управляющей шиной 9 (вход синхронизации устройства), вход сброса триггера 5 соединен с информационным. входом счетчика 7, входом сброса триггера 6 и шиной !О «Установка «О», выходы счетчика 7 соединены с соответствующими адресными входами блока хранения кода маски 4, причем последний выход счетчика адреса 7 соединен с счетным входом триггера 6, выход триггера 5 соединен со входом управления режимом запись-чтение блока памяти кода маски 4, выход которого соединен со вторым входом коммутатора, выход которого является выходом устройства. 1 ил.!

31748О

1О

И 3 О 0 Р с1 (H H (. o T H (> c u I c H fx B hl H H c. I I f 1 (., I ьlioH tехннкс и чожст б»;ть tello 1t)30Bыно при !!<>< jI()С III!!I .Н! i!OЧ!! Н«IК)lttИX Х СТРОИ(. ТВ Н3 ц !лни.срнческих х13! Ии Иых to)!033x 111МД! .

I1(., 1ЬК) И зоо !)(I (It l I i! я В 1 H(I CII Il(>BЫ! I I PI I Ис

ОhfстPО,Tcй T13H«i II II l ж lfос1 и стРОис 1 В3 фоРМИРОВВНИЯ Xi «1 СКИ РХ 10 !1 1!! X Сн !13ЛО В Д. 1и доменной памяти.

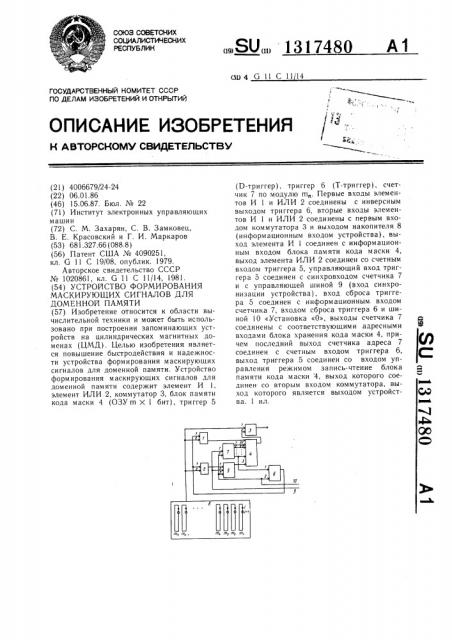

На чертеже «!зобр;!ж ll«l блок-схсча ifp(;сложенного устройства.

Устро«!ство формирования маскируfoH!Hx сигналс)в для домс tt«i(>é II«!xtiiòè (одержит элечснт И 1, элече!Кг И, IИ 2, кочмутатор 3. блок 113xlÿTH ко L3 мыски 4 (ОЗУ01 Х 1 бит), трипер 5 (D-триггер), трипкср 6 (T-триггер), счетчик 7 по чодулю m„. IIс рвые входы элементов И 1 и И;1И 2 сос,!инсны с инверсным Выходом триггера 6, Вторыс

Входы элементов И 1 и ИЛИ 2 соединены с первым входом коммхт«)тора 3 и выход()ч

H3 hoIIHTc. !я 8 (H !i(pop>I HI I Ho«t H h!ix! Bx(i. IO»f устройства), выход элсчснты И 1 сосдинеH с информацис)нныч tfxo, toì блока памяти ко,1а маски 4, выход элемента ИЛИ 2 соединен с счетным Входс)м триггера 5, управляющий вход триггера 5 соединен с синхроВxо 1()м счетчика 7 и с чl1p;l Бл яlо!1!ей !ни!!ой .) (вход синхронизации устройства), вход сброса триггсра 5 сос tf!HCH с иьфорчацис>нныч входс>м счетчика 7, входом сброса триггер» 6 и шиной 10 «Ус!ановкы «0», Выхо lh! с !стчика 7 соединены с соответствую!цими

ыдрс Ht t tн входами олока хранения кода маски 4, причем последний Bhlxo;I, счетчика адрс«ы 7 соединен с счетным входом триггера 6, выход триггера 5 соединен с входом управления режимом запись-чтение блока памяти кода часки 4, выход которого coe;IHHBí с вторым входом коммутатора, Выход которого является выходом устройства.

На чертеже и в тексте приняты слсдуloнсис Обозначения: m, ... m„- номера регистров хранения; пт — дефектный регистр хранения, ичекнций отказ типа «обрыв»; m< --- дефектный рег«!стр хранения, имеющий отказ типа «самозарождение

ЦМ11»; i номер служебной страницы данных, содержащей во всех позициях «1»;

1+1 — ночер служебной страницы дынHhIx, содержац(ей во всех позициях «0».

Устройство работает следующим Образом. Первоначально Ilo 1-му адресу вводят

Цм1 («»), 3 ИО (i + 1 ) -му адресу нс ВВОдят ЦМД («О») во все регистры хранения

m,... гп.„накопителя 8. Далее производится считывание служебной информации, pdclloложенной tto i-му и 1--1-му адресам накопителя. При считывании служебной информации с i-го и !+1-го адресов накопителя 8 по управляющей шине 9 подаются синхроимпульсы, в остальных случаях подается высокий или низкий потенциал. Перед считыванием информации по i-му адресу подачей низкого уровня 110 шине 10 производится устанспзка в нуль триггеров 5, 6 и счетчика 7. Таких> образом, при считывании служсб!И>Й информации с 1-го адреса накопителя 8 на первые выходы элементов И и И. IИ 2 с HHBcpcHot выхода триггера 6 подается высокий потенциал («1») . При эточ высокий уровень. подаваемый с выхода трип сра 5 на Вход управления режимом запись-чтение блока памяти кода маски 4, разрешает запись информации в блок памяти кода мыски 4, поступающей на его информационный вход. Код, состоящий из

«1», записанных ifo адресу 1 в регистры хры«!ения гп! ... m накопителя 8, при считывании изменяется лишь в позиции, соответствующей дефектному регистру хранения rn накопителя 8, имеющего отказ тина

«оорыв» («!» — >«0») . Таким образом, после считывания i-Ой страницы информации в блоке памяти кода маски 4 записывается код, маскирующий дефектные регистры, имею«цие отказ типа «обрыв»; (гп + I)-M синхроичпульсом, поступающим по шине 9, счетчик 7 сбрасывается в нуль, сигнал, поступающий при этом на счетный вход триггера 6, переводит его в единичное состояние.

IIpH c HThfff3HHH + 1 cTp3HH I«bt инфо!)чации с накопителя 8 Во всех позициях будет «О», кроме позиции, соответству>още«! дефектному регистру m, имеющему отказ типы «сымозарождение ЦМД». При этом трип.ер 5, ны первый вход которого поступает единичный уровень, устанавливается в единичное состояние и разрешит запись

«0» в !Т),, -ук> позицию кода маски, хранимой в блоке памяти кода маски 4. После считывания служебной информации, распо.10женной в i-QH и !+1-й странице накопителя 8, в блоке памяти кода маски 4 формируется код, маскирующий как дефектный регистр m имеющий отказ тина «обрыв», так и дефектный регистр m, имеющий отказ типа «самозарождение НМД». После считывания гп„-! о бита служебной информации с I+1-го адреса накопителя 8 производится установка в «О» триггера 5, что устанавливает блок HBMBTH кода маски 4 в режим чтения и позволяет производить чтение и запись информации в накопитель 8 с маскированием дефектных регистров .хранения. После окончания процесса формирования маскирую!цих сигналов производится вывод основной информации, которая поступает из накопителя 8; на второй вход коммутатора 3 синхронно с информацией из блока памяти кода маски 4 поступают маскирующие сигналы (код маски), которые в коммутаторе 3 разрешают прохождение информации только из годных регистров хранения m, m,, m> ... m» накопителя 8 и блокируют информацию из дефектных регистров хранения информации и), и m .

1317480

Формула изобретения

Составитель Ю. Розенталь

Редактор Н. Горват Техред И. Верес Корректор И. Эрдейи

3a к аз 2296/46 Тираж 589 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раугиская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, i.л. Проектная, 4

Устройство форм ирования м аски рующих сигналов для доменной памяти. содержащее блок памяти кода маски, счетчик и коммутатор, отличаюи4ееся тем, что, с целью повышения быстродействия и надежности устройства, оно содержит элемент И, элемент ИЛИ и два триггера, первые входы элементов И и ИЛИ подключены к инверсному выходу первого триггера, вторые входы элементов И и ИЛИ подключены к первому входу коммутатора и являются информационным входом устройства, выход элемента И подключен к информационному входу блока памяти кода маски, выход элемента ИЛИ подключен к счетному входу второго триггера, управляющий вход которого подключен к синхровходу счетчика и является входом синхронизации устройства, вход сброса второго триггера под5 ключен к информационному входу счетчика, входу сброса первого триггера и является установочным входом устройства, выходы счетчика соединены с соответствующими адресными входами блока памяти кода мас ð ки, а последний выход счетчика подключен к счетному входу первого триггера, выход второго триггера подключен к входу управления режимом запись-чтение блока памяти кода маски, выход которого подключен к второму входу коммутатора, выход которого является выходом устройства.