Устройство для контроля блоков памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для функционального контроля блоков оперативной памяти. Цель изобретения - повышение достоверности контроля. Устройство содержит генератор 1 тактовых импульсов, блок 2 синхронизации, счетчик 4 циклов, элемент НЕ 6 и элемент И-НЕ 9, образующие блок управления устройством, регистр 5 сдвига и сумматор 7 по модулю два, выполняющие функцию генератора псевдослучайных сигналов, счетчик 3 адреса , блок 10 сравнения и блок 11 индикации . 1 ил. сл о .4 00 О5

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 G 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3996433/24-24 (22) 23.12.85 (46) 15.06.87. Бюл. ¹ 22 (72) С. Н. Семенов, Ю. А. Марков и В. П. Жибура (53) 681.327 (088.8) (56) Авторское свидетельство СССР № 407398, кл. G 11 С 29/00, 1972.

Авторское свидетельство СССР № 1283858, кл. G 11 С 29/00, 1985..Я0» 1317486 А1 (54) УСТРОИСТВО ДЛЯ КОНТРОЛЯ

БЛСКОВ ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано для функционального контроля блоков оперативной памяти. Цель изобретения — повышение достоверности контроля. Устройство содержит генератор 1 тактовых импульсов, блок 2 синхронизации, счетчик 4 циклов, элемент НЕ 6 и элемент И вЂ” НЕ 9, образующие блок управления устройством, регистр 5 сдвига и сумматор 7 по модулю два, выполняющие функцию генератора псевдослучайных сигналов, счетчик 3 адреса, блок 10 сравнения и блок 11 индикации. 1 ил.

1317486

10

Формула изобретения

Изобретение относится к вычислительной технике и может быть использовано для функционального контроля блоков оперативной памяти.

Цель изобретения — повышение достоверности контроля.

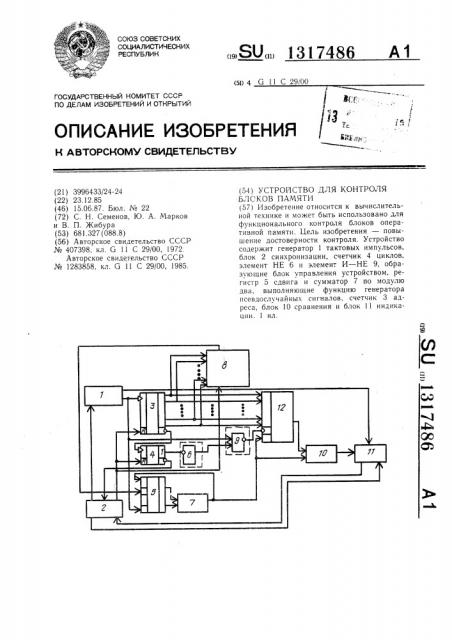

На чертеже изображена структурная схема устройства для контроля блоков памяти.

Устройство для контроля блоков памяти содержит генератор 1 тактовых импульсов, блок 2 синхронизации, счетчик 3 адреса, счетчик 4 циклов, регистр 5 сдвига, элемент НЕ 6, сумматор 7 по модулю два, формирователь 8 установочных сигналов, элемент И вЂ” НЕ 9, блок 10 сравнения и блок 11 индикации. Устройство подключается к контролируемому блоку 12 памяти.

Устройство работает следующим образом, Контролируемый блок 12 запоминает последовательно вводимую информацик в порядке ее поступления и последовательно выдает информацию в порядке, определяемом очередностью записи этой информации.

В процессе работы устройство реализует два цикла контроля блока 12 (образуюшие полный цикл контроля): запись "естовой последовательности в память; считывание тестовой последовательности из памяти.

Таким образом, устройство работает в двух режимах, режиме записи информации по адресам и в режиме считывания записанной информации, при котором осушествляется выявление неисправностей контролируемого блока 12.

По команде «Пуск» блока 2 счетчик 3 адреса и одноразрядный счетчик 4 устанавливаются в нулевое состояние. Регистр 5 сдвига также устанавливается в начальное (единичное) состояние. После этого запускается генератор 1 тактовых импульсов, который начинает выдавать тактовые импульсы на вход блока 1! индикации, а также на счетный вход счетчика 3 адреса, на вход синхронизации регистра 5 сдвига и на вход элемента И вЂ” НЕ 9.

Счетчик 3 адреса работает в режиме непрерывного пересчета, формируя код адреса, по которому производится обрашение к ячейкам памяти блока 12. Код адреса поступает на адресные входы контролируемого блока 12 и на входы формирователя 8.

Формирователь 8 обеспечивает формирование управляющего сигнала для регистра 5 сдвига, при этом задним фронтом импульса «Установка» обеспечивается запись начальной информации в регистр 5 сдвига.

Счетчик 4, элемент 6 НЕ, элемент И вЂ” Н =

9 обеспечивают работу устройства в режимах записи и чтения («О» — «Запись», «l»-«Считывание») .

При первом проходе по адресам контролируемого блока 12 (первый цикл контроля) осуществляется режим «Запись», при втором проходе по адресам (второй цикл контроля) осуществляется режим «Чтение».

Таким образом, в режиме записи счетчик

3 адреса формирует последовательность адресов. B режиме считывания формирует ту же адресную последовательность, что и при записи и обеспечивает считывание из блока

12 информации, записанной в него в режиме записи.

В течение первого цикла контроля регистр 5 сдвига работает в режиме непрерывного сдвига записанной в него информации, затем по заднему фронту импульса «Сброс» осуществляется запись в регистр 5 сдвига исходной информации и осуществляется следующий цикл контроля. При этом регистр

5 сдвига совместно с сумматором 7 формирует псевдослучайную последовательность максимальной длины.

В предлагаемом устройстве разрядность регистра 5 сдвига должна быть не меньше, чем разрядность счетчика 3 адреса.

С помошью регистра 5 сдвига и сумматора 7 можно формировать меняющееся от проверки к проверке (за счет соединения различных выходных разрядов регистра 5 сдвига с входами сумматора 7 псевдослучайным образом) распределение информации в контролируемом блоке 12 памяти.

Устройство для контроля блоков памяти, содержащее генератор тактовых импульсов, блок синхронизации, формирователь установочных сигналов, счетчик адреса, регистр сдвига, блок сравнения и блок индикации, причем первый, второй и третий выходы блока синхронизации подключены соответственно к синхровходу генератора тактовых импульсов, входу сброса счетчика адреса и входу сброса блока индикации, синхровход которого соединен с первым выходом генератора тактовых импульсов, информационный вход и выход блока индикации подключены соответственно к выходу блока сравнения и установочному входу блока синхронизации, второй выход генератора тактовых импульсов соединен с входом синхронизации регистра сдвига и счетным входом счетчика адреса, выходы разрядов которого являются адресными выходами устройства, информационным входом которого является первый вход блока сравнения, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены счетчик циклов, сумматор по модулю два, элемент НЕ и элемент И вЂ” НЕ, выход которого является выходом записи-чтения устройства, причем вы1317486

Составитель В. Рудаков

Редактор Н. Горват Техред И. Верес Корректор И. Эрдейи

Заказ 2296/46 Тираж 589 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

l13035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 ходы разрядов и выход переполнения счетчика адреса подключены соответственно к одним из входов формирователя установочных сигналов и счетному входу счетчика циклов, выход переполнения и информационный выход которого соединены соответственно с входом смены цикла блока синхронизации и входом элемента НЕ, выход которого подключен к одному из входов элемента

И вЂ” НЕ, другой вход которого соединен с вторым выходом генератора тактовых импульсов, другой вход и выход формирователя установочных сигналов соединены соответственно с вторым выходом блока синхронизации и управляющим входом регистра сдвига, информационный вход которого и

5 второй вход блока сравнения подключены к выходу сумматора по модулю два, вход сброса счетчика циклов соединен с вторым выходом блока синхронизации, входы сумматора по модулю два соединены с группой выходов регистра сдвига, а выход сумматора по модулю два является информационным выходом устройства.