Преобразователь унитарного кода в двоичный код

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении преобразователей и блоков сопряжения в цифровых системах . Целью изобретения является повышение быстродействия преоЬразователя и расширение класса решаемых задач за счет обеспечения возможности преобразования в последовательный код. Поставленная цель достигается тем, что в преобразователь унитарного кода в двоичный код, содержащий регистр 2, шифратор 1,первый элемент ИЛИ 3, дополнительно введены формирователь одиночного импульса 4, генератор серий импульсов 5, второй и третий элементы ИДИ 6, 7, что значительно уменьшает время на преобразование кодов. 2 ил. I (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (191 (11) (51)4 Н 03 М 7 12

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А STOPCKOMV СВИДЕТЕЛЬСТВ(0

2

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3993855/24-24 (22) 21 ° 10. 85 (46) 15.06.87. Бюл. 11 22 (72) А. Г.орехов, Б.В.Гришин и В.И.Тябин (53) 681.325(088.8) (56) Авторское свидетельство СССР

}Â 917342, кл. Н 03 М 7/00, 1981.

Авторское свидетельство СССР

У 921081, кл. Н 03 М 7/02, 1981 ° (54) ПРЕОБРАЗОВАТЕЛЬ УНИТАРНОГО КО.дА в двоичный код (57) Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении преобразователей и блоков сопряжения в цифровых системах. Целью изобретения является повышение быстродействия преобразователя и расширение класса решаемых задач за счет обеспечения возможности преобразования в последовательный код. Поставленная цель достигается тем, что в преобразователь унитарного кода в двоичный код, содержащий регистр 2, шифратор 1,первый элемент ИЛИ 3, дополнительно введены формирователь одиночного импульса 4, генератор серий импульсов

5, второй и третий элементы ИЛИ 6, 7, что значительно уменьшает время на преобразование кодов. 2 ил.

1 13176

Изобретение относится к автоматике и цифровой выи лительной технике и может быть использовано при построении преобразователей и блоков сопряжения в цифровых системах.

Цель изобретения — повышение быстродействия преобразователя и расширения класса решаемых задач путем обеспечения воэможности преобразования в последовательный код. 10

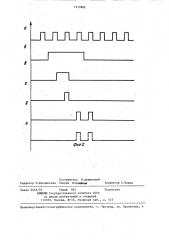

На фиг. 1 представлена структурная схема преобразователя кодов; на фиг. 2 — временная диаграмма сигналов при его работе.

Преобразователь кодов содержит шифратор 1, регистр 2, первый элемент ИЛИ 3, формирователь 4 одиночного импульса, генератор 5 серий импульсов, второй 6 и и третий 7 элементы ИЛИ, информационные входы 8, 20 управляющий вход 9, тактовый вход

10, информационный выход 11 и тактовый выход 12.

Рассмотрим работу устройства при

25 преобразовании кода с основанием 4 (ш 4) в код с основанием 2 (в двоичный код), при этом информационный вход 8 устройства должен содержать

4 линии (О, 1,2,3j, причем одновременное наличие сигнала на двух 30 или более линиях должно быть исклю, чено. Для определенности допустим, что при появлении сигнала на линии

О на выход преобразователя кодов должен быть передан двоичный двухразрядный код »00", при появлении сигнала на линии 1 — двоичный двухраэряд- . ный код «10", при появлении сигнала на линии 2 — двоичный двухразрядный код «01", при появлении сигнала на 40 линии — 3 двоичный двухраэрядный код «11».

В предлагаемом преобразователе кодов шифратор 1 предназначен для формирования двоичного К-разрядного ко- 45 да (К находят иэ соотношения m < 2

% и округляется до целого числа; при ш =4, к=2) .

Регистр 2 предназначен для записи в него двоичного параллельного К-раз- g0 рядного кода с шифратора 1 и выдачи

его потребителю в виде К-разрядного последовательного двоичного кода.

Запись информации, поступающей из шифратора 1 в регистр 2, осуществляется при наличии сигнала »1» на входе разрешения записи тактовым импульсом, фронт которого задержан относительно фронта сигнала с выходов шиф62 2 ратора 1 на величину, определяемую из соотношения: (I

IVlOI К С где „,„„ — минимально допустимая величина задержки между фронтами сигналов на информационном и тактовым входами используемого регистра; „ „, — минимально допустимая длительность входного информационного сигнала;

,1, — длительность импульса формирователя одиночного импульса.

Тактовый импульс поступает на вход С регистра 2 через элемент

ИЛИ 6 с первого выхода формирователя одиночного импульса 4, а сигнал " 1» на вход разрешения записи поступает с второго выхода формирователя одиночного импульса 4 через элемент

ИЛИ 7 (для обеспечения записи информации в регистр 2 параллельньц1 кодом необходимо на вход разрешения записи подать сигнал »1", а для записи информации в последовательном коде .сигнал »0").

В регистре 2 последовательные информационные вход и выход соединены между собой, что позволяет при выдаче выходного преобразуемого кода

его вновь записывать в регистр 2.

В качестве формирователя одиночного импульса 4 может быть исполь-. зован любой формирователь, обеспе чивающий по фронту запускающего сигнала на первом выходе импульс положительной полярности длительностью, равной длительности импульса на тактоном входе 10 (фиг. 2а), а на втором выходе — импульс, фронт которого должен опережать фронт импульса на первом выходе, а спад его должен быть задержан относительно спада импульса на втором выходе (фиг. 2в,г).

Генератор серий импульсов 5 предназначен для формирования К импульсов, синхронных с сигналами на входе .

10 и задержкой первого импульса се- . рии не менее чем на период сигнала на входе 10.

Устройство работает следующим об- разом.

Сигнал, пришедший по одной иэ линии информационного входа 8, например, по линии 3, поступает через

7662

35

3 13 I элемент ИЛИ 3 (фиг. 26) и запускает фронтом формирователь 4 одиночного импульса. Одновременно сигнал поступает на шифратор 1, на выходе которого, а следовательно, и на входах D,,D (фиг..26) регистра 2, появятся единичные сигналы (в данном примере двоичный 2-разрядный параллельный код "!1") на время действия входного сигнала.

На выходах формирователя 4 одиночного импульса формируются два импульса: импульс с второго выхода (фиг. 2в) поступает на вход разрешения записи регистра 2 и переводит его в режим записи информации с .шифратора 1 по входам П,, D (фиг.

26) параллельным кодом. Запись информации осуществляется импульсом с первого выхода .формирователя одиночного импульса 4 (фиг. 2 r), поступающим через элемент ИЛИ 6 на тактовый вход регистра 2. После окончания записи информации в регистр 2 с шифратора 1 регистр 2 переводится в режим записи информации по входу D (в режим выдачи информации с регистра в последовательном коде) путем подачи на вход разрешения записи нулевого сигнала; по сигналу с первого выхода формирователя 4 одиночного импульса .через элемент ИЛИ 7 запускается генератор 5 серий импульсов, который вырабатывает К (К =2) тактовых импульсов (фиг. 2д), передаваемых на выход 12 и через элемент ИЛИ б на тактовый вход регистра 2, с помощью которых информация с регистра 2 (фиг. 2е) передается на выход 11,а также вновь записывается по входу

D в регистр 2.

По сигналу на управляющем входе

9 через элемент ИЛИ 7 запускается генератор серий импульсов 5 и его тактами на выход 11 выдается последовательный К разрядный код, записанный в регистр 2 сигналом, поступившим в преобразователь кодов перед приходом сигнала по управляющему входу 9.

Таким образом, в предлагаемом устройстве отпадает необходимость последовательного опрашивания входных информационных шин, что значительно ускоряет преобразование кодов. С выхода устройства возможно считывание кодов как в последовательном, так и в параллельном виде.

Формула изобретения

Преобразователь унитарного кода в двоичный код, содержащий регистр, шифратор, первый элемент ИЛИ,входы которого являются информационными входами преобразователя, выходы шифратора соединены с информационными входами регистра, выход которого является информационным выходом преобразователя, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия и расширения, класса решаемых задач, за счет обеспечения возможности преобразования в последовательный код, в него дополнительно введены формирователь одиночного импульса, второй и третий элементы

ИЛИ и генератор серий импульсов,выход которого соединен с тактовым выходом преобразователя и с первым входом второго элемента ИЛИ,выход которого соединен с тактовым входом регистра, вход последовательного кода которого соединен с выходом старшего разряда регистра, вход разрешения записи которого соединен с первым выходом формирователя одиночного импульса, второй выход которого соединен с вторым входом второго элемента ИЛИ и первым входом третьего элемента ИЛИ, выход которого соединен с входом пуска генератора серий импульсов, тактовый вход которого соединен с тактовым входом преобразователя и с тактовым входом формирова45 теля одиночного импульса, информационный вход которого соединен с выходом первого элемента ИЛИ, управляю(щий вход преобразователя соединен с вторым входом третьего элемента

ИЛИ.

1317662

Составитель М,Аршавский

Редактор Л.Пчелинская Техред Д. Олийнык

Корректор С.Черни

Заказ 2435/55 Тираж 901

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, r, Ужгород, ул. Проектная, 4