Устройство для анализа импульсных последовательностей

Иллюстрации

Показать всеРеферат

Изобретение Ьтносится к радио техиике и обеспечивает повышение достоверности анализа при одновременном увеличении помехозащищенности. Устройство содержит инвертирующий операционньш усилитель (ОУ) 1, инвертор 2, формирователи импульсов (ФИ) 3,4, накопители 5,6, пороговые блоки (ПБ) 7,8, элемент 2И-НЕ 9 и компаратор 10. Инвертор 2 и ФИ 3,4, служат для устранения влияния внутреннего сопротивления источника входных импульсных сигналов на работу накопителей 5,6. Во время действия импульса происхо- : дит уменьшение напряжения на входе ПБ 7 и увеличение напряжения на входе ПБ 8„ В паузах между импульсами происходит наоборот. При этом на выходах ПБ 7,8, элемента 2И-НЕ 9 и на втором, третьем и четвертом выходах устройства отсутствуют аварийные сигналы , а на первом выходе появляется сигнал о наличии импульсов на входе устройства. Пропадание импульсного сигнала на входе устройства из-за короткого замыкания цифровой линии, О что эквивалентно , приводит к постепенному увеличению напряжения на выходе накопителя 5. В результате сигнал с ОУ 1 запрещает работу компаратора 10, исключая появление сигнала на первом выходе устройства, а на втором выходе появляется сигнал о пропадании сигнала на входе устройства . Проладание сигнала вследствие обрьта линии, что эквивалентно появлению 1, приводит к уменьшению напряжения на накопителе 5. В результате на четвертом выходе устройства появляется сигнал наличия обрьта линии. 1 ил. М / а S : а 00 01

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСНОМ У СВИДЕТЕЛЬСТВУ ф

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3868582/24-09 (22) 18.03.85 (46) 15 ° 06.87. Бюл. № 22 (72) А.А. Дубинин, А,Г. Коротич, Ю.В. Лештаев, В.M. Ножников и С.Н, Сухов (53) 621.395.63(088.8) (56) Авторское свидетельство СССР

¹ 721924, кл. Н 04 M 3/22//

// Н 04 Q 11/02, 1977. (54) УСТРОЙСТВО ДЛЯ АНАЛИЗА ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ (57) Изобретение Ьтносится к радио технике и обеспечивает повышение достоверности анализа при одновременном увеличении помехозащищенности. Устройство содержит инвертирующий операционный усилитель (ОУ) 1, инвертор 2, формирователи импульсов (ФИ) 3,4, накопители 5 6 пороговые блоки (ПБ)

7,8, элемент 2И-НЕ 9 и компаратор 10.

Инвертор 2 и ФИ 3,4, служат для устранения влияния внутреннего сопротивления источника входных импульсных сигналов на работу накопителей 5,6.

Во время действия импульса происхо(51) 4 Н 04 M 3/22//Н 04 11/02 дит уменьшение напряжения на входе

ПБ 7 и увеличение напряжения на вхо де ПБ 8. В паузах между импульсами происходит наоборот. При этом на выходах ПБ 7,8, элемента 2И-НЕ 9 и на втором, третьем и четвертом выходах устройства отсутствуют аварийные сигналы, а на первом выходе появляется сигнал. о наличии импульсов на входе устройства. Пропадание импульсного сигнала на входе устройства из-за короткого замыкания цифровой линии, что эквивалентно "0", приводит к постепенному увеличению напряжения на выходе накопителя 5. В результате сигнал с ОУ 1 запрещает работу компаратора 10, исключая появление сигна- 9 ла на первом выходе устройства, а на втором выходе появляется сигнал о пропадании сигнала на входе устройст- С ва. Пропадание сигнала вследствие обрыва линии, что эквивалентно появлению "1", приводит к уменьшению напряжения на накопителе 5. В результате на четвертом выходе устройства появляется сигнал наличия обрыва линии.

1 ил.

1 1317685 ;2

I t l1 явлению 1, приводит к постепенному уменьшению напряжения на первом накопителе 5, и сигнал на выходе первого порогового блока 7 пропадает.Одновременно на выходе инвертора 2 появляется сигнал, соответствующий по уровюи ню 0 . Второй формирователь 4 импульсов, второй накопитель 6 и второй пороговый блок 8 работают onuf0 санным образом. В результате на выходе второго порогового блока 8, на четвертом выхоце устройстваи входах элемента 2И-НЕ 9 и компаратора 10 появляется сигнал наличия обрыва цифрового тракта. По этому сигналу на выходе элемента 2И-НЕ 9, входе инвертирующего операционного усилителя I и втором выходе устройства появляется сигнал пропадания входных импупьсэв.

1 1(ампаратор 10 снова блокируется сиг налом запрета, поступающим .с выхода инвертирующего операционного усилителя 1.

При наличии импульсного сигпала на входе устройство работает следующим образом.

Изобретение относится к радиотехнике и может использоваться для контроля и анализа цепей импульсных устройств, Цель изобретения — повышение достоверности анализа при одновременном увеличении помехозащищенности.

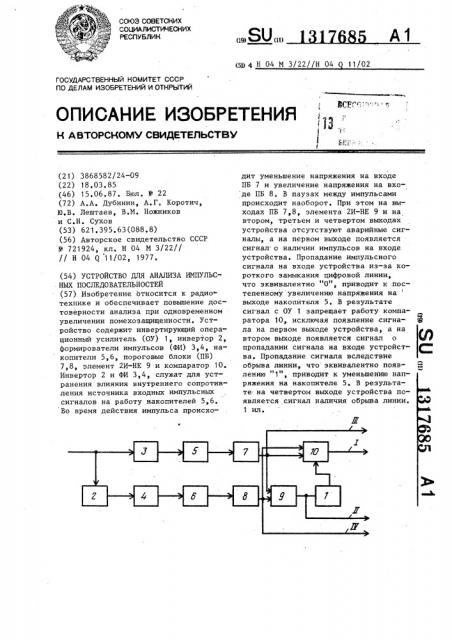

На чертеже представлена структур( ная электрическая схема предложенного устройства, Устройство для анализа импульсных последовательностей содержит инвертирующий операционный усилитель 1, инвертор 2, первый 3 и второй 4 формирователи импульсов, первый

5 и второй 6 накопители, первый 7 и второй 8 пороговые блоки, элемент 2ИНЕ 9, компаратор 10.

Устройство работает следующим аб- 20 разом.

Импульсный сигнал с входа устройства поступает на входы первого формирователя 3 импульсов и инвертора 2.

Инвертор 2 и первый формирователь 3 25 импучьса, а также второй формирователь 4 импульса служат для устране- ния влияния внутреннего сопротивления источника входных импульсных сигналов (не показан) на работу первого gg

5 и второго 6 накопителей.

Пропадание импульсного сигнала на входе устройства, вызванное коротким замыканием цифрового тракта,, что эквивалентно н0", приводит к постепенному увеличению напряжения на выходе первого накопителя 5, При возрастании этого напряжения до уровня, достаточного для срабатывания первого порогового блока 7, на выходе послед- р0 него появляется сигнал, свидетельствующий о наличии "0" на входе устройства. Этот сигнал одновременно поступает на в ады элемента 2И-НЕ 9, компаратора 10 и третий выход устройства. На выходе элемента 2И-НЕ 9 появляется сигнал, свидетельствующий о пропадании импульсного сигнала на входе устройства, Сигнал с выхода элемента 2И-НЕ 9 поступает на второй выход устройства и вход инвертирующего операционного усилителя 1, с выхода которого поступает сигнал запрета на вход компаратора 10, который препятствует появлению сигнала на первом 55 выходе устройства.

Пропадание импульсного сигнала на входе устройства вследствие обрыва цифровой линии, что эквивалентно поВо время действия импульса происходит уменьшение напряжения на входе первого порогового блока 7 и увеличение на входе второго порогового блока 8. В паузах между импульсами происходит увеличение напряжения на входе первого порогового блока 7 и уменьшение напряжения на входе второго порогового блока 8, При этом на выходах первого и второго пороговых блоков

7 и 8, элемента 2И-НЕ 9 и четвертом, третьем и втором выходах устройства отсутствуют аварийные сигналы, в результате на выходе инвертирующего операционного усилителя 1 также отсутствует сигнал запрета работы компаратора 10, и на первом выходе устройства появляется сигнал, свидетельствующий О наличии импульсов Iid exo де устройства, Формула и з о б р е т е и и я

Устройство для анализа импульсных последовательностей, содержащее первый формирователь импульсов, вход которого является входом устройства, первый и второй накопители, кампаратор, выход которого является первым выходом устройства, а т л и ч а ю— щ е е с я тем., чтс, i целью повышения достоверности анализа при одно1317685

Составитель Е. Голуб

Редактор N, Келемеш Техред В.Кадар Корректор С. Шекмар

Заказ 2437/56 Тираж 638 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35» Раушская наб.„ д. 4/5.Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 временном увеличении помехозащищенности, введены первый и второй пороговые блоки, последовательно соединенные инвертор, вход которого соединен с входом первого формирователя импульсов, и второй формирователь импульсов, выход которого подключен к входу второго накопителя, выход которого подключен к входу второго порогового блока, последовательно соединенные элемент 2И-НЕ, первый вход которого соединен с выходом второго порогового блока, и инвертирующий операционный усилитель, выход котороro подключен к управляющему входу компаратора, первый и второй информационные входы которого соединены соответственно с выходами соответственно первого и второго пороговых блоков, выход первого формирователя импульсов через первый накопитель подключен к входу первоио порогового блока, выход которого подключен к втоf0 рому входу элемента 2И-HE выход которого, а также выходы первого и второго пороговых блоков являются соотретственно вторым, третьим и четвертым выходами устройства.