Устройство для вычисления свертки

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислительных систем, функционирующих в реальном масштабе времени. Цель изобретения - упрощение устройства. Поставленная цель достигается за счет того, что в состав устройства входят К L вычислительных блоков 1.1 - 1.KL, блок регистров 2 и L коммутаторов 3.1-3.L, причем каждый вычислительный блок содержит два буферных регистра, регистр коэффициента, умножитель,, регистр результата и сумматор. Уменьшение объема оборудования обусловлено тем, что за счет рациональной организации вычислительного процесса в устройстве отпадает необходимость в применении L - 1 линий задержки длиной N - К ячеек каждая . 2 шт. а (Л со со о 4 СП

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51) 4 G 06 F 15/353

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Н А BTOPCKOMY СВИДЕТЕЛЬСТВУ (21) 4016098/24-24 (22) 29.01. 86 (46) 23.06.87. Бюл. Ф 23 (71) Киевский политехнический институт им. 50-летия Великой Октябрьской социалистической революции (72) А. В. Выжиковска (SV), Роман Выжиковски (PL), Дариуш Гретковски (PL) и Ю. С. Каневский (SV) (53) 628.32(088.8) (56) Рабинер Л., Гоулд Б. Теория и применение цифровой обработки сигналов. — M.: Мир, 1978.

Авторское свидетельство СССР

Ф 1198535, кл. G 06 F 15/353, 20.11.84. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СВЕРТКИ (57) Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислительных систем, функционирующих и реальном масштабе времени. Цель изобретения — упрощение устройства, Поставленная цеЛь достигается эа счет того, что в состав устройства входят К L вычислительных блоков 1.1 — 1.KL, блок регистров 2 и L коммутаторов 3.1-3.LI причем каждый вычислительный блок содержит два буферных регистра, регистр коэффициента, умножитель,, регистр результата и сумматор. Уменьшение объема оборудования обусловлено тем, что за счет рациональной органиэации вычислительного процесса в устройстве отпадает необходимость в применении L — 1 линий задержки длиной и — К ячеек каждая. 2 ил.

1 !3

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислительных систем, функционирующих в реальном масштабе времени.

Цель изобретения — упрощение устройства.

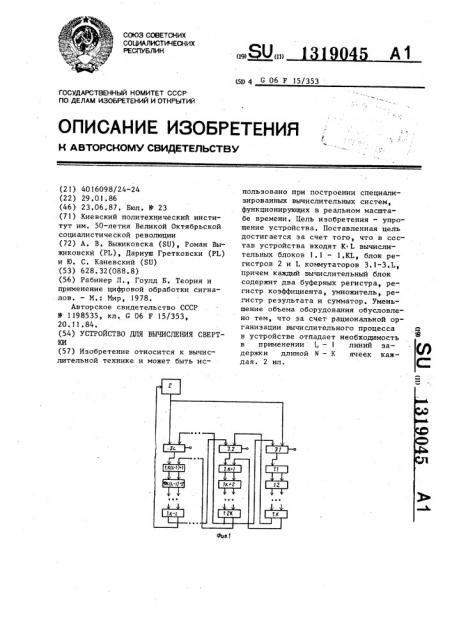

На фиг, 1 изображена схема устройства; на фиг. 2 — схема вычислительного блока, Устройство (фиг. 1) содержит KL вычислительных блоков 1.1, 1.2,...

° 1 4 ФКТ Э

Каждый из вычислительных блоков

l.i (фиг, 2) содержит буферный регистр 4.i регистр 5.i регистр 6 ° i коэффициента, умножитель 7,1, регистр 8.i результата, сумматор 9,i и регистр 10.1 результата.

При выполнении одномерной свертки устройство работает следующим образом. Во время этой операции под воздействием сигнала "Одномерная свертка", поступающего на управляющий вход устройства, коммутаторы 3.1, кроме 1=1, передают информацию, поступающую из первого информационного выхода вычислительного блока

1,(1-1)К, на первый информационный вход вычислительного блока 1,(1— 1)К+1, а коммутатор 3.1 — на пер= вый информационный вход вычислительного блока 1,1 отсчеты входной последовательности Х(1)...X(P), которые одновременно с подачей сигнала "Одномерная свертка" начинают поступать из выхода основной памяти 2 со скоростью одного отсчета на такт, Определяют базовые операции А и

В, причем под базовой операцией следует понимать повторяющуюся совокупность действий, выполняемых вычислительным блоком, Базовая операция А выполняется в течение одного такта в вычислительном блоке 1 следующим образом, В исходный момент времени в первом буферном регистре 5.i хранится one(z) ранд .а,, который затем поступает на второй вход умножителя 7 ° 1 на первый вход которого с выхода регистра б.i коэффициента поступает коэффициент И (К L-i+1), Затем умножитель 7.i формирует произведение ц(К L-i+1) ° а„, которое с приходом тактового импульса записывается в первый регистр 8,i результата, Под

19045 2

y(n) = u(D)X(n+D-1)+о(П-1) X(n+D-2)+

30. +а(П-2) X(n+D-3)+. ° . +CO(1) X(n), 5

f0

55 воздействием тактового импульса происходит также перезапись содержимого а;, первого буферного регистра (z>

5.(i-l) и содержимого а, второго (<) регистра 4.i соответственно во второй буферный регистр 4.i и первый буферный регистр 5.i (в случае блока 1.1 во второй буферный регистр

4.i записывается новый входной отсчетт), Базовая операция В выполняется в течение одного такта в вычислительном блоке 1. i следующим образом. В исходный момент времени в первом 9.i и втором 10.(i-l) регистрах результата хранятся соответственно произведение а (К L-i+1)a; (2) и частичный результат Ь;,, которые затем поступают на входы сумматора

9.i, формирующего их сумму. С приходом тактового импульса указанная сумма записывается во второй регистр

l0.i результата, Формирование отсчета выходной последовательности с номером n(n=

=1,2,...,P-К L+1) определяют выражением гдеП=К1..

Поступление отсчетов входной последовательности, которые участвуют в формировании y(n) начинается в такте с номером и когда во второй буферный регистр 4,1 поступает отсчет

X(n). Затем в течение последующих

D-1 тактов продолжается поступление отсчетов X(n+1), Х(п+2)... °,X(n+D-l), причем каждый нОвый входной отсчет записывается в регистр 4,1, а ранее поступившие отсчеты сдвигаются в одну позицию в регистре сдвиrа, который образуется буферными регистрами 4.i и 5,i Таким образом, в такте n+D отсчет X(n+D+1) поступает в первый буферный регистр 5,! а отсчеты

X(n+D-2), X(n+D-3)... °,X(n) запишутся в следующих позициях регистра сдвига. Формирование результата y(n) начинается в такте n+D+1, в течение которого в блоке 1 ° 1 выполняется базовая операция А, в результате которой в первый регистр 8,1 результата записывается произведение ca(D)X(n+

+D-!). Кроме этого, отсчет X(n+D-2) записывается в регистр 5.2, отсчет

X(n+D-3) в регистр 4,3, отсчет X(n+

+D-4) в регистр 5,3 и т.д.

3 13190

Такт n+D+2. В блоке 1.1 выполняется базовая операция В, в результате которой во второй регистр 10.1 результата записывается сумма у(п) =

=<Р + Q (D) ° X(n+D-1) (на первый вход сумматора 9.1 всегда подается код нуля), а в блоке 1.2 выполняется базовая операция А, в результате которой в первый регистр 8.2 результата записывается произведение co(D-1)X(n+ f0

+D-2), Кроме этого, отсчет X(n+D-3) записывается в регистр 5.3, отсчет

X(n+D+4) в регистр 4.4, отсчет Х(п+

+D-5) в регистр 5.4, и т.д.

Такт n+D+3. В блоке 1.2 выполняет- 15 ся базовая операция В, в результате которой во второй регистр 10.2 ре-, зультата записывается сумма у(п) (n) + ()(Р-IХ (n+D-2), а в блоке

1.3 — базовая одерация А, в результа-20 те которой в первый регистр 8.3 результата записывается произведение

Q{D-2)X(n+D-3). Кроме того, отсчет

X(n+D-4) записывается в регистр 5.4, отсчет X(n+D-5) в регистр 4,5 и т,д.

Такт n+D+4. В блоке 1.3 выполняется базовая операция В, в результате которой во второй регистр 10.3 результата записывается сумма у(п) у(п) + сд(D-2)X(n+D-3), а в блоке 30

1.4 — базовая операция А, в результате которой в первый регистр 8.4 результата записывается произведение И (D-3)X(n+D-4). Кроме этого, отсчет X(n+D-5) записывается в ре- 35 гистр 4.5, отсчет X(n+D-6) в регистр

5.5 и т.д.

Такт n+2D. В блоке 1.7 (D-1) выполняется базовая операция В, в результате которой во второй регистр 40

10.(D-I) результата записывается сумма у(п), = y(n)z + са(2)Х(п+1), а в блоке I.D — базовая операция А, в результате которой произведение

Q(I)X(h) записывается в первый ре- 45 гистр 8.D результата.

Такт и+2Р+1. В блоке I.D выполняется базовая операция В, в результате которой во второй регистр IО.D результата записывается окончательное значение y(n), откуда поступает в основную память 2. При выполнении двумерной свертки устройство работает следующим образом. Во время этой операции в регистре б.i коэффициента, где i=KL+K хранится коэффициент

Q(K-K+I 1). Одновременно с подачей сигнала "Двумерная свертка", который к

y(n, .m)= u(K, 1)X(n+K-1,ш)+

k=l

+ ы (К, к= к

+ ы(К, к=>

+у (nm)+ ..

2)X(n+K-1, ш+1)+...+

L) X(n+K-1, ш+Т;1) =у (n,m)+

° +у (n, m)

L где 1 п 6 2К 1 с ш & M-L+1, Формирование отсчета у (n,m) начинается в такте с номером S =R(n+

+К- l, m)+2(L 1)К+2=К(2Т.+Зш-4)-ш+

+n+2, когда на вход первого буферного регистра 5.1 поступает входной отсчет X(n+K-l, m); который с приходом очередного тактового импульса записывается в указанный регистр.

В следующем такте с номером S +1 в вычислительном блоке 1.1 выполняется базовая операция А, в результате ко- . торой в первый регистр 8.1 результата записывается произведение и (К,l)Х(п+

+К-l, ш).

Такт S+2. В вычислительном блоке

1.1 выполняется базовая операция В, в результате которой во второй регистр 10.1 результата записывается сумма у (n, m) = P + са(К, l)X(n+K-1, ш), а в вычислительном блоке

1.2 — базовая операция А, в результате которой в первый регистр 8.2

45 4 поступает на управляющий вход устройства, с выхода блока 2 регистров на вход второго буферного регистра 4. (L- 1)К+1 посредством, коммутатора 3.1. (поскольку на его управляющий вход поступает сигнал "Двумерная свертка") со скоростью одного отсчета на такт начинают поступать отсчеты X(n, ш) входного массива, удовлетворяющие условию 1 ап ЗК-I, 1 аm ыM. При этом указанные отсчеты передаются по столбцам, т.е. в такте с номером

R(n, m)=(m-1)(ЗК-1)+и на вход регистра 4.(L-I)К+1 поступает отсчет

Х(п, ш), который затем с приходом каждого тактового импульса сдвигается на одну позицию в регистре сдвига, образованный 2L К буферными регистрами 4(L-1)К+1, 5.(L-I)К+1, 4.(L-I) ° К+2, 5.(L-I)K+2, 4.Т.К, 5.L К, 4. (Т;2)К+1, 5. (L-2)К+1, 4. (Ь-2)К+2 ) 5. (Т;2) К+2,...,4. (L-2) К+

+К, 5, (Т;2) К+К,...,4. 1,5. 1, 4. 2, 5.2,...,4.К, 5.К.

Формирование произвольного отсчета y(n, m) выходного массива определяют выражением

1 3 I 9045 6 результата записывается произведение та(К-1, l)Х(п+К-2, m).

Такт S+3. В вычислительном блоке

1.2 выполняется базовая операция В, в результате которой но второй регистр 10.2 результата записывается сумма у (n, m) .=У (n, m), + то(К-1), 1)X(n+K-2, m), а в вычислительном блоке 1.3 - базовая операция А, н результате которой в первый регистр

8.3 результата записывается произнедение (1(К-2, 1)Х(п+К-З, m).

Такт S+K+I, В вычислительном блоке 1.К выполняется базовая операция

В, в результате которой во второй регистр 10.К результата записывается сумма у (n, m) =ут(n, m) К--у (и, m), +

+тд(1, 1)Х(п,m) . В этом же такте в вычислительном блоке 1,К+1 выполняется баэоная операция А, в результате которой в первый регистр

8.К+1 результата записывается произведение са (К, 2)X(n+K-l, m+1), Такт S+K+2. В вычислительном блоке

1.К+1 выполняется базовая операция

В, в результате которой во второй регистр 10,K+1 результата записывается сумма у (n, m), =у (n, ттт)+тд(К, 2)»

» Х(п+К-l, пт+1), а в вычислительном блоке 1,K+2 — базовая операция А, н результате которой в первый регистр

8.K+2 результата записывается произведение у (К- 1, 2)Х(п+К-2, m+1).

Такт S+K+3. В блоке 1.К+2 выполняется базовая операция В, в результате которой но второй регистр 10.К+2 результата записывается сумма у (n, m)=

=у (п, ттт)+ы(К-1, 2) X(m+K-2, m+1), а в блоке 1.К+3 — базовая операция А, в результате которой в первый регистр

8,К+3 результата записывается произ.ведением (K-2,2)Х(п+К-З, ттт+1), Такт Б+2К+1. В блоке 1,2К реализуется базовая операция В, в результате которой во второй регистр 10.2К результата записывается сумма у (и, тп) =

=у (и, m), +у (и, m)=y (n, m)„ = 1+

+и (1, 2)Х(п, тп+1), Такт S+(L-1) К+1, В вычислительном блоке 1.(L-1)K выполняется базовая операция В, в результате которой во второй регистр 10,(L-1)К результата

),-1 т записывает ся сумма у (и, m) =у (n, m) +

+у (тп, n)+... +у (n, m). В этом же такте в вычислительном блоке 1 ° (L— 1)К+1 выполняется базовая операция

А, в результате которой н первый регистр 8 ° (L-1)К результата записывается произведение у (К, L)X(n+K-l, m+L--1).

Такт S+(1.-1)K+2. В блоке 1,(L-1)x

«К+1 выполняется базовая операция В, в результате которой но второй регистр 10,(Ь"1)К+1 результата записывается сумма у (пт,п) у (и, m)„+

+ ц(К, L)X(n+K-l, m+L-l), а в блоке

1,(L-1)К+2 реализуется базовая операция А, в результате которой в первый регистр 8,(L-1)К+2 результата записывается произведение тт (К-п, К)» к X(m+K-2), пт+Т;1) .

Такт S+L. К+1. В вычислительном блоке 1.К L выполняется базовая операция В, в результате которой ао.второй регистр 10.К L результата записывается окончательное значение y(n, m), от куда в следующем т акт е по ступает на информационный вход блока 2 регистров ° Таким же образом протекает работа устройства, при обработке тех отсчетов входного массива X(n,m), которые удовлетворяют условию где h = 2,3...

5

f0

1I5

2 (h- l ) K+1 с: n (2h+1)K-1, Формула изобретения

Устройство для вычисления свертки, содержащее блок регистров, L коммутаторов и L групп вычислительных блоков по К блоков в каждой (К L — длина последовательности коэффициентов), причем выход блока регистров подключен к первым информационным входам первого и L-го коммутаторон, при этом каждый вычислительный блок содержит первый и второй регистры результата, сумматор, уМножитель, первый и второй буферные регистры и регистр коэффициента, выход которого подключен к входу умножителя, выход которого подключен к информационному входу первого регистра результата, выход которого подключен к первому входу сумматора, выход которого подключен к информационному входу второго регистра результата, второй вход умножителя подключен к выходу первого буферного регистра, информационный нход которого подключен к выходу второго буферного регистра, выходт первого буферного регистра и второго регистра результата К-го (K=1, К-1) вычислительного блока 1-й (1 = 1,?.) Составитель А. Баранов ю, Редактор Н. Рогулич Техред И.Попович Корректор Т, Колб

Заказ 2514/44 Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

7 13 группы подключены соответственно к информационному входу второго буферного регистра и второму входу сумматора (К+1)"ro вычислительного блока

1-й группы, выходы первого буферного регистра и второго регистра результата К-ro вычислительного блока М-й (М 1, L"I) группы подключены соответственно к первому информационному входу (M+1)-ro коммутатора и второму входу сумматора, первого вычислительного блока (М+1)-й группы, выход второго регистра результата К-го высслительного блока L-й группы под19045 8 ключен к информационному входу блока регистров, выход 1-ro коммутатора подключен к информационному входу второго буферного регистра первого вычислительного блока 1-й группы, а управляющие входы всех коммутаторов соединены между собой и являются входом задания режима работы устройства, о т л и ч а ю щ е е с я тем, f0 что, с целью упрощения устройства, выход первого буферного регистра К-го вычислительного блока (ш+1)-й группы подключен к второму информационному входу М-ro коммутатора,