Устройство для контроля полупроводниковой памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для тестового диагностирования полупроводниковой памяти. Цель изобретения - повышение быстродействия устройства контроля. Быстродействие устройства достигается благодаря сокращению числа элементов, ограничиваюш,их скорость формирования тестов. Устройство содержит блок 2 задания начальных данных, блок 3 синхронизации, формирователь 4 управляющих сигналов, блоки 5 формирования адресов, коммутатор 6 адресов , блоки 7 формирования данных, коммутатор 8 данных, ботоки 9 сравнения, элемент ИЛИ 10, коммутатор 11 команд, регистр 12 команд, регистр 13 адреса, регистр 14 данных . 10 ил. i (Л со со о со

СОЮЗ СОВЕТСКИ)(СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 G 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

Om Эаи

СО

Ж

CD сО

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3950542/24-24 (22) 02.09.85 (46) 23.06.87. Бюл. № 23 (71) Научно-исследовательский институт управляющих вычислительных машин Научнопроизводственного объединения «Им пульс» (72) В. Г. Рябцев, А. Д. Стафеев, А. Ф. Шамарин, О. П. Смалий, В. Е. Торшина, Л. И. Русс и А. И. Волох (53) 681.327 (088.8) (56) Патент США № 4402081, кл. 371/21, опублик. 1983.

Авторское свидетельство СССР № 1238164, кл. G 11 С 29/00, 1984.

„„SU„„1319079 A1 (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОЛУПРОВОДНИКОВОЙ ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано для тестового диагностирования полупроводниковой памяти. Цель изобретения — повышение быстродействия устройства контроля.

Быстродействие устройства достигается благодаря сокращению числа элементов, ограничивающих скорость формирования тестов.

Устройство содержит блок 2 задания начальных данных, блок 3 синхронизации, формирователь 4 управляющих сигналов, блоки 5 формирования адресов. коммутатор 6 адресов, блоки 7 формирования данных, коммутатор 8 данных, блоки 9 сравнения, элемент

ИЛИ 10, коммутатор 11 команд, регистр 12 команд, регистр !3 адреса, регистр 14 данных. 10 ил.

1319079

Изобретение относится к вычислительной технике и может быть использовано для тестового диагностирования полупроводниковой памяти.

Цель изобретения — повышение быстродействия устройства.

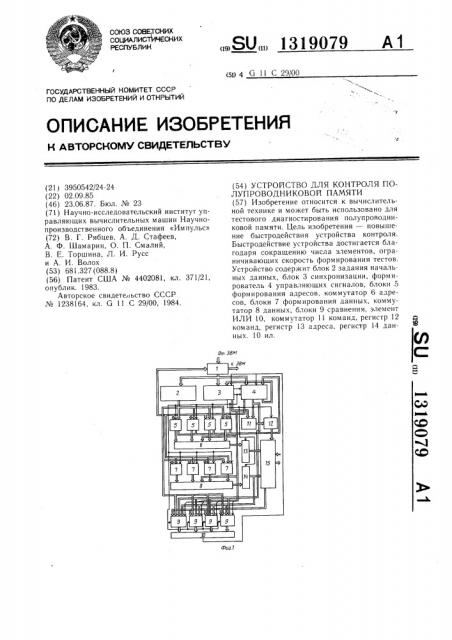

На фиг. 1 приведена функциональная схема устройства для контроля полупроводниковой памяти; на фиг. 2 — функциональная схема блока управления; на фиг. 3 — функциональная схема блока задания начальных данных; на фиг. 4 — функциональная схема блока формирования адреса; на фиг. 5— функциональная схема блока адреса; на фиг. 6 — функциональная схема блока коммутации адреса; на фиг. 7 — функциональная схема блока формирования данных; на фиг. 8 — функциональная схема блока сравнения; на фиг. 9 — функциональная схема блока синхронизации; на фиг. 10 — функциональная схема блока связи с ЭВМ.

Устройство (фиг. 1) содержит блок 1 связи с ЭВМ, блок 2 задания начальных данных, блок 3 синхронизации, формирователь 4 управляющих сигналов, блоки 5 формирования адресов, коммутатор 6 данных, блоки 7 формирования данных, коммутатор 8 адресов, блоки 9 сравнения, элемент ИЛИ 10 коммутатор 11 команд, регистр 12 команд, регистр 13 адреса, регистр 14 данных и блок 15 сопряжения, к которому подключается блок контролируемой памяти (не показан).

Формирователь 4 (фиг. 2) содержит коммутаторы 16 — 18, элемент ИЛИ 19, счетчик 20 микрокоманд, микропрограммное оперативное запоминающее устройство 21, регистры 22 кода операций, дешифратор 23 микрокоманд, программные счетчики 24.

Блок 2 задания начальных данных (фиг. 3) содержит регистр 25 блокировки сравнения считанных и контрольных данных, регистр 26 хранения начального кода блоков формирования данных, регистр 27 начального адреса контролируемой памяти, регистр 28 конечного адреса контролируемой памяти, регистр 29 кода подматриц контролируемой памяти, элементы ИЛИ 30.

Блок 5 формирования адресов (фиг. 4) содержит. элементы И 31, блоки 32 адреса, обеспечивающие выбор строк, столбцов и микросхем контролируемой памяти, блоки 33 сравнения, блоки 34 коммутации адреса, регистры 35 — 37, предназначенные для хранения кодов адреса строк, столбцов и микросхем памяти соответственно.

Блок 32 адреса (фиг. 5), входящий в блок 5 формирования адресов, содержит регистр 38, элемент И 39, коммутатор 40, комбинационные блоки 41 — 48 и коммутатор 49.

Блок 34 коммутации адреса (фиг. 6), входящий в блок 5 формирования адреса (фиг. 4) содержит элементы 50 И и элементы ИЛИ 51.

10 15

Блок 7 формирования данных (фиг. 7) содержит регистр 52, комбинационные блоки 53 — 57, коммутатор 58, регистр 59.

Блок 9 сравнения (фиг. 8) состоит из регистра 60 эталонных данных, элементов

И-ИЛИ-НЕ 61, регистра 62 хранения считанных данных и регистра 63 результатов диагностирования.

Блок 3 синхронизации (фиг. 9) состоит из генератора 64, блока 65 задержки, элемента НЕ 66, генератора 67 одиночных импульсов, делителя 68 на четыре, триггеров

69 — 72, элемента И-НЕ 73, элемента ИЛИНЕ 74, дешифратора 75, элемента 76 И.

Блок 1 связи с ЭВМ (фиг. 10) содержит коммутатор 77, дешифратор 78, элементы

НЕ 79 и элемент И-HE 80.

Конкретный пример структуры устройства (фиг. 1) содержит группы из четырех одноименных блоков 5 формирования адресов, блоков 7 формирования данных и блоков 9 сравнения.

Перед началом работы устройства (фиг. 1) в блок 2 через блок 1 от внешней управляющей ЭВМ заносятся: в регистр 25 — число разрядов контролируемой памяти (1), в регистр 26 — начальный код блоков формирования данных, в регистр 27 — начальный адрес контролируемой памяти, в регистр 28— конечный адрес контролируемой памяти, в регистр 29 — номер подматрицы контролируемой памяти. Устанавливается частота работы генератора 64 и время выборки информации в блоке 65 задержки. В микропрограммное запоминающее устройство 21 заносится программа работы устройства.

Начальный адрес программы заносится в счетчик 20 микрокоманд.

Запись исходных данных и программы работы устройства осуществляется внешней управляющей ЭВМ следующим образом.

От ЭВМ на входы дешифратора 78 поступает первая группа управляющих сигналов, которая определяет тип выбранного регистра 25 — 29.

Информация от ЭВМ поступает на входы элементов НЕ 79.

Вторая группа управляющих сигналов поступает на входы элемента И-НЕ 80 и используется для формирования стробирующего сигнала дешифратора 78.

Управляющие сигналы, поступающие от

ЭВМ, на выходе дешифратора 78 преобразуются в сигнал «Общий сброс», который переводит в исходное состояние триггеры

69 — 72. При другой комбинации управляющих сигналов ЭВМ формируется сигнал

«Пуск», поступающий на вход генератора 67 одиночных импульсов, который формирует импульс, переключающий триггер 70 в единичное состояние.

Частота выходного сигнала генератора

64 уменьшается в четыре раза при помощи

1319079 делителя 68 и на выходе элемента И 76 формируются тактовые импульсы, обеспечивающие синхронизацию работы формирователя 4. При помощи счетчика 20 микрокоманд из микропрограммного оперативного запоминающего устройства 21 выбираются микрокоманды, которые определяют функции, выполняемые основными блоками устройства.

Блоки 5 формирования адресов содержат блоки 32 адреса, которые при помощи комбинационных блоков 41 — 48 и коммутатора 49 могут инвертировать данные, увеличивать код адреса на единицу, уменьшать код адреса на единицу, увеличивать код адреса на два, уменьшать код адреса на два, увеличивать код адреса на три, увеличивать код адреса на четыре, уменьшать код адреса на четыре, осушествлять сдвиг кода адреса вправо на один разряд.

Блоки 7 формирования данных могут при помощи комбинационных блоков 53 — 57 и коммутатора 58 инвертировать данные, увеличивать код данных на четыре, увеличивать код данных на единицу, уменьшать код данных на единицу, уменьшать код данных на четыре, сдвигать вправо на один разряд код данных.

В блоки 5 формирования адресов заносят начальный адрес проверяемой микросхемы. Затем код второго блока 5 увеличивают на единицу, третьего блока — на два, четвертого блока — на три. В блоки 7 формирования данных заносят начальный код, который предварительно был занесен в регистр 26.

Подготовленные коды адреса передаются через коммутатор 6 на входы регистра

13, а затем на входы блока 15. Коды данных через коммутатор 8 передаются на входы регистра 14 данных. На управляющие входы коммутаторов 6, 8 и 11 поступают сигналы с выхода делителя 68, которые обеспечивают поочередную передачу кодов адреса, данных и кодов операций на контролируемую. память, подключаемую к устройству при помощи блока 15 сопряжения, который обеспечивает соединение выходных сигналов регистров 12 — 14 с входными контактами контролируемой памяти и выходных контактов этой памяти с входами блоков 9 сравнения.

При осуществлении последовательной записи информации в ячейки памяти значение кодов адреса всех четырех блоков 5 формирования адреса изменяется на четыре.

Таким образом, формируется код адреса ячеек контролируемой памяти и в них осуществляется запись информации.

Сравнение кодов адреса, формируемых блоками 32 адреса с конечным кодом адреса контролируемой памяти, осуществляют блоки 33 сравнения, сигналы с выходов

Устройство может работать в двух режимах с остановом при обнаружении однократной ошибки и остановом после выполнения всей программы контроля с индикацией результата «Годен» или «Брак». Если триггер 69 (фиг. 9) переключить в единичное состояние, то при возникновении сигнала «Ошибка» с выхода элемента ИЛИ 10 происходит блокировка формирования тактовых импульсов при помощи элемента

И вЂ” НЕ 73, формирующего при этом сигнал низкого уровня напряжения. Если триггер 69 находится в нулевом состоянии, то программа контроля выполняется полностью а сигнал выхода элемента ИЛИ 10 используется для формирования при помощи команды условного перехода, анализирующей результаты диагностирования, сигналов

«Годен» или «Брак». При этом переключается в единичное состояние триггер 71 или триггер 72 и осуществляется сигнализация результатов контроля. Сигналы с прямых выходов триггеров 71 и 72 включают элементы индикации (не показаны) и через элемент ИЛИ вЂ” НЕ 74 переключают триггер 70 в нулевое состояние, при этом блокируется формирование тактовых импульсов формируемых элементом И 76.

55 которых поступают на входы коммутатора

16 и используются для реализации микрокоманд условного перехода. Выбор номера блока 5, сигналы сравнения которого необходимо использовать, осуществляется при помощи отдельного операционного поля микрокоманды. Код микрокоманды условного перехода поступает на входы- коммутатора 18, сигнал с выхода которого обеспечивает запись в счетчик 20 микрокоманд, кода адреса перехода, поступающего через коммутатор 17 на входы счетчика 20 микрокоманд, а при сравнении кода блоков

32 адреса с конечным кодом адреса контролируемой памяти содержимое счетчика

20 микрокоманд увеличивается на единицу.

Управляющие сигналы «Запись», «Считывание» и «Сравнение» запоминаются в регистрах 22 кода операций и через коммутатор 11 передаются на входы регистра 12.

Данные с выходов контролируемой памяти через блок 15 поступают на входы регистра 62 хранения считанных данных.

Запись данных осуществляется при помощи стробов, формируем ых дешифратором 75. В регистр 60 эталонных данных заносят контрольные данные с выходов регистра 14.

Сравнение считанных и эталонных данных осуществляется элементами И вЂ” ИЛИ—

НЕ 61. Результаты контроля заносятся в регистр 63 (фиг. 8) . Сигналы с выходов блоков 9 сравнения объединяются на входах элемента ИЛИ 10 и используются для анализа результатов контроля.

1319079

Формула изобретения

Для задания числа циклов выполнения программы контроля и формирования различных алгоритмических последовательностей тестов используются программные регистры 24 (фиг. 2), в которые по микрокомандам занесения формируемых дешифратором 23 вначале заносят число циклов выполнения программы, а затем по микроком андам условного перехода осуществляется уменьшение содержимого данных счетчиков 24, сигналы переносов с выхода которых используются для управления работой счетчика 20 м икроком анд.

Сигналы с выхода микропрограммного оперативного запоминающего устройства

21 передаются для контроля во внешнюю управляющую ЭВМ при помощи коммутатора 77 (фиг. 10). Объем контролируемой полупроводниковой памяти можно разделять на подматрицы, номер которой заносится в регистр 29 (фиг. 3), при этом в регистр 28 конечного адреса заносится число, равное полному объему памяти, деленное на число подматриц. Сигналы с выходов регистра 28 конечного адреса через элементы ИЛИ 30 поступают на первые входы элементов И 50 (фиг. 6) и обеспечивают передачу данными элементами сигналов с выходов адресного блока 32. На элементах

ИЛИ 51 объединяются сигналы с выходов элементов И 50 и с выходов регистра 29 кода подматриц. Разделение контролируемой памяти на подматрицы повышает производительность контроля устройства, особенно и ри выполнении тестов, продолжительность которых пропорциональна квадрату числа контролируемых ячеек памяти.

Устройство для контроля полупроводниковой памяти, содержащее блок синхронизации, блок задания начальных данных„ коммутатор данных, блоки формирования данных, блоки сравнения, элемент ИЛИ, причем выходы блока задания начальных данных подключены к входам первой группы блоков сравнения и блоков формирования данных, выходы которых соединены с информационными входами коммутатора данных, управляющие входы которого соединены с выходами группы блока синхронизации, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блоки формирования адресов, коммутатор адресов, коммутатор команд, регистр команд, регистр адреса, регистр данных, формирователь управляющих сиг5 !

О

l5

Зо

50 налов, причем выход блока задания начальных данных подключены к входам первой группы блоков формирования адресов, входы второй. группы которых и входы второй группы блоков формирования данных подключены к выходам первой группы формирователя управляющих сигналов, выходы второй группы которого соединены с входами второй группы блоков сравнения и одними из входов коммутатора команд, другие входы которого соединены. с выходами группы блока синхронизации, выходы коммутатора команд соединены с информационными входами регистра ком анд, выходы первой группы блоков формирования адресов подключены к информационным входам коммутатора адресов, управляющие входы которого соединены с выходами группы блока синхронизации, выходы коммутатора адресов и коммутатора данных подключены соответственно к информационным входам регистра адреса и регистра данных, выходы которого соединены с входами третьей группы блоков сравнения, выходы которых подключены к входам элемента ИЛИ, выход которого соединен с входом останова формирователя управляющих сигналов и входом блока синхронизации, первый выход блока синхронизации соединен с входом пуска формирователя управляющих сигналов, второй выход блока синхронизации соединен с синхровходами формирователя управляющих сигналов, блоков формирования адресов, блоков формирования данных и блоков сравнения, третий выход блока синхронизации подключен к синхровходам регистра команд, регистра адреса и регистра данных, выходы второй группы блоков формирования адресов подключены к входам первой группы формирователя управляющих сигналов, выходы третьей группы которого соединены с входами первой группы блока синхронизации, выходы регистра адреса и регистра данных и входы четвертой группы блоков сравнения являются соответственно адресным и информационным выходами и информационным входом устройства, управляющие входы блоков сравнения соединены с выходами группы блока синхронизации, выходы регистра команд и выходы первой группы формирователя управляющих сигналов являются управляющими выходами устройства, управляющими входами которого являются входы блока задания начальных данных и входы второй группы блока синхронизации и формирователя управляющих сигналов.

1319079

0m 5

От1

0m 7

Om

Фиг. Я фиг. 5

0m 3 От 4 0m 2

Фиг. 4

1319079

Фиг. 5

Ъ2 &ай

0m 5 DmФ

От д

0m к 70 к8

Йл5

1319079

Om1

4,579

От

Фиг. 9

Z3O

Составитель В. Рудаков

Редактор Г. Волкова Техред И. Верес Корректор А. Ильин

Заказ 2517/46 Тираж 589 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4