Триггер

Иллюстрации

Показать всеРеферат

Изобретение относите к импульсно технике и может быть иснользовано и микроэлектронных сжтемах цифрово автоматики и вычислительной техники. Цель изобретения - уменьшение потребляемой MOIUHOC- ти триггера. Устро(1ство содержит транзисторы второго типа ироводимости 2. 7, 9, 12. Для достижения поставлеииой цели в устрой ство введены резистор 14 и новые связи. 1 ил. t6. Юо оо кгк; Ю Сл

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1319253 А 1 (у 4 Н 03 К 3/286

7 ф

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4012279/24-21 (22) 27.01.86 (46 ) 23.06.87. Бюл. ¹ 23 (72) С. В. Касаткин, И. И. Лавров, В. И. Громов и П. В. Ястребов (53) 621.374 (088.8) (56) Авторское свидетельство СССР № 970652, кл. Н 03 К 3/286, 1981.

Авторское свидетельство СССР № 843177, кл. Н 03 К 3/286, 1979. (54) ТРИ ГГЕ Р (57) Изобретение относит«" и импульсной текнике и может быть и«пользовано и микроэлектрîIIíûx системаx цифровой автоматики и вычислительной техники. Цель изобретения — — уменьшение потребляемой мои но«ти триггера. Устройство содержи г транзисторы второго типа проводимости 2, . 9, 12, Для достижения поставленной iL«,1и H у«трой ство введены резистор 14 и новые связи.

1 ил.

1319253

Изобретение относится к импульсной технике и предназначено для использования в микроэлектронных системах цифровой автоматики и вычислительной техники.

Цель изобретения — уменьшение потребляемой мощности триггера.

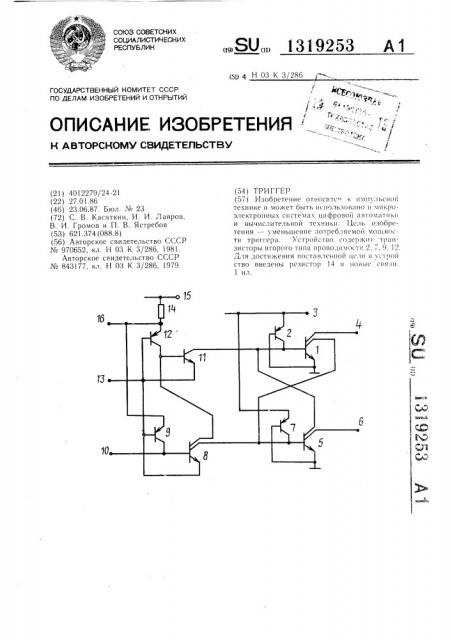

На чертеже представлена принципиальная электрическая схема триггера.

Триггер содержит первый транзистор 1 первого типа проводимости, база которого подключена к коллектору первого транзистора 2 второго типа проводимости, эмиттер которого подключен к первой шине

3 питания, а база — к общей шине и эмиттеру транзистора 1, первый коллектор которого подключен к первому выходу 4 триггера, а второй коллектор — к базе второго транзистора 5 первого типа проводимости, первый коллектор которого подключен к базе транзистора 1, второй коллектор — к второму выходу 6 триггера, а эмиттер — к общей шине и базе второго транзистора 7 второго типа проводимости, эмиттер которого подключен к шине 3, а коллектор — к базе транзистора 5 и первому коллектору третьего транзистора 8 первого типа проводимости, эмиттер которого подключен к базе третьего транзистора 9 второго типа проводимости, коллектор которого подключен к первому входу 10 триггера и базе транзистора 8, второй коллектор которого подключен к базе четвертого транзистора 11 первого типа проводимости, коллектор которого подключен к базе транзистора 1, а эмиттер — к базе четвертого транзистора 12 второго типа проводимости, эмиттеры транзисторов 8 и 11 подключены к второму входу 13 триггера, а эмиттеры транзисторов 9 и 12 через резистор 14 — к второй шине 15 питания и третьему входу 16 триггера.

Триггер работает следующим образом.

Вход 10 является информационным входом триггера (D-вход). Входы 13 и 16 используются в качестве входа синхросигнала (C-вход) и входа управления записью информации (R-вход).

Рассмотрим работу триггера, когда в качестве входа синхросигнала используется вход 13, а в качестве входа управления— вход 16, и на все входы триггера сигналы подаются с вентилей, у которых выходом является открытый коллектор транзистора первого типа проводимости.

Когда на входе 16 присутствует сигнал логической «1» (управляющий этим входом транзистор закрыт), триггер работает в режиме разрешения записи информации. Запись новой информации в триггер производится при подаче на вход 13 сигнала логического «О» (управляющий этим входом транзистор находится в режиме насыщения) .

Так как базы транзисторов 9 и 12 закорочены через управляющий транзистор на общую шину, то транзисторы 9 и 12 от45

50 входом 16, т. е. эмиттеры транзисторов 9 и 12 оказываются закороченными на общую шину, и транзисторы 9 и 12 при любом сигнале на входе 13 закрыты, базы транзисторов 8 и 11 обесточены, транзисторы 8 и 11 поэтому закрываются, и информация с входа 10 не влияет на состояние транзисторов 1 и 5. Триггер хранит информациюю.

Уменьшение потребляемой мощности предлагаемого триггера достигается за счет отключения тока транзисторов 9 и 12 при значении сигнала логической «1» на входе 13, а также за счет сокращения количества вентилей типа И-Л, крыты. При этом, если на входе 0 присутствует сигнал логической «!», то транзистор 8 открыт, а токи его коллекторов обеспечивают закрывание транзисторов 5 и 11 ответвлением коллекторных токов транзисторов 7 и 12. На выходе 6 и на базе транзистора 1 устанавливается сигнал логической «1», транзистор открывается, на выходе 4 и на базе транзистора 5 устанавливается сигнал логического «О».

Пары транзисторов 1, 2 и 5, 7 соответственно работают как инжекционные вентили и образуют бистабильную ячейку.

Токи транзисторов 2 и 7 задаются шиной 3 тока питания. Если на вход 10 подан сигнал логического «О», то коллекторный ток транзистора 9 ответвляется в управляющий входом 10 транзистор, транзистор 8 закрыт. Ток коллектора транзистора 12 поступает в базу транзистора 11, последний открыт, его коллекторный ток

20 ответвляет ток коллектора транзистора 2.

Транзистор 1 закрывается, на выходе 4 и на базе транзистора 5 устанавливается сигнал логической «1». Транзистор 5 открывается, на выходе 6 и на базе транзистора 1 устанавливается сигнал логического «0».

При поступлении на вход 13 сигнала логической «1» транзисторы 9 и 12 переходят в режим с оторванными базами, а транзисторы 1! и 8 — — в режим с оторванными эмиттерами, т. е. происходит закрывание транзисторов 8, 9, 11 и 12. Транзисторы 8 и 11 не влияют на состояние транзисторов 1 и 5. Так как транзисторы

8 и 9 закрыты, то информация с входа 10 не влияет на- состояние транзисторов 1

35 и 5. Триггер из режима записи переходит в режим хранения информации.

Запрет записи информации по входу 16 осуществляется подачей на этот вход сигнала логического «О». При этом эмиттерный ток транзисторов 9 и 12, который равен удвоенному значению тока питания одного инжекционного вентиля (т. е. тока эмиттера транзистора 2 или транзистора 7) и задается резистором !4 и значением напряжения шины 15, ответвляется управляющим

1319253 з

Форл1ула изобретения

Составитель А. Янов

Техред И. Верес Корректор А. Зимокосов

Тираж 901 Подписное

Редактор О. Юрковецкая

Заказ 2529/54

В11ИИ13И Государственного комитета СССР по делам изобретении и открытий

113035, Москва, Ж вЂ” 35, Раушская. наб., д. 4/5

Г!роизводственно-полиграфическое предприятие. г. Ужгород. ул. Просктная, 4

Триггер, содержащий первый транзистор первого типа проводимости, база которого подключена к коллектору первого транзистора второго типа проводимости, эмиттер которого подключен к первой шине питания, а база — к общей шине и эмиттеру первого транзистора первого типа проводимости, первый коллектор которого подключен к первому выходу триггера, а второй коллектор — к базе второго транзистора первого типа проводимости, первый коллектор которого подключен к базе первого транзистора первого типа проводимости, второй коллектор — к второму выходу триггера, а эмиттер — к общей шине и базе второго транзистора второго типа проводимости, эмиттер которого подключен к первой шине питания, а коллектор — к базе второго транзистора первого типа проводимости и первому коллектору третьего транзистора первого типа проводимости, эмиттер которого подключен к базе третьего тра нзистора второго типа проводимости, коллектор которого подключен к первому входу триггера и базе третьего транзистора первого типа проводимости, второй коллектор которого подключен к базе четвертого транзистора первого тирпа проводимости, коллектор которого подключен к базе первого транзистора первого типа проводимости, а эмиттер —— к базе четвертого транзистора второго типа проводимости, эмиттер которого соединен с эмиттером третьего транзистора второго типа проводимости, а коллектор — с базой четвертого транзистора первого типа проводимости, эмиттер которого соединен с эмиттером третьего транзистора первого типа проводимости, отличающийся тем, что, с целью уменьшения потребляемой мощности, в него введены третий вход, вторая шина питания и резистор, при этом эмиттер третьего транзистора первого тина проводимости подключен к второму входу триг20 гера, а эмиттер третьего транзистора второго типа проводимости подключен к третьему входу триггера и через резистор к второй шине питания.