Устройство для селекции сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и обеспечивает повышение точности селекции . Устройство содержит АЦП 1, блок 2 инверторов в составе инверторов 2i-2k, элементы И-НЕ 3, 5, 6, 8, 9, 13 и 15, триггеры 4, 7 и 14, элемент ИЛИ-НЕ 10, инверторы 11 и 12, счетчики 16-19, блок 20 памяти , генератор 21 тактовых импульсов. 2 ил. Фиг.1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„Я0„„1319285 А 1 (gg 4 н о4 в l/10, н оз н 17/оо

ОПИСАНИЕ ИЗОБРЕТ

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

Фиг.1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4025304/24-09 (22) 21.02.86 (46) 23.06.87. Бюл. № 23 (71) Научно-исследовательский институт прикладной математики и механики при Томском государственном университете им. В. В. Куйбышева (72) Н. П. Бекетов (53) 621.391.837:621.3(088.8) (56) Авторское свидетельство СССР № 598255, кл. Н 04 В 1/10, 1978. (54) УСТРОЙСТВО ДЛЯ СЕЛЕКЦИИ СИГ

НАЛОВ (57) Изобретение относится к радиотехнике и обеспечивает повышение точности селекции. Устройство содержит АЦП 1, блок 2 инверторов в составе инверторов 21 — ? „, элементы И вЂ” HE 3, 5, 6, 8, 9, 13 и 15, триггеры 4, 7 и 14, элемент ИЛИ вЂ” НЕ 10, инверторы 11 и 12, счетчики 16 — 19, блок 20 памяти, генератор 21 тактовых импульсов. 2 ил.

1319285

Формула изобретения

Изобретение относится к радиотехнике и может быть использовано в системах цифровой фильтрации для селекции сигналов в условиях помех в виде одиночных или пачек кратковременных импульсов, сравнимых по амплитуде с полезным сигналом.

Цель изобретения — повышение точности селекции.

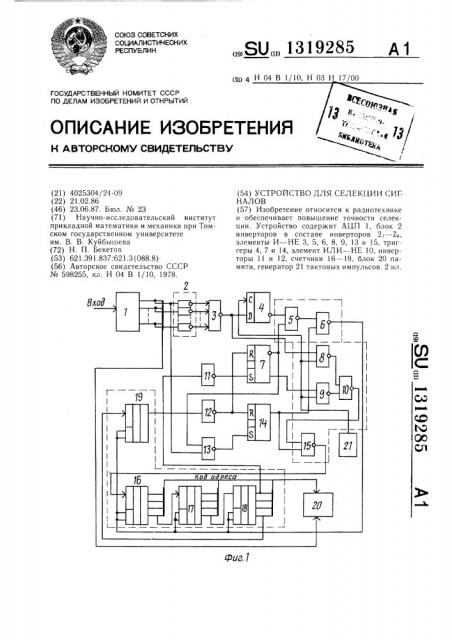

На фиг. 1 приведена электрическая структурная схема устройства для селекции сигналов; на фиг. 2 — временные диаграммы, поясняющие его работу.

Устройство для селекции сигналов содержит аналого-цифровой преобразователь (АЦП) 1, блок 2 инверторов в составе инверторов 2 1 — 2 К, первый элемент И вЂ” НЕ 3, первый триггер 4, второй 5 и третий 6 элементы И вЂ” НЕ, второй триггер 7, четвертый 8 и пятый 9 элементы И вЂ” НЕ, элемент

ИЛИ вЂ” HE 10, первый 11 и второй 12 инверторы, шестой элемент И вЂ” НЕ 13, третий триггер !

4, седьмой элемент И вЂ” HE 15, первый 16, второй 17, третий 18 и четвертый 19 счетчики, блок 20 памяти и генератор 21 тактовых импульсов.

Устройство для селекции сигналов работает следующим образом.

В исходном положении первый 4 и третий 14 триггеры устанавливаются в нулевое состояние, генератор 21 тактовых импульсов подает синхроимпульсы на вход С первого триггера 4 и на вторые входы четвертого 8 и пятого 9 элементов И вЂ” НЕ

Электрический сигнал (фиг. 2 а и з) поступает на вход АЦП 1, преобразуется в цифровой код и через блок 2 инверторов поступает на вход первого элемента И вЂ” HE 3.

Выход первого элемента И вЂ” НЕ 3 соединен с информационным входом первого триггера

4. Триггер 4 интегрирования сигнала синхроимпульсами, поступающими на его вход синхронизации, устанавливается в единичное состояние и находится в нем, пока с выхода первого элемента И вЂ” HE 3 поступает единичный сигнал (фиг. 2 б и н).

На выходе первого элемента И вЂ” HE 3 единичный сигнал присутствует все время, пока с выхода АЦП 1 поступает информация хотя бы с одного из разрядов. При отсутствии такой информаци (т.е. тот случай, когда сигнала на выходе АЦП 1 нет совсем) первый триггер 4 устанавливается в нулевое состояние (фиг. 2 в и к). В течение определенного времени (время устанавливается подключением первого инвертора 11 к выходу третьего счетчика 18, определяющего контрольное время) первый триггер

4 своим инверсным выходом через второй

5 и третий 6 элементы И вЂ” HE, разрешает счет импульсов первому 16, второму 17, третьему 18 и четвертому 19 счетчикам в случае, если с прямого выхода третьего триггера 14 поступает единичный сигнал на . третий элемент И вЂ” HE 6.

ЗО

Третий триггер 14 устанавливается в единичное состояние при наличии сигнала с одного из разрядов АЦП 1, если нет запрета с выхода второго триггера 7. На фиг. 1 подключен первый разряд АЦП 1, но при большом уровне шумов можно минимальный уровень сигналов повысить, подключая более старший разряд. Второй триггер 7 устанавливается в единичное состояние через определенное время сигналом с выхода четвертого счетчика 19 через первый инвертор 11.

Сигнал с инверсного выхода второго триггера 7 разрешает продолжение записи во второй 5 и третий 6 элементы И вЂ” НЕ. Если сигнал на входе АЦП 1 непрерывен в течение контрольного времени, то первый триггер 4 находится в единичном состоянии. Нулевой уровень с инверсного выхода триггера 4 через второй 5 и третий 6 элементы И вЂ” HE разрешает счет импульсов. В случае прерывания сигнала на в-оде АЦП 1, т.е. когда присутствует импульсная помеха, первый триггер 4 устанавливается в нулевое состояние (фиг. 2 и и к), сбрасывая содержимое первого 16, второго 17, третьего 18 и четвертого 19 счетчиков. Поэтому импульсная помеха, длительность которой меньше контрольного времени, не записывается в блок 20 (фиг. 2 е) .

Когда на входе АЦП 1 присутствует полезный сигнал и после того как проходит заданное контрольное время, второй триггер 7 устанавливается в единичное состояние сигналом от третьего счетчика 18 (фиг. 2 г и л) через первый инвертор 11.

Нулевой уровень с инверсного выхода второго триггера 7 (фиг. 2 д и м) через второй 5 и третий 6 элементы И вЂ” НЕ, продолжает разрешение счета импульсов до тех пор, пока на выходе четвертого счетчика

19 не устанавливается единичный сигнал, который через второй инвертор 12 устанавливает третий триггер 14 в нулевое состояние, заканчивая запись информации.

При появлении помехи на входе устройства первый триггер 4 устанавливается в единичное состояние только на время длительности помехи, которое меньше заданного контрольного времени. Поэтому первый

16, второй 17, третий 18 и четвертый 19 счетчики сбрасываются сразу же по концу импульсной помехи, стирая информацию в блоке 20 (фиг. 2 ж и н). Так как длительность полезного сигнала превышает контрольное время, то срабатывает второй триггер 7, разрешая продолжение записи информации.

Устройство для селекции сигналов, содержащее аналого-цифровой преобразователь, блок памяти, генератор тактовых импульсов и первый счетчик, отличающееся

1319285

1 а фиг. Г

Составитель Э. Борисов

Редактор И. Шулла Техред И. Верес Корректор А Обручар

Заказ 2532/56 Тираж 638 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 7К вЂ” 35, Раушская наб., д. 4 5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Г1роектная, 4 тем, что, с целью повышения точности селекции, введены последовательно соединенные блок инверторов, вход которого соединен с выходом аналого-цифрового преобразователя, первый элемент И вЂ” НЕ, первый триггер, второй элемент И вЂ” НЕ и третий элемент И вЂ” НЕ, выход которого соединен с первым входом первого счетчика и объединен с первыми входами введенных второго, третьего и четвертого счетчиков, последовательно соединенные первый инвертор, вход которого соединен с первым выходом третьего счетчика и второй триггер, выход которого соединен с вторым входом второго элемента И вЂ” НЕ, последовательно соединенные второй инвертор, вход которого соединен с выходом четвертого счетчика, и третий триггер, выход которого соединен с вторым входом третьего элемента И вЂ” НЕ, последовательно соединенные четвертый элемент И вЂ” НЕ, первый вход которого соединен с выходом первого элемента И вЂ” НЕ, и элемент ИЛИ вЂ , второй вход которого через введенный пятый элемент И вЂ” НЕ соединен с вторым выходом второго триггера, шестой элемент И вЂ” НЕ, первый и второй входы которого соединены с выходом первого разряда аналого-цифрового преобразователя и первым выходом второго триггера соответственно, а выход соединен с вторым входом третьего триггера, а также седьмой элемент И вЂ” HE, первый и второй входы которого соединены с выходами третьего триггера и элемента ИЛИ вЂ” НЕ соответственно, а выход соединен с вторым вхо10 дом первого счетчика, при этом выход генератора тактовых импульсов соединен с вторыми входами первого триггера и четвертого и пятого элементов И вЂ” НЕ, первый и второй входы блока памяти соединены с

15 выходом аналого-цифрового преобразователя, с первыми выходами первого и второго счетчиков и с вторым выходом третьего счетчика, третий выход которого соединен с вторым входом четвертого счетчика, второй выход первого счетчика соединен с вторым

20 входом второго счетчика, второй выход которого соединен с вторым входом третьего счетчика, а выход второго инвертора соединен с вторым входом второго триггера.