Обнаружитель комбинаций двоичных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи. и,ель изобретения - уменьшение времени обнаружения комбинаций в скоростных потоках сигналов. Устр-во содержит регистр сдвига информации 1, многоканальный коммутатор 2, п эл-тов И 3i-Зп. Вновь введены переключатель 4 кодов комбинаций, блок 5 компараторов. 1 ил. гттт со со ОО to

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„SUÄÄ 1319327 А 1 д11 4 Н 04 Q 5/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3977732/24-09 (22) 20.11.85 (46) 23.06.87. Бюл. № 23 (72) В. Н. Деев, К. Л. Осинов и С. Е. Солнцев (53) 621.391.84 (088.8) (56) Патент США № 3346844, кл. Н 04 Q 5/16, 1967.

Авторское свидетельство СССР № 987859, кл. Н 04 Q 5/16, 1983. (54) ОБНАРУЖИТЕЛЬ КОМБИНАЦИЙ

ДВОИЧНЫХ СИГНАЛОВ (57) Изобретение относится к технике связи.

Цель изобретения — уменьшение времени обнаружения комбинаций в скоростных потоках сигналов. Устр-во содержит регистр сдвига информации 1, многоканальный коммутатор 2, и эл-тов И 3 — 3.. Вновь введены переключатель 4 кодов комбинаций, блок 5 компараторов. 1 ил.

1319327

Формула изобретения

Составитель В. Грачев

Редактор Н. Тупица Техред И. Верес Корректор В. Бутяга

Заказ 2535/58 Тираж 638 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Г!ронзводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Изобретение относится к технике связи и может быть использовано в приемных устройствах для обнаружения комбинаций двоичных сигналов известного типа при неизвестном моменте прихода.

Цель изобретения — уменьшение времени обнаружения комбинаций в скоростных потоках, сигналов.

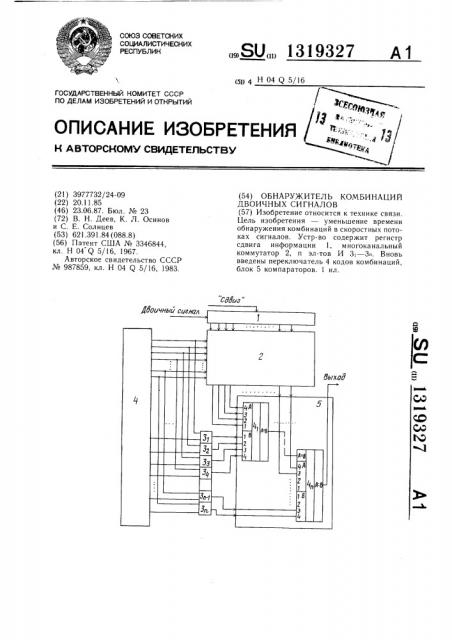

На чертеже приведена электрическая стрф урная схема обнаружителя комбинаций двоичны ЬитHBJIoB.

Обнаружитель комбинаций двоичных сиг. налов содф)кит регис1тр 1 сдвига информации, "муоГа каЪальщ1й- коммутатор 2, п эле ментов-Й Si ....Зп, переключатель 4 кодов комбинаций, блок< компараторов. . Обна ужите 1ь|комбинации двоичных сигналов рфготает следующим образом.

Двоичный сигнал с уровнем логического

«0» или «1» поступает на вход регистра 1 сдвига информации, служащего для преобразования последовательного двоичного кода в параллельный, на другой вход регистра 1 сдвига информации поступает тактовый сигнал, вырабатываемый устройством выделения тактовой частоты (не показан). с выходов регистра 1 сдвига информации двоичный сигнал в параллельном коде поступает на первые и входов многоканального коммутатора 2.

Многоканальный коммутатор 2 содержит п каналов пропускания, управляемых с выходов переключателя 4 кодов комбинаций, который служит для исключения из анализа битов двоичной информации, логические состояния которых не определены (бит служебной информации). Положение этих битов в двоичной комбинации может изменяться по заданной программе и задается логическим «0» с соответствующего разряда переключателя 4 кодов комбинаций, при этом на выходе соответствующего данному разряду каналу пропускания многоканального коммутатора 2 устанавливается состояние логического «0» независимо от того; как меняется логическое состояние битов служебной информации в обнаруживаемой двоичной комбинации. На всех остальных выходах переключателя 4 кодов комбинаций устанавливается состояние логической «1».

Двоичные сигналы с выхода многоканального коммутатора 2 поступают на входы

А соответствующих разрядов линейки цифровых компараторов блока 5 компараторов. Потенциалы логического «0» или «1», опре5

25 деляющие вид обнаруживаемой комбинации, с вторых выходов переключателя 4 кодов комбинаций поступают на вторые входы соответствующих п элементов И Зь..3п

На первые входы п элементов И 3I...3n поступают потенциалы логического «О» или «1» с первых выходов переключателя 4 кодов комбинаций. Положение служебного бита определяется потенциалом логического «О» на первом входе одного из п элементов

И Зь..Зп соответствующего разряда. Вид обнаруживаемой комбинации может изменяться по заданной программе.

С выходов п элементов И 3 ...3n логические потенциалы обнаруживаемой двоичной комбинации поступают на входы В соответствующих разрядов цифровых компараторов блока 5 компараторов.

При равенстве двоичных чисел на входах А и В (совпадении двоичных комбинаций) на выходе переноса по знаку «А» компаратора старших разрядов блока 5 компараторов появляется потенциал логической «1». При сдвиге на один разряд двоичной комбинации равенство нарушается и на выходе обнаружителя комбинаций двоичных сигналов формируется положительный импульс совпадения в один тактовый интервал, определяющий положение и вид обнаруживаемой комбинации в потоке двоичной информации.

Обнаружитель комбинаций двоичных сигналов, содержащий регистр сдвига информации, и выходов которого соединены соответственно с первыми п входами многоканального коммутатора, а также п элементов И, отличающийся тем, что, с целью уменьшения времени обнаружения комбинаций в скоростных потоках сигналов, введены переключатель кодов комбинаций и блок компараторов, при этом первые и выходов переключателя кодов комбинаций соединены соответственно с вторыми п входами многоканального коммутатора и первыми входами п элементов И, а вторые входы и элементов И соединены соответственно с вторыми п выходами переключателя кодов комбинаций, п выходов многоканального коммутатора соединены соответственно с первыми п входами блока компараторов, вторые п входов которого соединены соответственно с выходами и элементов И.