Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для микропрограммного управления. Цель изобретения - повышение быстродействия устройства. Микропрограммное устройство, управления содержит блок 1 памяти микрокомацц, регистр 2 адреса, регистр 3 логических условий, блок 4 задержки. Указанная цель достигается с помощью указанной совокупности блоков. 2 .ил. о I

СОВХОЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (5В 4 С 06 Р 9, 22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

« »

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3967695/24-24 (22) 21.10.85 (46) 30.06.87. Бюл. Р 24 (71) Могилевский машиностроительный институт (72) Г.В.Бочкарев. Н.А.Вислович, Г.В.Куклин и С.А.Яковлев (53) 681.3(088.8) (56) Горяшко А.П. Логические схемы и реальные ограничения, методы синтеза, оценка сложности, М.: Энергоиздат, 1982, с. 49, рис. 2 6.

Хассон С. Микропрограммное управление, М.: Мир, 1973, с. 39, рис.2.1.

Я0; И29ИЩ А 1 (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯЯ (57) Изобретение относится к вычислительной технике и микроэлектронике и предназначено для микропрограммного управления. Цель изобретения — повышение быстродействия устройства.

Микропрограммное устройство. управления содержит блок 1 памяти микрокоманд, регистр 2 адреса, регистр 3 логических условий, блок 4 задержки.

Указанная цель достигается с помощью указанной совокупности блоков. 2 .ил.

132Э8О6

Изобретение относится к вычислительной технике и миктроэлетгтронтик» н предназначено для микропрограммного управления.

Цель изОбретения — поэышени» eiFIстродействия устройства.

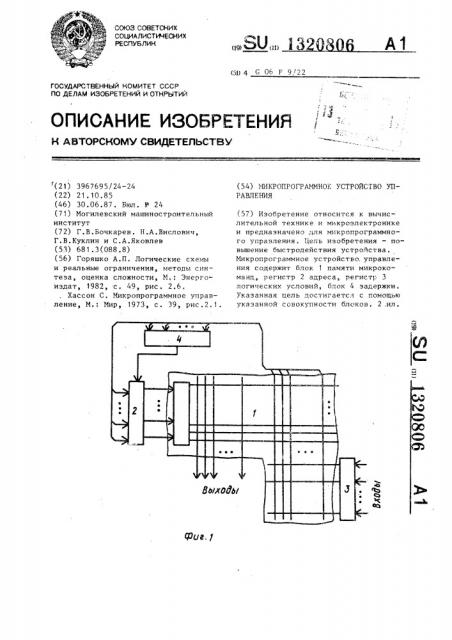

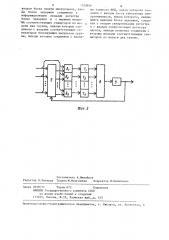

Ня фиг. 1 изображена структурная схема устройства., на фиг. 2 — стр гкTурнЯя схемЯ блокЯ задержке, Устройство (фиг 1) содержит блок

1 памяти микрокоманд, регистр 2 адреса, регистр 3 логических условий и блок 3 задержки.

Блок задержки (фиг, 23 содержит регис "p 5, группу сумматоров 6,, 6,,,,.6„ по модулю дтза, группу генераторов 7„,. 7, ..., 7„, блокирующих импульсоэ,, элемент ИЛИ 8 и генератор

9 синхроимпульсов.

Устройстго работает следующим

Образом.

В начальный момент времени устройст)зо находится э исходном состоя-. нии. В регистре 3 эяттисяна информация оэ условиях перехода устройстза

В следующее состояние. Си-нал на выХОДЕ 5SIOKa )3 СитхРОНИЗЯЦИИ СООТЭЕ)"ствуег уровню логического нуля. В следующий момент устройство эяпус<ается„ и генерятop : с.HHxl)аимпул ;-сов выдает импульс, достяточны33 по для= ттельности для срабатывания п»рзотт

Ст т ПЕНИ р»ГНСТря 2 ..О СП.ЗДУ ИНХроИМПУЛЬСа И11фОРМЯЦИЯ НЭ ПЕР)ЗОй С ТУ тЕнт1 регистра 2 переписыэа»11 я во вт cpal) cTyiieнь я затем — э регистр э бгтока задержки.

Г»H»paTopi! 7 блоккрующ31Х импульсон

ЗЯПУСКЯЮТСЯ ПО (gPOHT) ИМГ1ЧГтьса На

ВХОДЕ ЗЯПУСКа, ЗаПУСК Кат33ДО1С ЕН»РЯтора блокирующих импульсоэ свяэ;тн с изменением сигняпоэ -la входах логического элемента однсг". заранее поставленного в соответс вне этому генератору,, из рангов унивэрся)7ьного дешифратора блока 1 памяти микрокоманд. Это изменение отслеживается с помощью регистра 23 регистра блока зядержкн и сумматоров 6 по могу«лю

Вектор эходньгх сигналов„. Л1рисутствовавший на входах унивеэсяльнсго дешифрятора блока памяти микроко янд в предыдущем цикле работы устройства и хранящийся в регис "pe 5 блокa "адержки, сравнивается с актуальным век=тором, В случа»„ если хотя бы один иэ актуальных сигналов,, связанных с

ЭХОДЯМИ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ КЯКОГО

::1 бо ранга универс .nüaoão дешифратора,, изменяется по :равнению с предыдущим циклом, то генератор блокирующ«тх импульс os,, пос Г я вл»ннь)тт в cooT в» гстэие: этом y рян. ) Запускается .

Дпитель:ocòü импульса, выдаваемого генератором блокирующих импульсоэ, достятОчня для срябятыВания постяв т 4/I ментов этогс ранга последовятельности других рангов.

Так, 7 первый и Второй генераторы блокирующих импульсоВ Вьтдякт достяточньзт по длительности бятывяния всех рангов униэеро дешифратора. Третий генераблокирующих импульсов выдает достаточный по длительности батывяния э"ех рангов универо дешифряторя„ кроме первого

Время блокHpo÷KII определяется т г

31МПУЛ ЬС сра сяльног

3 импульс для cpa

;aльног

75 И T„ il им-)ульсом того из эапустившихся генераторов блокирующих импульсов,. который имеет максимальную длительность

Геттератор 9 ситзхроимпульсов э:НусКается по спаду б;токнрутощего импульса.

11 Оц»СС ПОВТСт я»тся ттэткЛИЧЕС 3<И, о р м у л;. э о б р з - » н и я."1тткрсп)ро) ря:-.».тнсс уст-Ойстэо yn"açë»HHÿ, с(.,;еp llaEG" Олок памяти мик

Г,О;-СОМЯНт:., РЕГ;:,С -:!O ЯДРЕСЯ,. РЕ-ИС-Р . :Огическ-Ix -:;слоэттй, блок задержки, И --:.: ":ЬХОгЬ3 Мнк-.- ОП»па тий бЛОКа ПяЬ«Я 3« "IKi) Ol lI I l> : тт(Зтгтн»НЫ С т" ттГХОД

;c7 эс : —;стэя. Вьгтоды адреса блока

":.- . Мяэ и микт) Окo:". 3 нд с Оед. -тнень3 с Входя

:-;н блока эят,»I)жки в-.тходы рсгэтстра

ЯЛРЕСЯ -OÅÄ"È-:.ЗНЫ С тт»РЭСй Г",ЗУГ1ПОй

)ip»cH4Ix вход:)в бл )кя ттямя ::1 ктгт«кро - G та 1-37 Эхог IO; ЧЧ " .Г К «тх У СПОЭтнтй -,,тСТ, Ойства соег.;13 1ен =:и:нформационным

Хот,ом р Г:3С: ря ЛОГИ :С «тх т т-ЛОВИИ q с. т л и ч а ю l е е с я тем. что целью гтовь)г31=-нl%я бь)стродействия т б);Э)3. ЭЯДЕР; Кт-. СОДЕР,:,< 37 РЕГHCTP ГРУПcóû;aTоров l1G модулю дэя, группу г:»нерятороэ блокттрутэщих и„"тпупьс «чв

=-л-емент ИЛИ, генератор синхроимпульсоВ, причем ВНГ<оды адреса блока пямяти микрокомянд с оединены -= информационными Входами регистра адреса, выход регистра логических условий

ОЕД)тНЕH С ВТОР ОИ Г)РУПтпон ЯДР ЕСНЫХ.ленного ему в соотэетстэие ранга универсального гешифрятора, а также

СВЯЗЯННОй С ВЬГХОДЯ.ти ЛОГИЧЕСКИХ ЭЛЕ3 . 320806 4 входов блока памяти микрокоманд, вхо- ми элемента ИЛИ,. выход которого соеды блока задержки соединены с динен с входом 1 уска генератора сининформационными входами регистра хроимпульсов, выход которого, являюблока задержки и с первыми входа- щикся выходом блока задержки, соедими соответствующих сумматоров по мо- „= нен с входом синхронизации регистра дулю два группы, выходы которых сое- и с входом синхронизации регистра динены с входами соответствующих ге- адреса, выходы регистра соединены с нераторов блокирующих импульсов груп- вторыми входами соответствующих сумпы, выходы которых соединены с входа- маторов по модулю два группы.

Составитель А.Михайлов

Редактор И.Касарда Техред N.Ìapãeíòäë Корректор.Л.Пилипенко

Заказ 2658/51 Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобр тений и открытий

113035, Москва, Ж-35, Раушская наб,,д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4