Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к запоминающим устройствам, которые используются для временного хранения данных, и может быть использовано в устройствах автоматики и вычислительной техники. Цель изобретения - расширение области применения за счет реализации режима «последний вошел - первый вышел. Буферное запоминаюш.ее устройство содержит регистры 1, блоки 2 элементов И, триггеры, группы элементов И 4 и 5, элементы И 6-8, элементы ИЛИ 9-11, элементы 2И-ИЛИ 12, блок 13 индикации свободных регистров, триггер 14, информационные входы 15, вход 16 чтения, стробирующий вход 17, выходы 18 числа свободных регистров и информационные выходы 19. Устройство работает в двух режимах, определяемых состоянием триггера 14. В режиме «первый воше.т - первый вышел информация с входов 15 переписывается последовательно в регистры 1 от первого к последнему. При этом перепись осуществляется через блоки 2, управляемые сигналами с выходов элементов И 4, если последующий регистр свободен . При поступлении сигнала на вход 16 происходит выдача данных из последнего регистра и сдвиг всего массива данных в сторону последнего регистра. В режиме «последний вощел-первый вышел при записи данных с входов 15 осуществляется занесение их в первый регистр. При записи последующих данных осуществляется сдвиг данных на один регистр в сторону последнего. При чтении данных по сигналам на входе 16 на выход 19 поступают данные из первого регистра и осуществляется сдвиг массива данных на одну порцию в сторону первого регистра 1. Блок 13 осуществляет индикацию по сигналу на входе 17 числа свободных регистров. 3 ил. 77 (Л оо ьо о 00 05 J8

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU „„1320846

А1 (51) 4 G 06 F 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АBTOPCHOMV СВИДЕТЕЛЬСТВУ

I

7« г!!1й.:.Й;.: „.". г; «» !

Щиг. 7

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 39629! 5/24-24 (22) 08. 10.85 (46) 30.06.87. Бюл. № 24 (72) П. И. Крупецкая, Ю. И. Мосиенко и Б. A. Фураш (53) 681.327.6 (088.8) (56) Авторское свидетельство СССР № !026!64, кл. G 11 С 19/00, 1979.

Авторское свидетельство СССР № 957429, кл. G 11 С 19/00, 1981. (54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к запоминающим устройствам, которые используются для временного хранения данных, и может быть использовано в устройствах автоматики и вычислительной техники. Цель изобретения — расширение области применения за счет реализации режима «последний вошел — первый вышел». Буферное запоминающее устройство содержит регистры 1, блоки 2 элементов И, триггеры, группы элементов И 4 и 5, элементы И 6 — 8, элементы

ИЛИ 9 — 11, элементы 2И вЂ” ИЛИ 12, блок

13 индикации свободных регистров, триггер 14, информационные входы 15, вход 16 чтения, стробирующий вход 17, выходы 18 числа свободных регистров и и нформационные выходы 19. Устройство работает в двух режимах, определяемых состоянием триггера 14. В режиме «первый вошел первый вышел» информация с входов 15 переписывается последовательно в регистры 1 от первого к последнему. При этом перепись осуществляется через блоки 2, управляемые сигналами с выходов элементов И 4, если последующий регистр свободен. При поступлении сигнала на вход 16 происходит выдача данных из последнего регистра и сдвиг всего массива данных в сторону последнего регистра. В режиме «последний вошел — первый вышел» при записи данных с входов 15 осуществляется занесение их в первый регистр. При записи последующих данных осуществляется сдвиг данных на один регистр в сторону последнего.

При чтении данных по сигналам на входе

16 на выход 19 поступают данные из первого регистра и осуществляется сдвиг массива данных на одну порцию в сторону первого регистра 1. Блок 13 осуществляет индикацию по сигналу на входе 17 числа свободны х ре ги стр о в. 3 ил.

1320846

25

35

45

Изобретение относится к запоминающим устройствам, которые используются для временного хранения данных, и может быть использовано в устройствах автоматики и вычислительной техники.

Цель изобретения — — расширение области применения устройства за счет организации режима «последний вошел — первый вышел».

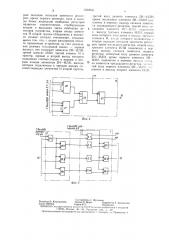

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 — функциональная схема блока индикации свободных регистров; на фиг. 3 — пример функционального выполнения блока разрешения записи и регистра.

Устройство (фиг. 1) содержит регистры

l. блоки 2 элементов И, триггеры 3 регистров 1 (показаны на фиг. 3), группу элементов И 4, группу элементов И 5, элементы

И 6 — 8, элементы ИЛИ 9 — 11, элементы

2И вЂ” ИЛИ 12, блок 13 индикации свободных регистров, триггер 14, информ ационные входы 15, вход 16 считывания, стробирующий вход 17, выходы 18 числа свободных регистров, информационные выходы 19, элементы ИЛИ 20 и 21, реверсивный счетчик 22, регистр 23 и элементы И 24 — 26.

Буферное запом инающее устройство работает следующим образом.

В исходном состоянии регистры свободны от информации, на нулевых выходах триггеров 3.1 соответствующих пегистров имеются сигналы НИ, НИ« — НИн (НИ— наличие информации; НИ вЂ” отсутствие информации), подтверждающие отсутствие информации в регистрах 1, кроме первого. На выходе элементов И 6 и ИЛИ

9 единичный сигнал, подтверждающий отсутствие информации во всех регистрах

1, кроме первого, на выходе элемента И 4.1 и на входе блока 2.1 элементов И имеется сигнал, разрешающий запись, на выходах элементов И 4.2 — 4. N и всех элементов

И 5 сигналы отсутствуют, на реверсивном счетчике 22 установлен код, соответствующий количеству регистров.

При поступлении на вход 15 устройства информационного слова через блок 2.1 =-aциси записывается в регистр 1.1, изменяется состояние триггера 3.1 регистра 1,1, на его выходе появляется сигнал (НИ, ).

Считывание информации из регистров !.1 — 1. N производится в режиме «первый вошел — первый вышел» и в режиме «первый вошел — последний вышел».

В первом режиме на первом выходе триггера 14 устанавливается единичный сигнал

1, который поступает на первые входы элементов 2И вЂ” ИЛИ и совместно с сигналами (НИ) о наличии информации с выходов триггеров 3.1 регистров l подготавливает элементы И 5 для выработки сигнала управления считыванием. Этот сигнал вырабатывается при поступлении сигнала считывания

2 на вход 16 устройства и разрешает выдачу информации из соответствующего регистра

1 на информационные выходы 19 устройства.

При каждом появлении сигналов НИ и

НИ на соответствующих входах блока 13 индикации свободных регистров реверсивный счетчик 22 вычитает или прибавляет единицу к своему содержимому. и таким образом осуществляется учет количества незанятых регистров. При появлении сигнала на стробйрующем входе 17 устройства производится выдача кода, определяющего количество свободных регистров.

Во втором режиме на втором выходе триггера 14 режима устанавливается единичный сигнал, который поступает на третьи входы всех элементов 2И вЂ” ИЛИ 12 и совместно с сигналами о наличии информации с единичных выходов триггеров 3.1 регистров подготавливает элементы И 5 для разрешения прохождения сигнала считывания с входа 16 устройства на входы считывания регистров l.

Формула изобретения

Буферное запоминающее устройство, содержащее регистры, информационные входы которых подключены к выходам соответствующих блоков элементов И, одноименные информационные входы которых объединены и являются информационными входами устройства, входы стробирования блоков элементов И подключены к выходам соответствующих элементов И первой груп пы, первые входы которых подключены к входам первой группы блока индикации свободных регистров и к первым выходам сигналов занятости соответствующих регистров. вторые выходы сигналов занятости подключены к входам второй группы блока индикации свободных регистров и к первым входам соответствующих элементов

И второй группы, выходы которых подключены к стробирующим входам соответствующих регистров, одноименные выходы которых объединены и являются информационным и выходами устройства, второй вход данного элемента И первой группы, кроме первого, подключен к первому входу предыдущего элемента И второй группы, второй вход первого элемента И первой группы подключен к выходу первого элемента ИЛИ, первый вход которого подключен к выходу первого элемента И, входы которого подключены к первым выходам сигналов занятости регистров, кроме первого регистра, второй вход первого элемента ИЛИ подключен к второму выходу сигнала занятости последнего регистра, первый выход сигнала занятости которого подключен к первому входу второго элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, входы которого подключены к вто1320816

Дцг.2

С й7гОЖ7 377Рминно и5

Сй злеп

Диг. 3

Составитель С. Шу стенка

Редактор Н. Киштулинец Техред И. Верес Корректор А. Зимокосов

Заказ 2662 53 Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1!3035, Москва, >K — 35, Раушская наб.. д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород. ул. Проектная, 4 рым выходам сигналов занятости регистров, кроме первого регистра, вход и выходы блока индикации свободных регистров являются соответственно стробирующим входом и выходами числа свободных регистров устройства, вторые входы элементов И второй группы объединены и являются входом сигнала считывания, отличаюи ееся тем, что, с целью расширения области применения устройства за счет реализации режима «последний вошел — первый вышел», оно содержит элементы 2И вЂ” ИЛИ, третий элемент ИЛИ, третий элемент И и триггер, первый и второй выход которого подключен соответственно к первым и вторым входам элементов 2И вЂ” ИЛИ, выходы которых подключены к третьим входам соответствующих элементов И второй группы, третий вход данного элемента 2И вЂ” ИЛ И, кроме последнего элемента 2И вЂ” ИЛИ подключен к первому выходу сигнала занятости последующего регистра, третий вход по5 следнего элемента 2И вЂ” ИЛ11 !1одклкп!ен к выходу третьего элемента ИЛИ, первый вход которого подключен к выходу третьего элемента И, Bxîëü которого пo lêëþчcHhl к

BTopblM выходам сигналов занятости реп1стров, кроме последнего регистра, второй вход третьего элемента ИЛИ подключен к»ервому выходу сигнала занятости первого регистра, четвертый вход данного элемента

2И вЂ” ИЛИ, кроме первого элемента 2И-ИЛИ, подключен к первому выходу сн мнила занятости предыдущего регистра. i,ñ700ðтый вход первого элемента 2И вЂ” И,:11! и 1ключен к выходу второго элемента И;1И.