Устройство преобразования входного двоичного сигнала в телеграфный сигнал

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи . Цель Изобретения - уменьшение потребляемой мощности за счет исключения делителей напряжения. Устр-во содержит двухполярныа источники 1 и 2 питания и смещения, п-р-пи р-п-рфазоинвертирующие транзисторы (Т) 3 и 4, диоды 7 и 8, р-п-ри п-р-п-выходные Т 9 и 10, резисторы 11-17 и ограничители 5 и 6 тока, вьтолненные каждый из Т 18 и 19 и резисторов 20 и 21. Из-за отсутствия делителей напряжения в ограничителях 5 и 6 тока данное устр-во потребляет и рассеивает меньшую мощность и менее критично к разбросу номиналов резисторов и параметров используемых Т. Устр-во по п.2, ф-лы отличается выполнением ограничителей 5 и 6 тока. 1 з.п. ф-лы, 1 ИЛ-. (Л :о о со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

А1 (19) (11) (5ц 4 Н 04 L 25/20

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTI44

Н ASTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 3929276/24-09 (22) 13.05.85 (46) 30.06.87. Бюл. Р 24 (72) Д.М.Затикян и С.А.Мелконян (53) 621.394.6 (088.8) (56) Авторское свидетельство СССР

Ф 1125765, кл. Н 04 L 25/20, 1983. (54) УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ВХОДНОГО ДВОИЧНОГО СИГНАЛА В ТЕЛЕГРАФНЬЙ

СИГНАЛ (57) Изобретение относится к электросвязи. Цель изобретения — уменьшение потребляемой мощности за счет исключения делителей напряжения. Устр-во содержит двухполярныв источники 1 и

2 питания и смещения, п-р-п- и р-и-рфаэоинвертирующие транзисторы (Т) 3 и 4, диоды 7 и 8, р-и-р- и п-р-и-выходные Т 9 и 10, резисторы 11-17 и ограничители 5 и 6 тока, выполненные каждый из Т 18 и 19 и резисторов 20 и 21. Из-за отсутствия делителей напряжения в ограничителях 5 и 6 тока данное устр-во потребляет и рассеивает меньшую мощность и менее критично к разбросу номиналов резисторов и. параметров используемых Т. Устр-во по п.2, A-лы отличается выполнением ограничителей 5 и 6 тока. 1 з.п. ф-лы, 1 ил.

1 13209

Изобретение относится к электросвязи и может быть использовано для сопряжения источников цифровой информации с телеграфными каналами связи.

Цель изобретения — уменьшение потребляемой мощности за счет исключения делителей напряжения.

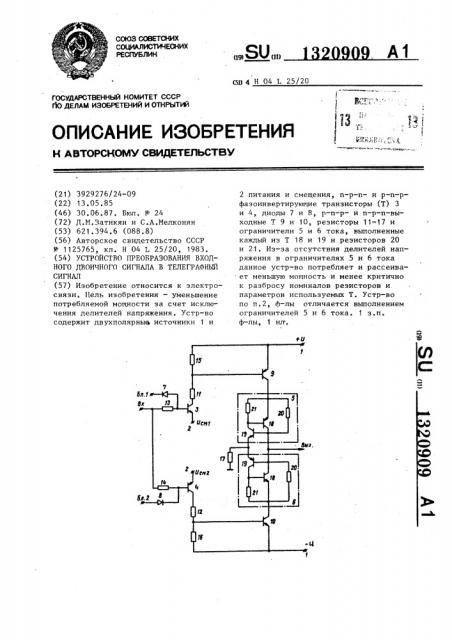

На чертеже представлена принципиальная электрическая схема устройства преобразования входного двоичного 10 сигнала в телеграфный сигнал.

Устройство преобразования входного двоичного сигнала в телеграфный сигнал содержит двухполярный источник 1 питания, двухполярный источник

2 смещения, и-р-и-фазоинвертирующий транзистор. 3, р-и-р-фазоинвертирующий транзистор 4, первый и второй ограничители 5 и 6 тока, первый и

20 второй диоды 7 и 8, р-и-р-выходной транзистор 9, и-р-и-выходной транзистор 10 и первый — седьмой резисторы

11-17 соответственно, а каждый ограничитель тока содержит первый и второй транзисторы 18 и 19 и первый и второй резисторы 20 и 21 соответственно.

Устройство преобразования входного двоичного сигнала в телеграфный сигнал работает следующим образом.

При подаче на блокировочные входы устройства напряжений, при которых первый и второй диоды 7 и 8 закрыты, и при наличии на сигнальном входе логической единицы, и-р-и-фазоинвертирующий транзистор 3 открыт и насыщен, а р-п-р-фазоинвертирующий транзистор 4 закрыт. Закрыт также и-р-и40 выходной транзистор 10, а р-п-р-выходной транзистор 9 открыт, На базу второго транзистора 19 первого ограничителя 5 тока через первый резистор

20 поступает напряжение положительной полярности, которое открывает этот транзистор. Через открытый первый транзистор 19 первого ограничителя

5 тока относительно его эмиттера подают отпирающий потенциал, что приводит к открыванию первого транзисто50 ра 18 первого ограничителя 5 тока, что в свою очередь вызывает шунтирование первого резистора 20 и на выходе устройства появляется потенциал положительной полярности, равный раз55 ности напряжений на плюсовой шине источника 1 питания и падений напряжений на открытых выходном р-п-р09 2 транзисторе 9 и первом транзисторе

18 первого ограничителя 5 тока.

При наличии на сигнальном входе устройства логического нуля открыт и насыщен р-п-р-фазоинвертирующий транзистор 4, открыт также выходной п-р-п-транзистор 10, а транзисторы

3 и 9 закрыты. На базу второго транзистора 19 второго ограничителя 6 тока через первый резистор 20 поступает напряжение отрицательной полярности, открывающее его. Через открытый транзистор 19 второго ограничителя 6 тока на базу первого транзистора 18 относительно его эмиттера подают отпирающий потенциал и этот транзистор открывается. Открытый транзистор l8 шунтирует первый резистор 20 второго ограничителя тока и на выходе устройства появляется сигнал отрицательной полярности.

При перегрузке, возникающей из-за короткого замыкания в линии, подключаемой к выходу устройства, или при появлении в ней встречного напряжения происходит следующее. Если при этом на входе устройства действует сигнал логической единицы, то на базу второго транзистора 19 первого ограничителя 5 тока поступает запирающий потенциал, что вызывает запирание также и первого транзистора 18, в результате чего через второй транзистор

i9 течет небольшой ток, величина которого зависит от величины первого резистора 20, определяющего также и величину тока, отбираемого от плюсовой шины источника 1 питания.

Аналогичные процессы протекают во втором ограничителе 6 тока при наличии на сигнальном входе устройства сигнала логического нуля и при коротком замыкании в линии или при появлении в ней встречного напряжения.

При необходимости блокировки устройства на его блокировочные входы необходимо подать напряжения, открывающие диоды 7 и 8:

Uga< П м Uy ïð в

6л2 Сма ) nP ° где U д — падение напряжения на открытом диоде;

Б,„„и О,„ - напряжения смещения на плюсовой и минусовой шинах источника 2 смещения.

Таким образом, предлагаемое устройство по сравнению с известным

3 132 из-за отсутствия делителей напряжения в ограничителях тока потребляет и рассеивает меньшую мощность и менее критично к раэбросу номиналов резисторов и параметров используемых транзисторов.

0909 4 и седьмого резисторов соединены соответственно с плюсовой и минусовой шинами и точника питания и общей ши.ной, о т л и ч а ю щ е е с я тем, что, с целью уменьшения потребляемой мощности эа счет исключения делителей .напряжения, вторые выводы пятого и шестого резисторов соединены с базами соответственно р-и-р- и п-р-п-выходных транзисторов, эмиттеры которых соединены соответственно с плюсовой и минусовой шинами источника питания, коллекторы выходных транзисторов соединены с входами соответствующих

f5 ограничителей тока, основные и дополнительные выходы которых соединены соответственно с выходом устройства и вторым выводом седьмого резистора.

Формула изобретения

1. Устройство преобразования входного двоичного сигнала в телеграфный сигнал, содержащее двухполярные источник питания и смещения, два фазоинвертирующих транзистора разного типа проводимостей, два ограничителя тока, два диода и два выходных транзистора разного типа .проводимости, причем база р-и-р-выходного транзистора через первый резистор соединена с коллектором и-р-и-фазоинвертирующего транзистора, база п-р-и-выходного транзистора через второй резистор подключена к коллектору р-п-р-фазоинвертирующего транзистора, анод первого диода соединен с базой и-р-ифазоинвертирующего транзистора и первым выводом третьего резистора, катод второго диода подключен к базе р-и-рфазоинвертирующего транзистора и первому выходу четвертого резистора, вторые выводы третьего и четвертого резисторов объединены с сигнальным входом устройства, блокировочными входами которого являются катод и анод первого и второго диодов соответственно, при этом эмиттеры фазоинвертирующих транзисторов подключены к соответствующим шинам источника смещения, первые выводы пятого, шестого

20 2. Устройство по и. 1, о т л и— ч а ю щ е е с я тем, что каждый ограничитель тока выполнен на парах транзисторов разного типа проводимостей, причем эмиттер первого транзи25 стора соединен с первым выводом первого резистора и через второй резистор с коллектором второго транзистора и базой первого транзистора, коллектор которого объединен с базой второ3Q ro транзистора, вторым выводом первого резистора и является основным выходом ограничителя тока, входом и дополнительным выходом которого являются эмиттеры первого и второго транзисторов соответственно, при этом первый транзистор первого ограничителя тока и второй транзистор второго ограничителя тока являются транзисторами р-и-р типа проводимости.

Составитель В.Зенкин

Техред М.Ходанич Корректор М.Шароши

Редактор M.Ïåòðoâà

Заказ 2669/57 Тираж 638 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4