Устройство автоматического контроля правильности чередования и отсутствия обрыва фаз многофазных сетей переменного тока

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано в любой отрасли промышленности в системах питания, управления и защиты механизмов и устройств, критичных к неправильному чередованию или пропаданию фаз многофазной сети. ИзобА ретение позволяет повысить быстродействие путем обеспечения работы устройства на любой рабочей частоте с временем реагирования, составляющим одну треть периода, а также повысить надежность устройства путем исключения сигнала ложной исправности в некоторых режимах работы. Устройство содержит формирователи-ограничители 1-3, элементы И 4,5,6,10,13,16,20,21 и 22, трехвходовый элемент ИЛИ-НЕ 7, элементы ИЛИ 8, 11, 14 и 23, инверторы 9, 12 и 15, RS-триггеры 17, 18 и 19, исполнительный элемент 24. Устройство может работать в сетях многофазного переменного тока любой частоты без перестройки и замены схемных элементов. Воздействие импульсных помех не нарушает работы устройства. 4 ил. С/; о

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

2205 А1 (19) (ll) й04G 01 R29 18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Ю1

Р с

Фис. l

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

М А BTOPCKOMV СВИДЕТЕЛЬСТВУ (21) 4040975/24-21 (22) 24.03.86 (46) 07.07.87. Бюл, У 25 (72) Д.Л.Орлов и Я.А.Мачинский (53) 621. 317. 75 (088. 8) (56) Патент США У 3825768, кл. 307-130, 1970, Авторское свидетельство СССР

У 586404,, кл. G 01 R 29/18, 1975. (54) УСТРОЙСТВО АВТОМАТИЧЕСКОГО КОНТРОЛЯ ПРАВИЛЬНОСТИ ЧЕРЕДОВАНИЯ И ОТСУТСТВИЯ ОБРЫВА ФАЗ МНОГОФАЗНЫХ СЕТЕЙ

ПЕРЕМЕННОГО ТОКА (57) Изобретение может быть использовано в любой отрасли промышленности в системах питания, управления и защиты механизмов и устройств, критичных к неправильному чередованию или пропаданию фаз многофаэной сети. Изобретение позволяет повысить быстродействие путем обеспечения работы устройства на любой рабочей частоте с временем реагирования, составляющим одну треть периода, а также повысить надежность устройства путем исключения сигнала ложной исправности в некоторых режимах работы. Устройство содержит формирователи-ограничители

1-3, элементы И 4, 5, 6, 10, 13, 16, 20, 2 1 и 22, трехвходовый элемент ИЛИ-НЕ 7, элементы ИЛИ 8, 11, 14 и 23, инверторы 9, 12 и 15, RS-триггеры 17, 18 и 19, исполнительный элемент 24. Устройство может работать в сетях многофазного переменного тока любой частоты беэ перестройки и замены схемных элементов. Воздействие импульсных по- ф/1 мех не нарушает работы устройства.

4 ил.

45

1 13222

Изобретение относится к контролю многофазных сетей переменного тока и может быть использовано в любой отраслн промышленности в системах питания, управления и защиты механизмов и устройств, критичных к неправильному чередованию или пропаданию фаз многофазной сети.

Цель изобретения — повышение быстродействия путем обеспечения работы устройства на любой рабочей частоте с временем реагирования 1/3 периода и повышение надежности путем исключения ложной исправности в некоторых режимах работы.

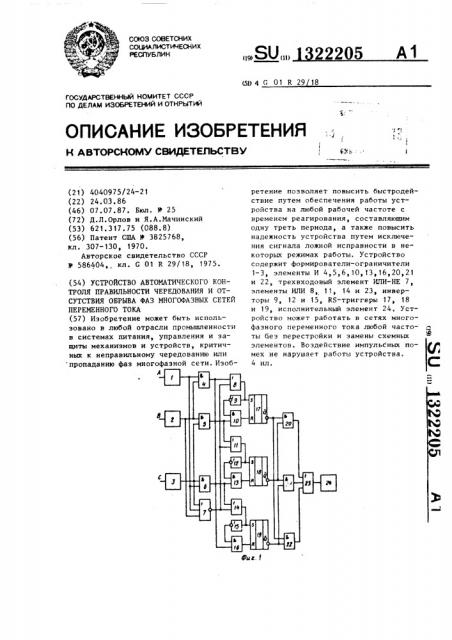

На фиг.1 представлена принципиальная схема устройства, на фиг.2 работа устройства в полнофазном ре- жиме при правильном чередовании фаз, на Фиг.3 — то же, в неполнофазном режиме при правильном чередовании фаз (пропадание фазы С); на фиг.4 — то же в полнофазном режиме при нарушении чередования фаз.

Устройство состоит из формирователей-ограничителей 1-3, первых трех элементов И 4-6, трехвходового элемента KIN-HE 7, первого двухвходового элемента ИЛИ 8, первого инвертора

9, первого дополнительного элемента

И 10, второго двухвходового элемента

ИЛИ 11, второго инвертора 12, второго дополнительного элемента И 13, третьего двухвходового элемента ИЛИ 14, третьего инвертора 15, третьего дополнительного элемента И 16, первого

17, второго 18 и третьего 19 RS-триггеров, четвертого 20, пятого 21 и шестого 22 элементов И, трехвходового элемента ИЛИ 23 и исполнительного 40 элемента 24.

Входы формирователей-ограничителей 1-3 подключены соответственно к фазам А, В, С трехфазной сети. Выход формирователя 1 соединен с первым входом элемента И 4 и вторыми входами элементов И 6 и ИЛИ-HE 7, выход формирователя 2 соединен с вторым входом элемента И 4, первым входом элемента И 5 и третьим входом элемента

И1П1-НЕ 7, выход формирователя 3 соединен с вторым входом элемента И 5 и первыми входами элементов И 6 или

ИЛИ-НЕ 7, выход элемента ИЛИ-HE 7 соединен с вторыми входами элементов

ИЛИ 8, 11 и 14, выход элемента И 4 соединен с первым входом элемента

ИЛИ 8 и вторым входом элемента И 16, 05 г выход элемента И 5 соединен с вторым входом элемента И 10 и первым входом элемента ИЛИ 11, выход элемента И 6 соединен с вторым входом элемента И

13 и первым входом элемента ИЛИ 14, выход элемента ИЛИ 8 соединен с входом инвертора 9 и входом S триггера

17, выход элемента ИЛИ 11 соединен с входом инвертора 12 и входом S триггера 18 выход элемента ИЛИ 14 соединен с входом инвертора !5 и входом

S триггера 19, выход инвертора 9 соединен с первым входом элемента И 10, выход инвертора 12 соединен с первым входом элемента И 13, выход инвертора 15 соединен с первым входом элемента И 10, выход элемента И 10 соединен с входом R триггера 17, выход элемента И 13 соединен с входом R триггера 18, выход элемента И 16 со единен с входом R триггера 19, выход триггера 17 соединен с первыми входами элементов И 20 и 22, выход Q триггера 18 соединен с вторым входом элемента И 20 и первым входом элемента И 21, выход триггера 19 соединен с вторыми входами элементов

И 2 1 и 22, выходы элементов И 20-22 соединены соответственно с первым, вторым и третьим входами элемента ИЛИ

23, выход которого соединен с испол=1 нительным элементом 24.

Работа устройства основана на том принципе, что в определенные моменты времени (1/6 периода) положительные полуволны напряжения двух фаз совпадают во времени. Эти совпадения происходят в последовательности, определяемой чередованием фаз.

Так при правильном чередовании фаз и в момент совпадения во времени полуволн фаз А и В на выходе элемента И 4 появляется импульс, который устанавливает RS-триггер 17 в нулевое состояние и одновременно устанавливает RS-триггер 19 в единичное состояние. При совпадении фаз В и С появляющийся на выходе элемента И 5 импульс устанавливает триггер 18 в нулевое состояние и одновременно устанавливает триггер 17 в единичное.

При совпадении фаз С и А триггер

19 устанавливается в нулевое состояние, а триггер 18 — в единичное. В любой момент времени на выходе одного из элементов И 20-22 обязательно присутствует сигнал, равный по длительности 1/3 периода сети, так как с

3 132220 этим перекрытием вырабатываются сигналы на выходах триггеров 17- 19. Последовательное чередование импульсов на выходах элементов И 20-22 совпадения обеспечивает постоянный единичный 5 сигнал на выходе элемента ИЛИ 23. Исполнительный элемент 24 включен постоянно (фиг. 2).

При пропадании хотя бы одной из фаз элемент ИЛИ-НЕ 7 выдает единич- 10 ный сигнал, который одновременно устанавливает триггеры 17- 19 в нулевое состояние. В дальнейшем на выходах элементов И 20-22 сигнал отсутствует до тех пор, пока в сети не восстано- !5 вится полнофазный режим. Все это время сигнал на включение исполнительного элемента 24 отсутствует (фиг. 3).

При неправильном чередовании фаз импульсы на выходах логических эле- 2р ментов И 4-6 появляются в иной последовательности, а следовательно, установка триггеров 17-19 в нулевое и единичное состояния происходит по другому закону, чем при правильном чере- 25 довании. Совпадения импульсов во времени на выходах триггеров 17-19 не

Т роисходит, так как длительность каждого импульса менее 1/3 периода сети.

Объединенный элементом ИЛИ 23 сигнал 3р ,не вьщает разрешение на включение исполнительного элемента 24 (фиг.4), Воздействие импульсных помех работу устройства не нарушает.

Устройство работает в сетях много- 35 фазиого переменного тока любой частоты без перенастройки и замены элемен тов.

Формула изобретения 40

Устройство автоматического контроля правильности чередования и отсутствия обрыва фаз многофаэных сетей переменного тока, содержашее три 45 формирователя-ограничителя, причем выход первого формирователя соединен с первым входом первого элемента И и вторым входом третьего элемента И, выход второго формирователя соединен 50 с вторым входом первого элемента И и первым входом второго элемента И, выход третьего формирователя соединен с вторым входом второго элемента И

5 4 и первым входом третьего элемента И, а также четвертья, пятый и шестой элементы И, выходы которых подключе ны соответственно к трем входам трехвходового элемента ИЛИ, выход которого соединен с исполнительным элементом, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности и быстродействия, в него введены логический элемент ИЛИ-НЕ с тремя входами, три двухвходовых элемента ИЛИ, три инвертора, три дополнительных элемента И и три RS-триггера, причем элемент ИЛИ-НЕ соединен тремя входами с выходами трех формирователей соответственно, и выходом с вторыми входами первого, второго и третьего двухвходовых элементов ИЛИ, выход первого элемента И соединен с первым входом первого двухвходового элемента ИЛИ и вторым входом третьего дополнительного элемента И, выход второго элемента И соединен с первым входом второго двухвходового элемента ИЛИ и вторым входом дополнительного элемента И, выход третьего элемента И соединен с первым входом третьего двухвходового элемента ИЛИ и с вторым входом второго дополнительного элемента И, выход первого двухвходового элемента ИЛИ соединен с входом

S первого RS-триггера и входом первого инвертора, выход второго двухвходового элемента ИЛИ соединен с входом S второго RS-триггера и входом второго инвертора, выход третьего двухвходового элемента ИЛИ соединен с входом S третьего RS-триггера и входом третьего инвертора, выходы первого, второго и третьего инверторов соединены соответственно с первьжи входами первого, второго и третьего дополнительных элементов И, выходы которых соединены соответственно с входами R первого, второго и третьего

RS-триггеров, причем выход первого

RS-триггера соединен с первым входом четвертого и шестого элементов И, выход второго RS-триггера соединен с вторым входом четвертого и первым входом пятого элементов И, а выход третьего RS-триггера соединен с вторыми входами пятого и шестого элементов И.

1322205 ъ

1

4

1 ф

Фие г

1322205

Составитель Н. Михалев

Техред Л.Сердюкова

Редактор М.Бланар

Корректор Л.Пилипенко

Закаэ 2860/42

Проиэводственно-полиграфическоепредприятие, r.Óçrîðîä, ул.Проектная 4 ! у ° ° ° °

Ъ

Тиразк 730 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5