Компаратор

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано для построения аналого-цифровых преобразователей (АЦП) в системах автоматического регулирования. Изобретение обеспечивает расширение функциональных возможностей путем сравнения сигналов, действующих в разные моменты времени. Компаратор содержит первую 1 и 2 и вторую 7 и 8 дифференциальные пары входных транзисторов. первую 3 и 4 и вторую 9 и 10 пары входных шин, управляемые генераторы 5 и 11 тока, первую 6 и вторую 16 шины питания, элементы 12 и 13 задержки , генератор 14 импульсов, первый 15 и второй 20 полевые транзисторы выходного истокового повторителя, нагрузочный резистор 17, бистабильный элемент 18, выходную шину 19, резистор 21, ключи 22 и 24, конденсаторы 23 и 25. Компаратор выполняет сравнение разновременных сигналов с большой точностью в результате исключения погрешностей, вносимьЪс ячейками выборки запоминания или АЦП. Компаратор превосходит по быстродействию известные схемы ячейки выборки запоминания или АЦП и усредняет входные сигналы на интервале стробирования входных транзисторов за счет интегрирования коллекторных токов. 1 ил. kn IS СО KD ND ISD tc sj

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTVM (21) 4032515/24-21 (22) 04.03.86 (46) 07.07.87. Бюл. Ф 25 (71) Институт кибернетики им.В.М.Глушкова (72) А.Д.Бех и В.В.Чернецкий (53).621.373.5(088.8) (56) Meyer G.L. Sampling comparators.

EDN, 1977, Ф 16, р. 22. (54) KOMIIAPATOP (57) Изобретение относится к импульсной технике и может быть использовано для построения аналого-цифровых преобразователей (АЦП) в системах автоматического регулирования. Изобретение обеспечивает расширение функциональных воэможностей путем сравнения сигналов, действующих в разные моменты времени. Компаратор содержит первую 1 и 2 и вторую 7 и 8 дифференциальные пары входных транзисторов, „„5U„„1322227 д1 (50 4 С 05 В 1/01 Н 03 К 5/24 первую 3 и 4 и вторую 9 и 10 пары входных шин, управляемые генераторы

5 и 11 тока, первую 6 и вторую 16 шины питания, элементы 12 и 13 задержки, генератор 14 импульсов, первый

15 и второй 20 полевые транзисторы выходного истокового повторителя, нагрузочный резистор 17, бистабильный элемент 18, выходную шину 19, резистор 21, ключи 22 и 24, конденсаторы 23 и 25. Компаратор выполняет сравнение разновременных сигналов с большой точностью в результате исключения погрешностей, вносимь)х ячейками выборки запоминания или АЦП. Компаратор превосходит по быстродейст = вию известные схемы ячейки выборки запоминания или АЦП и усредняет входные сигналы на интервале стробирования входных транзисторов за счет интегрирования коллекторных токов. 1 ил.

1 !3222

Изобретение относится к импульсной технике и может быть использовано для построения аналого-цифровых преобразователей в устройствах автоматического регулирования. 5

Целью изобретения является расширение функциональных возможностей за счет обеспечения возможности сравнения сигналов, действующих в разные моменты времени. 10

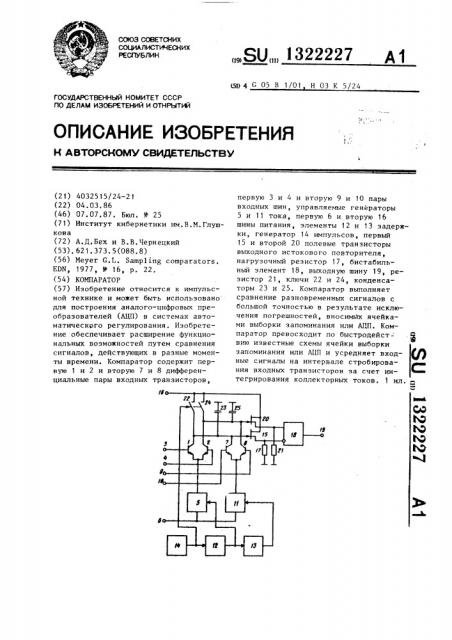

На чертеже представлена структурная схема компаратора.

Компаратор содержит первую дифференциальную пару входных транзисторов 1 и 2, базы которых соединены с 15 первой парой входных шин 3 и 4, эмиттеры объединены и подключены через первый управляемый генератор 5 тока к первой шине 6 питания, вторую дифференциальную пару входных тран- 20 эисторов 7, 8, базы которых соединены с второй парой входных шин 9 и 10, эмиттеры объединены и подключены через второй управляющий генератор 11 тока к первой шине 6 питания, последовательно соединенные первый 12 и второй 13 элементы задержки подключены между выходом генератора 14 импульсов и управляющим входом второго генератора 11 тока, коллекторы транзис- 30 торов 1 и 7 первой и второй дифференциальных пар объединены и подключены . к затвору первого полевого транзистора 15 выходного истокового повторителя, сток первого полевого транзистора 15 подключен к второй шине 16 питания, а исток через нагрузочный резистор 17 соединен с шиной нулевого потенциала и нулевым входом бистабильного элемента 18, выход которого под- 40 ключен к выходной шине 19 компаратора, коллекторы транзисторов 2 и 8 первой и второй дифференциальных пар объединены и подключены к затвору второго полевого транзистора 20 вы- 45 ходкого истокового повторителя, сток полевого транзистора 20 подключен к шине 16 питания, а исток через нагрузочный резистор 17 соединен с шиной нулевого потенциала и единичным входом бистабильного элемента 18, коллекторы транзисторов 1 и 7 соединены с второй шиной 16 питания через ключ

22 и первым выводом конденсатора 23, второй вывод которого соединен с шиной.нулевого потенциала, коллекторы транзисторов 2 и 8 соединены с второй п1иной 16 питания через ключ 24 и с первым выводом конденсатора 25, вто27 2 рой вывод которого соединен с шчной нулевого потенциала, управляющие входы ключей 22 и 24 объединены и подключены к выходу генератора 14 импульсов.

Компаратор работает следующим образом.

В начале интервала времени, в котором производится сравнение двух

I входных напряжений U Ä, приложенного х к входным шинам 3 и 4, и U8„, подаваемого на входные шины 9 и 10, конденсаторы 23 и 25 заряжаются до напряжения Е источника 16 питания. Заряд конденсаторов осуществляется через ключи 22 и 24, которые замыкаются на время "., равное длительности импульсов, периодически поступающих от генератора 14 импульсов. В остальной части периода поступления импульсов от генератора 14 импульсов выполняется сравнение мгновенных значений напряжений Увх и Ц,"% ° Выбор мгновенных значений входных напряжений в интервале сравнения производится в соответствии с величиной задержки импульсов генератора 14 импульсов на элементах 12 и 13 задержки. В моменты времени появления импульсов на выходах элементов 12 и 13 задержки происходит включение генераторов 5 и 11 тока на время 7 . В эмиттеры первой дифференциальной пары транзисторов

1 и 2 поступает ток I генератора 5 тока, а в эмиттеры второй пары 7 и 8 ток I " генератора 11 тока. Коллекторные токи транзисторов 1 и 2 первой пары перераспределяются в интервале времени ", пропорционально выходно1 му напряжению Б „, поскольку транзисторы работают в активном режиме. Аналогичный режим работы выполняется также для транзисторов 7 и 8 второй пары. Поскольку коллекторные токи транзисторов 1 и 2 первой пары не равны вследствие действия входного

I сигнала U „, то конденсаторы 23 и 25 разряжаются в интервале времени 7 до разного напряжения. Разность напряжений на конденсаторах 23 и 25, проПОрциОНальНая входНОму сигналу U&х ° поддерживается неизменной до момвнта запуска генератора 11 тока на время

7 . При этом конденсаторы 23 и 25 разряжаются на величину, пропорциональную величине коллекторных токов второй пары транзисторов 7 и 8> и, следовательно, величине второго входIl ного напряжения U ». Входные шины 9

Iy Г b(t ТГ Пэх

U =- — — -- — — — -(1+- — ) (1) с1 с„ 2с, 2М 40 где с, — величина емкости первого конденсатора 20, |х — коэффициент пропорциональности.

Ток эмиттера второго транзистора

Ir

2 первой пары ?, 2 и в °

45 нение напряжения на втором конденсаторе 25 под воздействием коллекторного тока транзистора 2:, (I

Г Г Ubx

U = — — — — (1 — ---) (2)

2с 2Ч

50 где с — величина емкости второго

2 конденсатора 25. 55

Учитывая, что напряжение Ub вклюl чено встречно по отношению к Ub получают изменение напряжения на пер3 13222 и 10 подключаются к источнику напряжения Бэх так, что транзисторы 7 и 8 ех второй пары создают на конденсаторах 23 и 24 напряжение противоположной полярности по сравнению с транзисто- 5 рами 1 и 2 первой пары. Величину задержки элемента 22, определяющую интервал времени между моментами включения пар входных транзисторов, выбирают намного меньшей постоянной 10 времени разряда конденсаторов 23 и

25. Для компаратора она равна произведению емкости конденсатора на сопротивление, эквивалентное параллельному включению входного сопротивле- 15 ния истокового повторителя и сопротивления утечки двух запертых входных транзисторов. В зависимости от выбранной емкости величина постоянной времени практически находится в пределах от нескольких микросекунд до нескольких десятков секунд.

Если выходное напряжение на емкостях компаратора пропорционально разности входных напряжений, ток эмитте-25 ра первого транзистора 1 первой пары

Ir 1 !

I = — + Ь I где I — ток генератоэ1 2 э Ф Г

I ра 5 тока, л? — изменение эмиттерного тока транзисторов 1 и 2 первой 30

I пары, вызванное сигналом Пэ . Его веI

| Ir личина 0 I Пх --- где | — теплоэ х 4 ° т т вой потенциал.

Изменение напряжения на первом 35 конденсаторе 23 под воздействием коллекторнога тока транзистора 1:

27 4 вом конденсаторе 23, вызванное коллекторным током транзистора 7 второй пары

|| (1 — ---) ° (3)

2с, 2Ч

Аналогично, изменение напряжения на втором конденсаторе, вызванное коллекторным током транзистора 8, равно

ll х с(сГ Ir Бьх

ЛПс = — - — — -(! + — -) (4)

2ст 2Ч

Напряжение на первом конденсаторе

23 после воздействия коллекторных токов обеих пар транзисторов равно

"с1 = E — || ||ст — bU cт (5)

Напряжение на втором конденсаторе 25 равно

Бс| = E — 4 Пс2 — ЛБс2 . (6)

Выходное напряжение на емкостях конденсаторов 23 и 25 равно

Usûõ Пс (7)

Выполняя подстановку равенств (1), (2) в (5) и (3), (4) в (6), а затем (5) и (6) в (7), получают с учетом обозначений I Г = I Гс = ? г, с„= с2 = с

/ Г Г Х

I — ----- (U — U ) (8) эь!х 2с ||| ьх ьх т где коэффициент усиления схемы К = Г Ir

2с |

Усиленная разность входных напряжений через истоковые повторители . поступает на входы бистабильного элемента 18. При П „= U э„, U „„= 0 бистабильный элемент 18 находится в неустойчивом положении. При неравенстве входных напряжений бистабильный элемент 18 устанавливается в одно иэ двух устойчивых положений.

Задача сравнения двух сигналов, действующих в различных интервалах времени, является одной из типовых задач в автоматическом регулировании, аналоговой вычислительной технике и аналого-цифровых преобразователях.

Для ее решения с помощью существующих компараторов дополнительно требуются ячейки выборки запоминания или аналого-цифровые преобразователи и оперативная память. При использовании предлагаемого компаратора необходимость в дополнительных аппаратурных затратах отпадает.

Сравнение разновременных сигналов с помощью предложенного компаратора

1322227

15 изобретения

Формула

Составитель Н.Маркин

Техред Л.Олейник Корректор М.Демчик

Редактор О.Головач

Заказ 2863/43

Тираж 863 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r.Óæãîðîä, ул.Проектная, 4 выполняется с большей точностью, поскольку исключаются погрешности,вносимые ячейками выборки запоминания или аналого-цифровыми преобразователями. 5

Предложенный компаратор значительно превосходит по быстродействию известные схемы ячейки выборки-запоминания и аналого-цифровые реобраэователи. 10

Дополнительным преимуществом предложенного компаратора является усреднение входных сигналов на интервале стробирования входных транзисторов за счет интегрирования коллекторных токов с помощью емкостей.

Компаратор, содержащий генератор импульсов и две дифференциальные пары транзисторов, базы которых соединены с входными шинами компаратора, эмиттеры попарно объединены и через

25 соответственно первый и второй управляемые генераторы тока подключены к первой шине питания, а коллекторы первых транзисторов первой и второй дифференциальных пар объединены, и подключены к затвору первого полевого транзистора, коллекторы вторых транзисторов первой и второй дифференпиальных пар объединены и подключены к затвору второго полевого транзистора, стоки полевых транзисторов подключены к второй шине питания, а истоки через нагрузочные резисторы соединены с шиной нулевого потенциала и подключены соответственно к единичному и нулевым входам бистабильного элемента, выход которого соединен С выходной шиной, о т л и ч а ю щ и й— с я тем, что> с целью расширения функциональных возможностей за счет возможности сравнения сигналов,действующих в разные моменты времени, в него введены два элемента задержки, а объединенные коллекторы первых транзисторов дифференциальных пар и коллекторы вторых транзисторов дифференциальных пар подключены соответственно к первым выводам первого и второго конденсаторов И через управляемые ключи соединены с второй шиной питания, вторые выводы конденсаторов соединены с шиной нулевого потенциала, причем выход генератора импульсов подключен к управляющим входам ключей и входу первого элемента задержки, выход которого подключен к управляющему входу первого генератора тока и входу второго элемента задержки, выход которого подключен к управляющему входу второго генератора тока.