Устройство для умножения

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств для умножения двоичных и десятичных чисел. Целью изобретения является сокращение количества оборудования устройства. Цель достигнута за счет изменения функций второго и третьего корректирующих сумматоров 15 и 16 и связей между узлами устройства, что позволило исключить из устройства два корректирующих сумматора и один регистр задержки . В устройстве применен конвейерный принцип обработки ииформации с анализом в каждом такте двух десятичных цифр или же восьми двоичных цифр множителя . Устройство содержит регистры 1-3 сомножителей и результата, матрицу 4 умножения, регистры 5-9 задержс ки, сумматоры 10-13 и корректирующие сумматоры 14-17. 2 ил.

CQK)3 СОВЕТСНИХ (ОЦИАЛИСТИЧЕСНИХ

pECflYBfMH

А1 (19) (11) (511 4 G 06 F 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTVM (21) 3969376/24-24 (22) 24.10.85 (46) 07.07.87. Бюл. Р 25 (71) Минский радиотехнический институт (72) В.Л.Богомаз и А.А.Шостак (53) 681.325(088.8) (56) Авторское свидетельство СССР

В 1267408, кл. G 06 F 7/52, 05.03.85.

Авторское свидетельство СССР

Ф 842800, кл. С 06 F 7/52, 1979. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ (57) Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств для умножения двоичных и десятичных чисел. Целью изоб ретения является сокращение количества оборудования устройства. Цель достигнута эа счет изменения функций второго и третьего корректирующих сумматоров 15 и 16 и связей между узлами устройства, что позволило исключить из устройства два корректирующих сумматора и один регистр задержки. В устройстве применен конвейерный принцип обработки информации с анализом в каждом такте двух десятичных цифр или же восьми двоичных цифр множителя. Устройство содержит регистры

1-3 сомножителей и результата, матрицу 4 умножения, регистры 5-9 задерж ки, сумматоры 10-13 и корректирующие сумматоры 14-17. 2 ил.

1322266 нож(иие в3горогc) сомножителя, нлходящ го(я в реl истре ?, нл 8 двоичных разрядов (или же два десятичных разряда) первого сомножителя, цлходящег(-я в р«гистре 1, причем в зависимос ги от уровня потенциала нл входе

18 режима работы устройства на выходе ма грины 4 умножения формируются чстыре слагаемых либо в двоична-десяти (но>1 коде, либо в двоичном коде. !!атрицу 4 умно кения, как и в изНе)- f Hoof уг тройст(3е, мо,l;Ho реализовать

1 3 л и о < Т 31 ) H H O I t IT O lIV fl f> O E3 0 "(H HE (0 EJ O Ef П а мяти, Регистры 5-9 задержки являются синхронизируемыми и необходимыми для организации конвейерного метода умножения в устройстве.. Они предназначены для временного хранения промсжу45

Изобретение относится к вычисли— тельной технике и может быть использовано при разработке бис гродействун)щих устройств для умножеш(я двоичных и десятичных чисел . 5

Цель изобретения — сокращение количества оборудования устройства.

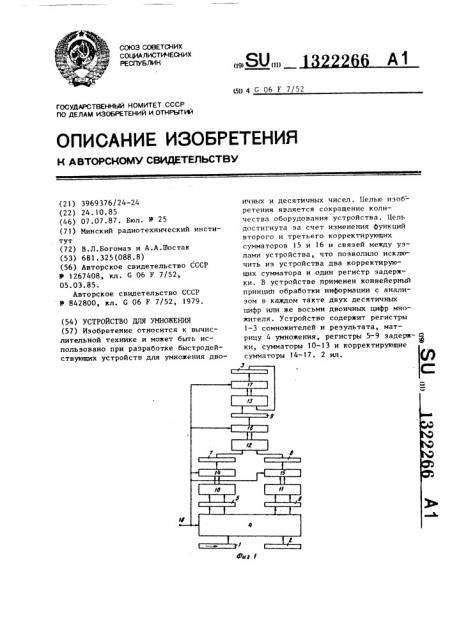

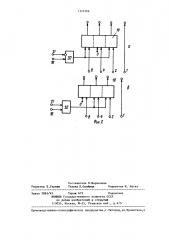

На фиг.l приведена структурная схема устройства для случля, когда на выходах матрицы умножения в од- 10 ном такте формируются четыре слагаемых; на фиг.2 — функциональные схемы тетрад корректирующих сумматоров, используемых в устройстве.

Устройство для умножения содержит 15 регистры 1 и ? первого и второго сомножителей соответстве(шо, рег истр 3 результл l л, матрицу 4 умноже(fitll регис гры 5-9 задержки, сумматоры 10-13, корректиру(ощие сумматоры 14-17 и 20 вход 18 рсж гмл работы устройства.

Тетрлдл корректирующего сумматора содержит tpeхрлзрядиый двоичный сумматор 19, элемент И 20, вход 21 пере25

flocks корректирующего сумматора.

Регис.тры и 2 первого и второго сомножителей предназначены для хранения цифр множителя и множимо го, причем регitcтр сдвигающий. !

3 реi èñòðo 3 результатл после заверше(шя операции умножения формируе ся о глршая часть произведения. Б г(роцсссе же выг(олнения умножения в нем време(но хранятся промежуточные р .3;- ) Il,l, o регистра

Г:.Il; l O, 1 flf ил()1.1Я IIOC) EIITHO длс c)I и устройс" .. — младшая часть

ПР О((э 13 e,:(P 3t Hÿ . ма 11»If(a 4 умг(3»кения выполняет ум3 3) IlfhIX Pl 3 УJII) Г;3 1 L)13 . (, IfH: !)О l) Х))) (Ы H P и )казаны.

Суммлтоphl 10 — 13 предил 3начеиы для суммирования промеж у г II« fx частич131>(х произведений.

Корректируя)щие сумм;(торы !4-17 необходимы для внесения коррекции при работе устройства в режиме десятично— го умги)жения. Корректирующие сумматоры 14 и 17 осуществляют вычитание шести путем прибавления +10. Функциональная схема тетрады этих сумматоров представлена на фиг.2а. Коррекция выполняется следующим образом.

Отсутствие переноса на входе 21 (фиг.2а) рлзрешает прибавление +10 к тетраде Н;3 3>уз(млторе 19, а присутствие rlepeiff)c:3 нл входе 21 позволяет пропускать тетраду через сумматор 19 транзитом. С;(едовательно, на выходе корректирующих сумматоров 14 и 17 информация формируется в естественном двоично-десятичном коде. Корректирующие су..(млторы 15 16 осуществляют

1 риблвле>(ие +6 (фиг.2б). В этом слу(а(коррекция осуществляется следующ((м обрл3oM.

Присутствие переноса на входе 21 пози )ляет добавление +6 к тетраде на сумматоре 19, а отсутствие переноса входе ?1 разрешает прохождс ие информ;.ции через сумматор 19 транзитом.

Поэтому на выходе корректирующих сумматоров 15 и 16 информация в(:)дается в

)fff()lt шо-десягичцом коде с избытком

3-6, Пр(ум((о)кс)(пш деся гичнь(х 11 двоичных чисе;(устройство рлботлст следующим образом.

Режим десятичного умцокен((я. При десятичном режиме умножения на каждом такте работы устройства осуществляется умножение двух десятичных цифр первого сомножителя, хранящегося в регистре 1, нл все цифры второ— го сомножителя, хранящегося в регистре 2. В первом такте управляющий сигнал на входе 18 режима работы устройства разрешает формирование на выходах матрицы 4 умножения четырех слагаемых, предстлвлеш(ых в двоично-десятичном коде, причем слагаемые первой и третьей гругп выходов матрицы 4 умножения предстлвлены в двоично-десятичном коде с избытком +6, а слагаемые второй и четвертой групп выходов матрицы 4 умножения представлены в рс ге(твенном двоично-десятичном коде. (l< р !i!.!

< I I I X < J l; l T ;1 < I! .! X « )> < I i < T ) i!, 5 ! 6

ДС )5Л Н I! .

ll:! < ..I< Лун»шс м т:.»н1 с .»ти же четыре

1322266 T :1 51 Ill < V» Ill I 1»l !ПО<и! ЯН11 < В< >!! <$)V!IT ! !! 1! бс » 5! .»с llf !!ия .

Ф с5 р м y ..! а и э о б р е т е н и я с.u «еi

1!а следующем третьем такте содержимое третьего регистра 7 задержки и четвертого регистра 8 задержки сум- !О мируется на третьем сумматоре !2, результат которого корректируется на третьем корректирующем сумматоре 16 и заносится в пятый регистр 9 задержки в двоично-десятичном коде с иэбыт-25 ком +6.

На четвертом такте содержимое пятого регистра 9 задержки суммируется на четвертом сумматоре 13 с содержимым регистра 3 результата (на данном ЗО такте оно равно нулю), сдвинутым на восемь разрядов вправо. Результат этого суммирования корректируется на четвертом корректирующем сумматоре 17 и заносится в регистр 3 результата в <5 естественном двоично-десятичном коде.

Все вышеописанные ступени устройства работают одновременно (параллельно), т.е. умножение выполняется по конвейерному принципу. О

Результат умножения побайтно в каждом такте выдается с регистра 3 результата, причем на заключительном такте умножения в этот регистр заносится старшая часть результата.

Режим двоичного умножения. Работа устройства при режиме двоичного умножения аналогична работе устройства при режиме десятичного умножения. От-50 личия состоят в том, что управляющий сигнал на входе 18 режима работы устройства настраивает корректирующие сумматоры 14-17 на пропуск через них информации транзитом, а также разрешает формирование на выходах матрицы

4 умножения четырех слагаемь!х, представленных в двоичном коде. Все ос стр< йство для умножения, соде ржащее регистры первого и втс рого сомножителей, регистр результата, Iaт— рицу умножсния, пять региг т ров »ад<. ржки, четыре сумматора и четыре корректирующих сумматора, причем выходь! регистров первого и второго сомножителей соединены с входами первого и второго сомножителей соответственно матрицы умножения, первая и вторая группы выходов которой соединены соответственно через первый и второй регистры задержки с входами первого и второго сумматоров, выходы суммы которых соединены с информационными входами соответственно первого и второго корректирующих сумматоров, выходы которых соединены с информационными входами соответственно третьего и четвертого регистров задержки, выход третьего регистра задержки соединен с первым информационным входом третьего сумматора, выходы суммы и переноса которого соединены с информационным входом и входом переноса соответственно третьего корректирующего сумматора, выход которого через пятый регистр задержки соединен с первым информационным входом четвертого сумматора, выходы суммы и переноса которого соединены с информационным входом и входом переноса соответственно четвертого корректирующего сумматора, выход которого соединен с информационным входом регистра результата, выходы переноса первого и второго сумматоров соединены с входами переноса соответственно первого и второго корректирующих сумматоров, входы разрешения коррекции которых соединены с входами разрешения коррекции третьего и четвертого корректирующих сумматоров, с входом задания режима умножения матрицы умножения и входом режима работы устройства, о т л и— ч а ю щ е е с я тем, что, с целью сокращения количества оборудования, выход четвертоro регистра задержки соединен с вторым информационным входом третьего сумматора, выход регистра результата соединен с вторым информационным входом четвертого сумматора.

1322266

Составитель Н.Маркелова

Редактор П.Гереаи Текред Л.Олийнык Корректор И. Муска

Заказ 2865/45 Тирах 672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, W-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.ухгород,ул.Проектная,4