Устройство для вывода информации

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано при создании ЭКВМ с памятью . Целью изобретения является расширение области применения устройства за счет обеспечения двунаправленного обмена информацией. Устройство содержит первый триггер 2, счетчик 3, первый, второй элементы ИЛИ 5, 6, первый генератор 7 импульсов, первый, второй элементы И 8,9, преобразователь 10 кодов, первый распределитель 11 импульсов, формирователь 12 пачки импульсов, коммутатор 17, второй, третий триггеры 18, 19, второй распределитель 20 импульсов, формирователь 21 импульсов, третий, четвертый, пятый элементы И 22, 23, 24 и второй генератор 25 импульсов. Устройство обеспечивает последовательные запись и чтение информации из памяти с.автоматической переадресацией. 3 ил. с € N)

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (Н 1 G 06 F 13/00

I у г

f с

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPCHOMY СВИДЕТЕЛЬСТВУ

Ый.;1 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1270762 (21) 4020034/24-24 (22) 10.02.86 (46) 07.07.87. Бюл. М- 25 (72) К.М.Ценных и В.В.Найденов (53) 681.3(088 ° 8) (56) Авторское свидетельство СССР

1270762, кл. С 06 F 13/00, 1985. (54) УСТРОЙСТВО ДЛЯ ВЫВОДА ИНФОРМАЦИИ (57) Изобретение относится к области вычислительной техники и может быть использовано при создании ЭКВМ с памятью. Целью изобретения является расширение области применения устройства эа счет обеспечения двунаправлен„.Я0„„1322292 А 2 ного обмена информацией ° Устройство содержит первый триггер 2, счетчик

3, первый, второй элементы ИЛИ 5, 6, первый генератор 7 импульсов, первый, второй элементы И 8,9, преобразователь 10 кодов, первый распределитель

11 импульсов, формирователь 12 пачки импульсов, коммутатор 17, второй, третий триггеры 18, 19, второй распределитель 20 импульсов, формирователь

21 импульсов, третий, четвертый, пятый элементы И 22, 23, 24 и второй генератор 25 импульсов. Устройство обеспечивает последовательные запись и чтение информации иэ памяти с автоматической переадресацией. 3 ил.

13222

Изобретение относится к вычислительной технике, может быть использовано при создании ЭКВМ с памятью и является усовершенствованием устройства по авт. св. У 1270762. 5

Цель изобретения — расширение области применения за счет обеспечения двунаправленного обмена информацией.

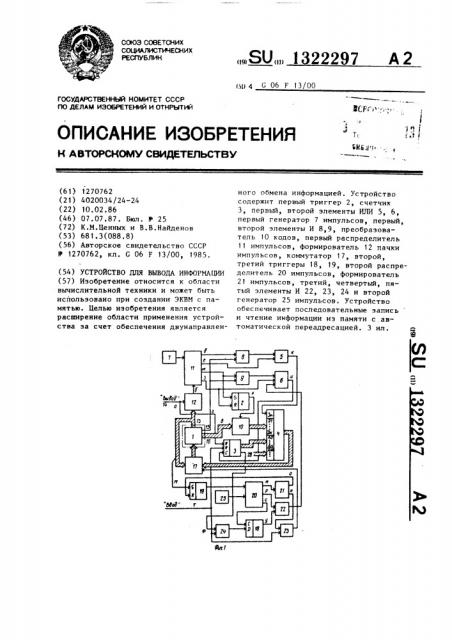

На фиг. 1 представлена структурная схвма устройства1 на фиг. 2 и 3 — вре-1О менные диаграммы его работы.

Устройство (фиг. 1) содержит арифметико-логическое устройство 1 электронной клавишной вычислительной машины (ЭКВМ), первый триггер 2, счетчик 3, блок 4 памяти, первый и второй элементы ИЛИ 5 и 6, первый генератор

7, первый и второй элементы И 8 и 9, преобразователь 10 кода, первый распределитель 11 импульсов, формирова- 20 тель 12 пачки импульсов, входы группы и вход которого являются соответственно входами 13 первой группы и первым входом 14 устройства, второй вход 15 и вход второй группы 16 устройства, коммутатор 17, второй и третий триггеры 18 и 19, второй распределитель 20 импульсов, формирователь

21 импульсов, третий, четвертый и пятый элементы И 22-24, второй гене- 30 ратор 25 импульсов.

Устройство работает следующим образом.

В исходном состоянии сигналом логического "О" по шинам Вывод" и 35

"Ввод" заблокированы счетчик 3, формирователь 12 пачки импульсов и четвертый и пятый элементы И 23 и 24.

Таким образом, второй триггер 18 находится в нулевом состоянии и блоки- 40 рует третий элемент И 22, с выхода которого сигнал логического "0" поступает на третий вход второго элемента

ИЛИ 6, а коммутатор 17 заблокирован сигналом логического "0", который по- 45 ступает с выхода четвертого элемента

И 23. Выходная информация арифметико-логического устройства 1 появляется поразрядно на его выходах, поступает на преобразователь 10 кода, а фазоимпульсно-кодированные синхросигналы арифметико-логического устройства 1 поступают на входы группы формирователя 12 пачки импульсов и на информационные входы коммутатора

17.

При выводе информации из арифметико-логического устройства 1 в блок 4 с!7 2 памяти устройство работает следующим образом.

С приходом по шине 14 сигнала "Вывод" (фиг. 2л) снимается блокировка со счетчика 3, а формирователь 12 формирует пачку импульсов (фиг. 2Б), число которых соответствует числу разрядов выводимой информации (фиг.2ь ).

Причем первый импульс в пачке совпадает по фазе с синхросигналом, соответствующим младшему (старшему) разряду выводимой информации, второй импульс совпадает со следующим разрядным сигналом и т.д.

Передним фронтом каждого импульса иэ пачки запускается распределитель

11 импульсов, который вырабатывает четыре импульса, сдвинутых относительно друг друга на один такт выходной частоты первого генератора 7 (фиг.2д, е, ж, з). Первым из этих импульсов первый триггер 2 устанавливается в единичное состояние, третьим сбрасывается в нулевое состояние (фиг.2л), а преобразователь 10 кода в первом случае выдает код запятой, во втором— преобразованный код разряда выходной информации арифметико-логического устройства 1.

Сигналы (фиг. 2u), поступающие на счетный вход счетчика 3 с выхода второго элемента ИЛИ 6, устанавливают адрес разрядов числа, вводимого в блок 4 памяти, на входы адреса числа которого поступает код адреса числа, а сигналы с первого элемента ИЛИ

5 осуществляют запись информации в блок 4 памяти. Однако запись кода запятой возможна лишь в том случае, когда с выхода запятой 15 арифметикологического устройства 1 на входы элементов И 8 и 9 поступит разрешение (сигнал запятой). В этом случае за время действия разрядного сигнала адрес разряда числа блока 4 памяти изменяется дважды, и дважды поступает сигнал записи (фиг. 2и к). Первым сигналом осуществляется запись кода запятой, а вторым — запись информации, соответствующей данному разрядному сигналу.

По окончании последнего импульса формирователя 12 и сигнала "Вывод" устаройство переходит в исходное состояние. Для нормального функционирования устройства сигнал "Вывод" должен быть длительностью не менее двух периодов частоты синхросигналов, в

13222 противном случае нозможен вывод не всех разрядов информации.

В режиме "Ввод (фиг. 3) устройство работает следующим образом.

В исходном состоянии на адресные входы числа блока 4 памяти ло входной шине 28 устройства поступает код адреса вводимого числа. С приходом в момент t, сигнала "Ввод", синхронизированного с началом второго импульса 10 второго распределителя 20 импульсов (фиг. Зр т), разблокируются четвертый и пятый элементы И 23 и 24 и счетчик 3, с выхода которого на адрес ные входы разрядов числа блока 4 па-,5 мяти поступает в этот момент нулевой код адреса младшего (старшего) разряда вводимого числа. Передним фронтом третьего импульса (фиг. Зс, ) второй триггер 18 устанавливается 20 в единичное состояние, разблокируя третий элемент И 22. С выходов арифметико-логического устройства 1 на информационные входы коммутатора

17 поступают синхросигналы, а на его 25 управляющие входы с выхода блока 4 памяти поступает код младшего (старшего) разряда вводимого числа. В момент времени t, (фиг. Зн) с первого выхода формирователя 21 импульсов 30 через третий элемент И ?2 на вход запрета коммутатора 17 приходит сигнал разрешения и определенный синхросигнал в соответствии с кодом разряда поступает на соответствующий вход арифметико-логического устройства 1.

За период времени t -tz (фиг. Зм) в арифметико-логическом устройстве

1 происходит "Захват" синхросигнала (например, для АЛУ 145 ИП 7, 145 ИП 40

12 это время равно 2-3-M периодам синхросигнала), а в интервале времени t -t происходит выполнение арифметико-логическим устройством 1 операции ввода первого разряда числа.45

Это время определяется быстродействием арифметико-логического устройства 1, причем синхросигналы на его выходах в это время отсутствуют (фиг.Зм) и появляются вновь лишь в момент време-5 ни t> (фиг. Зм), что свидетельствует об окончании ввода разряда числа в арифметико-логическое устройство 1.

Третий триггер 19 при этом устанавливается в единичное состояние, так как55 в момент t он разблокируется сигнал лом с второго выхода формирователя 21 ° импульсов (фиг. 3 в) . Сигналом логической "1" с выхода третьего триггера

97 4

19 запускается второй распределитель

20 импульсов, выходным сигналом которого запускается формирователь 21 импульсов (фиг. 3 н, о, л) . При этом пер вым импульсом второго распределителя

20 импульсов блокируются третий триггер 19 и коммутатор 17, а второй импульс (фиг. Зр) устанавливается на выходах счетчика 3 код следующего разряда вводимого числа, который поступает на входы адреса разрядов числа блока 4 памяти. С выхода последнего код этого разряда поступает на управляющие входы коммутатора 17.

После появления в момент t синхро3 сигналов через определенное время (например, для арифметико-логических устройств 145 серии

7-10 мс) арифметико-логическое устройство 1 готово к вводу следующего разряда числа.

В момент времени t разблокируется коммутатор 17 после чего осуществляется ввод в арифметико-логическое устройство 1 следующего разряда числа. Аналогичным образом происходит ввод остальных разрядов числа.

Сигнал с первого выхода формирователя 21 импульсов (фиг. Зн) обеспечивает необходимую задержку ввода разряда числа, а сигнал с второго выхода — с помощью третьего триггера 19 запуск второго распределителя 20 импульсов только после окончания ввода предыдущего разряда. Этим достигается максимальное быстродействие устройства при вводе.

В момент появления на выходах счетчика 3 кода адреса последнего вводимого разряда, íà его выходе переноса появляется сигнал логического "0" (фиг. Зу), который блокирует пятый элемент И 24. Третьим импульсом с выхода второго распределителя 20 импульсов второй триггер 18 сбрасывается в "0" (фиг. 3 ) и запрещает тем самым прохождение импульсов через четвертый элемент И 22 на вход счетчи" ка 3.

По окончании ввода в арифметикологическое устройство 1 последнего разряда числа в момент времени t (фиг. 3 р,т) сигнал "Ввод" сбрасывается в "0", блокируя счетчик 3 и четвертый и пятый элементы И 23 и 24, и устройство возвращается в исходное состояние.

1322297

Формула изобретения

Устройство для вывода информации по авт. св. У 1270762, о т л и ч а ющ е е с я тем, что, с целью расширения области применения за счет обеспечения двунаправленного обмена информацией, в него введены коммутатор, второй и третий триггеры, второй распределитель импульсов, формирователь 10 импульсов, третий, четвертый и пятый элементы И и второй генератор импульсов, причем выход второго генератора импульсов соединен с тактовым входом второго распределителя импульсов, 15 первый, второй, третий выходы которого соединены соответственно с входом формирователя импульсов, первым входом третьего элемента И, входом синхронизации второго триггера, выход которо- 20 го соединен с вторым входом третьего элемента И, выход которого соединен с третьим входом второго элемента ИЛИ, первый, второй выходы формирователя импульсов соединены соответственно с 25 входом сброса третьего триггера и первым входом четвертого элемента И, выход которого соединен с управляющим входом коммутатора, выход которого соединен с выходом устройства для подключения по входу данных ЭКВМ выход третьего триггера соединен с входом запуска второго распределителя импульсов, первый вход пятого элемента И соединен с выходом счетчика, вход сброса которого соединен с вторыми входами четвертого, пятого элементов И и входом устройства для подключения выхода задания команды ввода информации ЭКВМ, выход пятого элемента И соединен с информационным входом второго триггера, первый и второй информационные входы коммутатора соединены с выходами устройства для подключения соответственно группы выходов синхронизации ЭКВМ и выхода данных памяти, установочный вход третьего триггера соединен с входом устройства для подключения выхода синхронизации ЭКВМ.

1322297

r 4 4

Составитель С.Бурухин

Редактор Н.Рогулич Техред И.Попович Корректор А.Обручар

Заказ 2866/46 Тирам 672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Уигород, ул. Проектная, 4