Устройство для определения среднего арифметического электрических величин

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для повышения достоверности результатов обработки информации , получаемой с помощью частотных датчиков. Целью изобретения является повышение быстродействия. Поставленная дель достигается тем, что в устройство , содержащее п входных каналов , каждый из которых содержит формирователь 1 импульсов, генератор 3 тактовых импульсов с п тактовыми импульсами , дополнительно включены группа элементов И 9 и элемент ИЯИ 1 3.п. ф-лы. 2 ил. 10. (Л f/ 2п 8, вп Фиг1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (5D G 06 F 15/36

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3856684/24-24 (22) 10. 12. 84 (46) 07.07.87. Бюл. № 25 (72) 3.Ш.Батршин, В.Б.Дудыкевич, Л.Т.Пархуць, 3.M.Ñòðèëåöêèé и И.В ° Маслий (53) 681.333 (088.8) (56) Авторское свидетельство СССР № 1140134, кл. С 06 F 15/36, 7/52, 1984.

Авторское свидетельство СССР

Ф 635491, кл. С 06 F 15/36, 1978. (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СРЕДНЕГО АРИФМЕТИЧЕСКОГО ЭЛЕКТРИЧЕСКИХ

ВЕЛИЧИН (57) Изобретение относится к вычислительной технике и может быть использовано для повышения достоверности результатов обработки информации, получаемой с помощью частотных датчиков. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в устройство, содержащее и входных каналов, каждый из которых содержит формирователь 1 импульсов, генератор 3 тактовых импульсов с и тактовыми импульсами, дополнительно включены груп» па элементов И 9 и элемент ИЛИ 10.

1 э.п. ф-лы. 2 ил.

1322313

А +А,+А + А4

СР 4 (2) где А, г

<

Аналог ние (2) з (3) 40

1

-л

-<

< с(>

+ — f +

50 пре55 вревреИзобретe!! tte От нос><тся е вычислительной технике и может быть иснользовано для повышения достоверности результатов обработки инсрормациг1,110 лучлемой с помощью частотных датчиков.

Цель изобретения — повышение быстродействия.

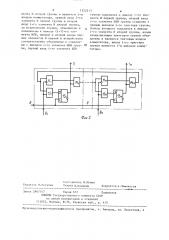

На фиг.! представлена блок-схема устройства; на фиг.2 — один из вари- 10 литов коммутатора каналов.

Устройство для определения среднего лр1!фметического электрических вели 1ин содержит формировл гели 1, — 1„ импульсов, элементы И 2, -2„, генератор 3 импульсов, однов!!брлторы 4, -4„, КОЕ!МУ! Л ОР > КЛ tlË31013 ) ТЛЕТ 01<ый 13ХГ>ГI

6, г<ыход11 ко!!мутa! орл 7, -7„11 вхо3(ы и, 11 и „коммутаторл, блок 9 элеменго 3 (!;! . let te;гг ИЛИ 10. 20 ! о 1::утлтор 5 клнл!Iîв (<,>1I! . 2) содер>11>п первую и вторую группы э:1е:.tet!тов ((11, — 11„и (2, — 12„, D-тр !ггсры 13, — 13„и группу эл! ментов (ПИ

25 и

Устройство рлботает слсцующим образом.

В начальный моме1!т в первом Dтр !ггере 13, за!нисана единица (цепи .<Я1 !си нс уелзлны) . ((р!1 подаче нл

30 т lftòîl!l" 1 нхсд 6 глкто1<ых !,мпу.!ьсов

1!р«р .ботл : елнллл:; (т. е. нл входа; 8< — Ы „нлхо,ill I ся 101 !ческ;3я еди1!t!!to) нл пыходлх ttð011. Еод!!т сдвиг J!o гlt се! и «;лип<ли.. слн отклжет 1 акой- 35 . !1< по 1;;i! . 1.1 > ил с 0<3т13 етс г13у!Ощеt :3::0

Р !С!!(!< ;1e!!;IТС,ГIЯ ПОЯВ!!ТСЯ !01 IIЧОСЕllй

11<>.! !1, т1!I т О > О Й л 013 j> < . .г,,! e t K tl!! 11 (С01:3!угл< ор 5, б:!Ое 9 >лемснто!3 (!

>."Оме>гг Ц:((! 10 представ:IJ::<:т «nt OII ,.; 1:!тet.t ч;1стОты. ! 0!11! t« t3 1 Ь 0 и !Пул ЬС Ог< н<1 ВЫ,Î;J<

>лом !If;l (f!((f 10 Описывается урл! не111> 0: !

3 4 3

+ —,b + —,с + —,d + —,е +

4 4 (1) где . — количество тактов за 13ре: !11 <> С (3 ЕОЛИ<1ЕСТВО ТЛЕТОВ Э

МЯ

Ii0JIlI

e — количество тактов за время — количество тактов за время 61-6 ъ — количество тактов за вре<> 7 °

Уравнение (1) можно записать в следующем виде а+Ь+с+

b+c+d+e;

0+d+e+

d+e+ f +q. ично для п каналов уравнеапишется, A.

3=<

А и

<(> о р м у л л и 3 о б р е т е н и я

1. Устройство для определения среднего арифметического электрических величин содержащее г! формирователей и1!13ульсов, N одновибраторов, генератор импульсов, группу из N элемеHT013 И, первый вход i-гo элемента

1! группы (i = 1-N) объединен с входом

1-I o одиовибраторл и подключен к выходу I.-ro формирователя импульсов, вход которого является i-м информационн1!1! входом устройства, о т л ич а ю щ е е = я тем, что, с целью повышеьн1я быстродействия, в него

1313едены, блок элементов И, элемент

ИЛ((, коммутатор каналов, выход генерлторл 11мпугьсов подключен к вторым вхоцам элементов И группы и управляю11!ему входу коммутаторов каналов, выходы которого подключены к первой группе входов блока элементов И, вторая группа входов которого соединена с vxoptt!»t э;!ементов И группы, выходы блока элементов И подключены к вхор 3.! э «!!ен a ИJ(И, выход которого явцяется выходом устройства.

2. Устройство по п.1, о т л и ч л ю щ е е с я тем, что коммутатор кана.!ов содержит первую и вторую группы элементов И, группу элементов

ИЛИ, группу триггеров, информационный вход .-го триггера группы подключен к выходу i-ro элемента И первой группы, инверсный вход которого

Объединен с первьгм входом i-го эле1322313

Рие 2

Составитель И.Мухин

ТехРед Л ° Олейник Корректор A. Зимокосов

Редактор Н.Рогулич

Заказ 28б7/47 Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 мента И второй группы и является i-м входом коммутатора, прямой вход i-го элемента И первой группы и второй вход i-ro элемента И второй группы, за исключением первых, объединены и подключены к выходу (i-1)-го элемента ИЛИ, прямой и второй входы первых элементов И первой и второй групп соответственно объединены и соединены с выходом i-го элемента ИЛИ груп- 10 пы, первый вход i-го элемента ИЛИ группы подключен к выходу i-го элемента И первой группы, второй вход

i-го элемента HJIH группы соединен с прямым выходом i-го триггера группы, D-вход которого подключен к выходу

i-го элемента И второй группы, входы синхронизации тригтеров группы объединены и являются тактовым входом коммутатора, выход i-ro триггера группы является i-м выходом коммутатора,