Регистр последовательного приближения

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники, в частности может быть использовано в аналого-цифровых преобразователях поразрядного уравновешивания . Изобретение позволяет повысить надежность и упростить схемотехническую реализацию регистра последовательного приближения путем использования в каждом разряде JK-триггера по типу «основной-вспомогательный и двух элементов И на каждый разряд, кроме последнего. Входы перво го элемента И каждого разряда соединены с шиной управления и единичным выходом JK-триггера этого разряда, выход первого элемента И подключен к К-входу триггера. Прямые выходы предыдущих триггеров подключены к J-выходу последующих триггеров . Входы вторых элементов И подключены к тактовому и нулевому выходам последующего триггера, а выход этого элемента соединен с триггером своего разряда. Тактовые импульсы поступают на тактовый вход последнего разряда. К-вход триггера последнего разряда соединен с щиной логического нуля, а J-вход триггера первого разряда - с щиной логической единицы. 1 ил. & (Л ел К5 Ю Nj СЛ 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (51) 4 Н 03 К 17 62

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 3801849/24-24 (22) 10.10.84 (46) 07.07.87. Бюл. № 25 (72) Л. В. Челпанов (53) 621.372.3 (088.8) (56) Авторское свидетельство СССР № 822367, кл. Н 03 К 17/62, 1979.

Балакай В. Г. и др. Интегральные схемы аналого-цифровых и цифроаналоговых преобразователей. — М.: Энергия, 1978, с. 207, рис. 6 — 5. (54) РЕГИСТР ПОСЛЕДОВАТЕЛЬНОГО

ПРИБЛИЖЕНИЯ (57) Изобретение относится к области вычислительной техники, в частности может быть использовано в аналого-цифровых преобразователях поразрядного уравновешивания. Изобретение позволяет повысить надежность и упростить схемотехническую реа„„SU„„1322458 A 1 лизацию регистра последовательного приближения путем использования в каждом разряде JK-триггера по типу «основной — вспомогательный» и двух элементов И на каждый разряд, кроме последнего. Входы перво го элемента И каждого разряда соединены с шиной управления и единичным выходом

JK-триггера этого разряда, выход первого элемента И подключен к К-входу триггера.

Прямые выходы предыдущих триггеров подключены к J-выходу последующих триггеров. Входы вторых элементов И подключены к тактовому и нулевому выходам последующего триггера, а выход этого элемента соединен с триггером своего разряда. Тактовые импульсы поступают на тактовый вход последнего разряда. К-вход триггера последнего разряда соединен с шиной логического нуля, а J-вход триггера первого разряда— с шиной логической единицы. 1 ил.

1322458

Формула изобретения

Изобретение относится к вычислительной технике и может быть использовано в аналого-цифровых преобразователях поразрядного уравновешивания.

Цель изобретения — повышение надежности и упрощение схемотехнической реализации регистра последовательного приближения.

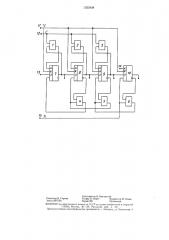

На чертеже представлена функциональная схема регистра последовательного приближения.

Регистр последовательного приближения содержит элементы И 1 — 6, JK-триггеры

7 — 10, шины 11 начальной установки, шину 12 управления, 13 логической единицы, 14 логического нуля и 15 тактовых импульсов.

Регистр последовательного приближения работает следующим образом.

Все JK-триггеры 7 — 10 переключаются в нулевое состояние воздействием на входы

R импульса с шины 11 начальной установки.

Первый тактовый импульс с шины 15 тактовых импульсов проходит последовательно через элементы И 6, 5, 4 на тактовые входы всех JK-триггеров 7 — 10 и по заднему фронту переключает в единичное состояние JKтриггер 7, у которого J-вход подключен к шине логической единицы. Второй тактовый импульс также воздействует на тактовые входы всех JK-триггеров 7- — 10 и по его заднему фронту переключается в единичное состояние JK-триггер 8. Аналогично устанавливаются в единичное состояние остальные триггеры регистра.

При работе регистра в составе аналогоцифрового преобразователя сигнал на шине 12 управления„соответствующий логической единице, свидетельствует о перекомпенсации, и одновременно с установкой в единицу очередного триггера предыдущий триггер дол жен устанавливаться в «0».

Рассмотрим случай, когда необходимо отработать код 1100 на шине 12 управления.

До начала отработки все JK-триггеры 7—

1О переводятся в состояние «0». По первому элементу кода JK-триггер 7 переключается в единичное состояние, остальные триггеры остаются в состоянии «О». По второму эле5

10 15

2 менту кода JK-триггер 8 переключается в единичное состояние, JK-триггер 7 переводится в состояние «О», остальные триггеры остаются в состоянии «О». По третьему элементу кода JÊ-триггер 9 переключается в единичное состояние, JK-триггер 8 переключается в состояние «О», остальные триггеры остаются в состоянии «О». По четвертому элементу кода JK-триггер 10 переключается в единичное состояние, JK-триггер 9 остается в единичном состоянии, JK-триггеры 7 и 8 остаются в состоянии «1». Таким образом, на регистре устанавливается код 0011, обратный коду на шине 12 управления. В последнем младшем разряде устанавливается состояние «1», что соответствует измерению с избытком.

Регистр последовательного приближения, каждый разряд которого, кроме последнего, содержит первый и второй элементы И, первый вход первого элемента И каждого разряда подключен к шине управления, шину начальной установки и шину тактовых импульсов, отличающийся тем, что, с целью повышения надежности и упрощения схемотехнической реализации, каждый из разрядов содержит JK-триггер, тактовый вход

JK-триггера каждого разряда, кроме последнего, соединен с выходом второго элемента И первый и второй входы которого соединены соответственно с тактовым входом и нулевым выходом JK-триггера последующего разряда, тактовый вход JÊ-триггера последнего разряда подключен к шине тактовых импульсов, единичный выход JK-триггера каждого разряда соединен с J-входом JKтриггера последующего разряда и с вторым входом первого элемента И, выход которого подключен к К-входу JK-триггера своего разряда, причем J-вход JK-триггера первого разряда и К-вход JK-триггера последнего разряда подключены соответственно к шинам логической единицы и логического нуля, а шина начальной установки соединена с R-входами JK-триггеров всех разрядов.

1322458

11 1Г

Составитель В. Выговскнй

Редактор И. Горная Техред И. Верес Корректор М. Пожо

Заказ 2877/54 Тираж 901 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1! 3035, Москва, К вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4