Преобразователь двоичного кода в двоично-десятичный

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и цифровой вычислительной техники и может быть использовано при построении двоично-десятичных преобразователей . Целью изобретения является упрощение преобразователя. Поставленная цель достигается тем, что преобразователь двоичного кода в двоично-десятичный , содержащий первый сумматор 2, первый регистр 4, схему сравнения 6, первый и второй двоично-десятичные Счетчики 10, II, первый и второй элементы И 8. 9 и элемент ИЛИ 7, содержит второй сумматор 1 и второй регистр 3, входы которого соединены с выходами двоично-десятичных счетчиков 10, 11, входы обратного и прямого счета которых соединены с выходами первого и второго элементов И 8, 9, выходы первого счетчика 10 соединены с первыми входами второго сумматора 1, вторые входы которого соединены с выходами первого регистра 4, а выходы первого сумматора 2 соединены с вторыми входами схемы сравнения 6. 1 ил. сл со to ю 4 00 KD

СОЮЗ СОВЕТСНИХ, СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) А1 (5)) 4 Н 03 М 7/12

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3885179/24-24 (22) 16. 04. 85 (46) 07.07.87. Бюл.Ф 25 (71) Харьковский государственный университет им. А.M.Ãîðüêoãî (72) В.Ф.Боронило, В.П.Середа, С.К.Бесчастных, В.И.Мелешко и !О.Л.Нуров (53) 681.325(088.8) (56) Авторское свидетельство СССР

Р 1124282, кл. H 03 M 7/12, 1983.

Авторское свидетельство СССР

Р 1266008, кл. Н 03 M 7/12, 1984. (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА

В ДВОИЧНО-ДЕСЯТИЧНЫЙ (57) Изобретение относится к области автоматики и цифровой вычислительной техники и может быть использовано при построении двоично-десятичных преобразователей. Целью изобретения является упрощение преобразователя. Поставленная цель достигается тем, что преобразователь двоичного кода в двоично-десятичный, содержащий первый сумматор 2, первый регистр 4, схему сравнения 6, первый и второй двоично-десятичные счетчики 10, 11, первый и второй элементы И 8, 9 и элемент ИЛИ 7, содержит второй сумматор 1 и второй регистр 3, входы которого соединены с выходами двоично-десятичных счетчиков 10 11, входы обратного и прямого счета которых соединены с выходами первого и второго элементов И 8, 9, выходы первого счетчика !О соединены с первыми входами второго сумматора I, вторые входы которого соединены с выходами первого регистра 4, а выходы первого сумматора 2 соединены с вторыми входами схемы сравнения 6. 1 ил.

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построе1 ии двоично-десятичных преобразователей.

Цель изобретения — упрощение преобразователя.

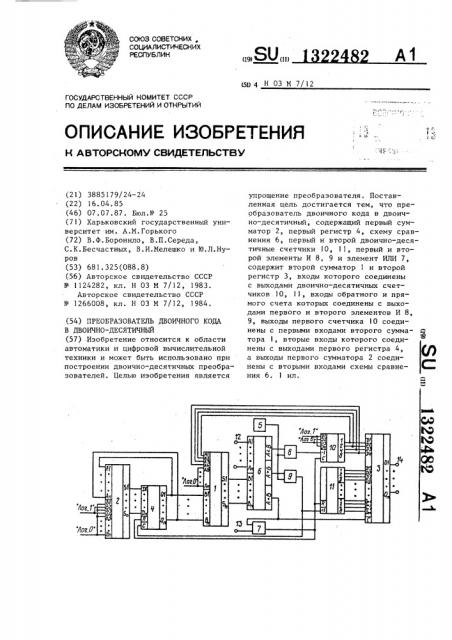

На чертеже представлена функциональная схема преобразователя двоичного кода в двоичпо-десятичный.

Преобразователь содержит сумматоры 1 и 2, регистры 3 и 4, генератор

5 импульсов, схему 6 сравнения, элемент ИЛИ 7, первый и второй элемент

И 8 и 9, первый и второй двоично-десятичные счетчики 1О и 11, информационный вход 12, вход 13 установки, выходы 14 преобразователя. !

Преобразователь работает следующим образом.

В начале преобразо:вания на вход

13 установки подается сигнал, который устанавливает в нулевое состояние второй регистр 4 и второй двоично-десятичный счетчик 11, а в первый двоично-десятичный счетчик 10 записывает двоичный код числа 9 . Этот код складывается на сумма". îðå .1 с нулевым кодом регистра 4 и поступает на схему 6 сравнения для сравнения с преобразуемым двоичным кодом, поступающим на схему сравнения с входов

12. Если преобразуемый код больше кода числа "9", то на втором выходе

"A) В" схемы 6 сраьнения появляется сигнал уровня логической единицы, который разрешает происхождение тактовых импульсов с генератора 5 импульсов через второй элемент И 9 на вход прямого счета второго двоично-десятичного счетчика 11 и синхровход регистра 4. При этом с каждым тактовым импульсом содержимое регистра 4, а значит и двоичного числа на выходе первого сумматора 1, будет увеличиваться на двоичное число "10", а второй двоично-десятичный счетчик !1 будет подсчитывать количество тактовых импульсов, которые, в данном случае, имеют вес "десятков" выходного двоично- десятичного кода. Этот процесс продолжается до тех пор, пока двоичное число на выходе первого сумматора 1 становится равным или превышает преобразуемый,цвоичный код.

Если число на выходе первого сумма.— тора превышает преобразуемый дво5

10 !

26

4G

50 ,55 ичный код, ro с второго выхода "А . В" исчезнет, а на третьем выходе "А В" схемы 6 сравнения появляется сигнал уровня логической единицы, который разрешает прохождение тактовых им-. пульсов с генератора 5 импульсов через первь.й элемент И 8 на вход обратного счета первого двоично-десятичного счетчика 10, в который был предварительно записан двоичный код числа "9", С каждым тактовым импульсом это число уменьшается на единицу, соответственно уменьшается двоичное число на вьходе первого гумматора !.

В момент ра.венства этого числа преобразуемом,цвоичному коду на третьем выходе "А < В" исчезает, а на первом выходе А-В схемы 6 сравнения появляется сигнал уровня логической единицы, по которому числа с выходов первого и второго двоично-десятичных счетчиков 10 и 11, имеющих соответственно вес единиц и десятков, переписываются в регистр 3 и устанавливаются на выходах 14 преобразователя. Этот же сигнал через элемент

ИЛИ 7 устанавливает преобразователь н исходное состояние. ! формула изобретения

Преобразователь двоичного кода в двоично-десятичный,, содержащий генератор импульсов, схему сравнения, первый и второй двоично-десятичные счетчики, первый регистр, первый сумматор, элемент ИЛИ, первый и второй элементы И, первые входы которых соединены с выходом генератора импульсов, а вторые входы соответственно соединены с выходами "Больше" и "Меньше" схемы сравнения, первая группа входов которой соединена с информационными входами преобразователя, выходы первого сумматора соединены с информационными входами первого регистра, выходы которого соединены с первой группой входов первого сумма-. тора, о т л и ч а к> шийся тем, что, с целью упрощения преобразователя, он содержит второй сумматор и второй регистр, входы которого соединены с выходами первого и второго двоична-десятичных счетчиков, входы обратного и прямогo c e KoTo b co ответственно соединены с выходами первого и второго элементов И, выход

Равнол схемы сравнения соединен с входом записи второго регистра и с

3 1322482 4 первым входом элемента ИЛИ, выход ко- кой единицы преобразователя соединен торого соединен с входами сброса вто- с информационными входами первого и рого двоично десятичного счетчика и четвертого разрядов первого двоичнопервого регистра и с синхровходом пер- десятичного счетчика и с входами нтового двоично-десятичного счетчика, 5 рой группы второго и четвертого развыходы которого соединены с входами рядов второго сумматора, входы ос тальмладших разрядов второго сумматора, ных разрядов второй группы которого вторая группа входов которого соеди- соединены с входом логического нуля иена с выходами первого регистра, преобразователя, вход установки ковходы старших разрядов первой группы 10 торого соединен с вторым входом элевторого сумматора соединены с входом мента ИЛИ, выход второго элемента И логического нуля преобразователя, вы- соединен с синхровходом первого реходы которого соединены с выходами гистра, информационные входы второго второго регистра, выходы второго сум- и третьего разрядов первого двоичноматора соединены с второй группой 15 десятичного счетчика соединены с вховходов схемы сравнения, вход логичес- дом логического нуля преобразователя. !

Составитель Н.Шелобанова

Редактор Е.Папп Техред А.Кравчук Корректор С.Шекмар

Заказ 2878/55 Тираж 901 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4