Преобразователь двоичного кода в код системы остаточных классов

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТ ИЧЕСНИХ

РЕСПУБЛИК (19) (11) (5и 4 Н 03 М 7/18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АBTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ. (21) 3904323/24-24 (22) 03.06.85 (46) 07.07.87. Бюл. W- 25 (72) В.А. Иванченко, П.Л. Прокопьев и В.Н. Торопов (53) 681.3 (088.8) (56) Авторское свидетельство СССР

М 1269271, .кл. Н 03 M 7/18, 1985.

Авторское свидетельство СССР

Р 1176383, кл. Н 03 M 7/18, 1984. (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА

В КОД СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ (57) Изобретение относитсяк вычислительной технике. Целью изобретения является упрощение преобразователя.

Поставленная цель достигается тем, что в преобразователе, содержащем входной регистр, сумматор по модулю

Р, блок умножения на константу по модулю Р, два регистра и коммутатор, изменены связи между блоками устройства. 1 ил.

13224 раэователя.

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах для перевода чисел из двоичной позиционной системы в систему остаточных классов„

Цель изобретения — упрощение преобразователя.

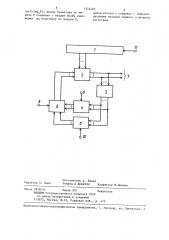

° На чертеже представлена схема преобразователя двоичного кода в f0 код системы остаточных классов.

Преобразователь содержит входной регистр 1, сумматор 2 по модулю Р, блок 3 умножения на константу по модулю Р, первый и второй регистры 4 15 и 5, коммутаор 6, выход 7 преобразователя, тактовые входы 8-11 преобразователя, Пусть Р имеет разрядность (и+1).

Тогда любое число В, имеющее разряд- 20 ность и, будет меньше P. В этом случае процесс преобразования числа Х можно представить в виде (Х) =(... (О+В,) 2 ) +...+В, ) где н-

В„=А 2 +...+А <(„, )н

k+1

«1=О l

Ю ° 1

m-1

1 и

Преобразователь двоичного кода

B код системы остаточных классов работает следующим об1:азом.

В исходное состоянии íà. входном регистре 1 находится значение преобразуемого числа, регистры 4 и 5 обнулены, коммутатор 6 подключает выход регистра 4 к входу первого слагаемого сумматора 2.

В первом такте значение и стар- 40 ших разрядов преобразуемого числа (В,) из входного регистра 1 поступает на вход второго слагаемого сумматора

2 по модулю, откуда они передаются на вход блока 3 умножения. По окончании 45 переходных процессов на вход 9 преобразователя поступает сигнап, по которому результат принимается на регистр 4.

Б начале второго такта па сигналу, поступающему на тактовый вход 11, осуществляется сдвиг на и разрядов влево содержимого входного регистра

1. Содержимое регистра 4 суммируется со значением В на сумматоре 2, откуда результат поступает на блок 3 умножения. По окончании переходных процессов на вход 10 поступает так83 2 товый сигнал, по которому результат запоминается на регистре 5.

Б начале третьего такта осуществляется сдвиг содержимого регистра

l на п разрядов влево по сигналу, поступающему на вход ll а по сигналу, поступающему на вход 8, коммутатор 6 подключает выход регистра 5 к входу первого слагаемого сумматора 2.

Значение В суммируется с содержи2 мым регистра 5, полученный на сумматоре 2 резупьтат поступает на вход блока 3 умножения. По окончании переходных процессов на вход 9 поступает тактовый сигнал. по которому результат заносится в регистр 4. И так далее.

Б начале последнего такта осуществляется сдвиг íà и разрядов содержимого входного регистра 1 ° Результат предыдущего такта суммируется с В. на сумматоре 2 и умноtYl — 1 жается по модулю на блоке 3 умножения. Окончательный результат преобразования снимается с выхода 7 преобЛополнительный положительный эффект изобретения состоит в увеличении тактовой частоты работы, Ф о р м у л а и э о б р е т е н и я

Преобразователь двоичного кода

B:

P., коммутатор, первый и второй регистры, выходы которых соединены соответственно с первым и вторым информационными входами коммутатора, управляющий вход коммутатора, входы разрешен 1я приема первого и второго регистров, вход разрешения сдвига входного регистра соединены соответственно с тактовыми входами с первого по четвертый преобразователя, выход сумматора по модулю P является выходом преобразователя, отличаю-щийся тем,что, с целью упрощения преобразователя, выхоц коммутатора соединен с входом первого слагаемого сумматора по модулю Р, вход второго слагаемого которого соединен с:выходом и старших разрядов входного регистра

1322483 4 выход которого соединен с информационными входами первого и второго регистров. (n+l log P) выход сумматора по модулю P соединен с входом блока умножения на константу по модулю Р, Составитель А. Клюев

Техред A.Êðàâ÷óê Корректор М.Демчик

Редактор Е. Папп

Заказ 2878/55 Тираж 901 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

II3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4