Устройство для приема дискретных сообщений

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи . Цель изобретения - повьшение помехоустойчивости. Устр-во содержит эл-т задержки 1, фазовращатель 2, перемножители 3,4,7 и 8, интеграторы 5 и 6, блоки задержки 9 и 10, сумматор 11, дискриминаторы 12,13 и 14 полярности , регистры 15,16 и 17 сдвига, коммутатор 18, декодер 19, блок синхронизации 20 ц блок управления (БУ) 21. Последовательности эл-тов передаваемых бх. кодовых комбинаций (КК) с выходов дискриминаторов 12, 13 и 14 на протяжении каждой КК заполняют регистры 15, 16 и 17. После приема последнего эл-та КК содержимое регистров 15j 16 и 17 поочередно (в любой последовательности ) через коммутатор 18, который управляется БУ 21, передается в декодер 19. Декодер 19 производит обнаружение ошибок в поступающих в него КК и, если ошибки не обнаружены , БУ 21 прекращает дальнейшую передачу КК в декодер 19 и вырабатывает сигнал, по которому декодированная безошибочная КК передается на выход устр-ва для использования ее потребителем . Если во всех трех КК декодером 19 обнаружены ошибки, то БУ 21 вырабатывает сигнал об ошибочном приеме. Цель достигается введением дискриминаторов 13 и 14, регистров 15, 16 и 17, коммутатора 18 и БУ 21. Дана ил. выполнения декодера 19иБУ21. 2 ил. с в (Л дых:} Од N9 ts5 4 СО со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (5!)4 Н 04 L 27/22

I

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2 1 ) 402 3804/24-09 (22) 19,02,86 (46) 07.07.87. Бюл. Р 25 (71) Ленинградский электротехнический институт связи им, проф. М. А. БончБруевича (?2) 10, Б, Окунев и Ю. П. Фомин (53) 621. 394 ° 62 (088, 8) (56) Окунев 10. Б, Теория фазоразностной модуляции, — М.: Связь, 1979, с ° 140, (54) УСТРОЙСТВО ДЛЯ ПРИЕМА ДИСКРЕТНЫХ

СООБЩЕНИЙ (57) Изобретение относится к электросвязи, Цель изобретения — повышение помехоустойчивости. Устр-во содержит эл-т задержки !, фазовращатель 2, перемножители 3,4,7 и 8, интеграторы, 5 и 6, блоки задержки 9 и 10, сумматор 11, дискриминаторы 12,13 и 14 полярности, регистры 15,16и 17 сдвига, коммутатор 18, декодер 19, блок синхронизации 20 и блок управления (BY) 21, Последовательности эл-тов передаваемых

„„80„„1322499 А 1 кодовых комбинаций (КК) е выходов . дискриминаторов 12, 13 и 14 на про- тяжении каждой КК заполняют регистры

15, 16 и 17. После приема последнего эл-та КК содержимое регистров 15, 16 и 17 поочередно (в любой последовательности) через коммутатор 18, который управляется БУ 21, передается в декодер 19. Декодер 19 производит обнаружение ошибок в поступающих в него КК и, если ошибки не обнаружены, БУ 21 прекращает дальнейшую передачу КК в декодер 19 и вырабатывает сигнал, по которому декодированная безошибочная KK передается на выход устр-ва для использования ее потребителем, Если во всех трех КК декодером 19 обнаружены ошибки, то БУ 21 вырабатывает сигнал об ошибочном при еме, Цель достигается введением дискриминаторов !3 и !4, регистров 15, 16 и 17, коммутатора 18 и БУ 21. Дана ил. выполнения декодера 19 и БУ 21, 2 ил. Оаэи

1 13

Изобретение относится к электросвязи и может использоваться при приеме дискретных сообщений, закодиро-ванных кодом, позволяющим обнаруживать ошибки, и передаваемых при помощи сигналов с фазоразностной модуляцией второго порядка по каналам с неопределенной и нестабильной несущей частотой.

Цель изобретения — повышение помехоустойчивости.

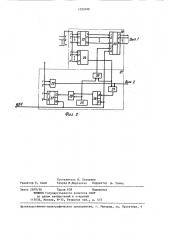

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства; на фиг. 2 — структурная схема декодера и блока управления.

Устройство содержит элемент 1 задержки, фаэовращатель 2, перемножители 3 и 4, интеграторы 5 и 6, перемножители 7 и 8, блоки 9 и 10 задержки, сумматор 11, дискриминаторы

12 — 14 полярности, регистры 15 — 17 сдвига, коммутатор 18, декодер 19, блок 20 синхронизации, блок 21 управления. Декодер 19 состоит из дешифратора 22, регистра 23 сдвига, блока

24.обнаружения ошибок, Блок 21 состоит из задающего генератора 25, RSтриггера 26, счетчика 27, элементов

И 28 — 30, элемента ИЛИ 31, Устройство работает следующим образом.

Совокупность элемента 1 задержки, перемножителя 3 и интегратора 5 образует автокорреляционный демодулятор сигналов с ФРМ первого порядка (ФРМ-1}, в котором отсутствует выходной дискриминатор полярности ° Этот модулятор рассчитан на прием сигналов с частотой, удовлетворяющей соотношению йТ 2k#i, 1с=О,.+ 1, + 2, „... (1) где ш — частота сигнала;

Т - длительность посылки, Аналогично совокупность блока 1 задержки, фазовращателя 2„ перемножителя 4 и интегратора 6 образует автокорреляционный демодулятор сигналов с частотой, удовлетворяющей соотношению

dl (2k+0,5)ii, k=0, + 1, + 2...,, (2)

F, сли выполняются соотношения

ыт (21с+1) Й, 1сйо, Ф 1, + 2 9..., (3} для первой совокупности и

LoT(2k-0,5)и, 1с0,+ 1, + 2...,, (4) 22499 1 для второй, то эти демодуляторы обеспечивают ту же помехоустойчивость инверсных решений. Если принять решения о знаках сигналов на выходах интеграторов 5 и 6 (о знаках косинусов первых разностей фаз) по правилу

О, если соз с1 „Ч> О, I и

1, если cos 4„ (О, (5) !

О где — двоичный символ, соответствующий первой разности фаз д ц на и-й посылке

15 сигнала, и перекодировать их в значения знаков косинусов вторых разностей фаз по правилу И-1 (6}

20 где I„ — двоичный информационный символ, соответствующий второй разности фаз íà и-й посылке сигнала, 25 то можно получать два демодулятора сигналов с ФРМ-2, рассчитанные на работу при выполнении соотношений (7) 4Т-1 П, k&1 + 19 221 °...

30 для первого и (Л=(k+0,5)Т, 1<=0, 1. 1, с 2,..., (8) для второго демодуляторов соответственно, причем их помехоустойчивость будет близка к помехоустойчивости автокорреляционного демодулятора сигналов с ФРМ-1, Легко убедиться, что совокупность перемножителя 7, блока 9 задержки и дискриминатора 13 полярности, а также

40 перемножителя 8, блока 10 задержки и дискриминатора 14 полярности выполняют операции, эквивалентные принятию решения о знаках косинусов первых разностей фаз по правилу (5) и после45 дующего перекодирования их последовательностей в последовательности знаков косинусов вторых разностей фаз по правилу (6). Таким образом, дискретные последовательности на выходах дискриминаторов 13 и 14 полярности при выполнении соотношений (7) и (8) соответственно являются последовательностями элементов передаваемых кодовых комбинаций, Последовательности с выходов всех трех дискриминаторов 12-14 полярно-. сти на протяжении каждой кодовой комбинации заполняют регистры )5 з 13224

17 сдвига, на которые входы которых поступают импульсы тактовой синхронизации, После приема последнего элемента кодовой комбинации содержимое этих регистров поочередно (в лю5 бой последовательности) через коммутатор 18 передается через декодер 19, причем передача каждой комбинации может осуществляться в зависимости от способа реализации декодера по- 1р следовательно (посимвольно).или параллельно (все символы комбинации сразу), Коммутатор 18 управляется сигналом с первого выхода блока 21 управления, запуск которого произ- 15 водится совместно с запуском декодера 19 импульсов блоковой синхронизации. Декодер 19 производит обнаружение ошибок в поступающих в него комбинациях. В этом случае, если в Zp переданной в декодер комбинации ошибки не обнаружены, о чем свидетельствует сигнал на втором выходе декодера, блок 21 управления прекращает дальнейшую передачу комбинаций в деко- 25 дер 19 и вырабатывает на своем втором выходе сигнал, по которому декодированная безошибочная комбинация передается на первый выход устройства для использования ее потребителем. Если во всех трех комбинациях декодером 19 обнаружены ошибки, блок

2l управления на третьем выходе вырабатывает сигнал об ошибочном приеме.

Формула из обретения

Устройство для приема дискретных сообщений, содержащее два канала, каждый из которых состоит из после- 4р довательно соединенных первого пере— множителя, интегратора и второго перемножителя, второй вход которого соединен с выходом интегратора через

99 4 блок задержки, выходы вторых перемножителей соединены с входами сумматора, выход которого соединен с входом

f дискриминатора полярности, первые входы первых перемножителей, вход элемента задержки и вход блока синхронизации объединены и являются входом устройства, причем выход элемента задержки соединен с вторым входом первого перемножителя первого канала и через фазовращатель с вторым входом первого перемножителя второго канала, первый выход блока синхронизации соединен с вторыми входами интеграторов, второй выход блока синхронизации соединен с первым входом декодера, первый выход которого является первым выходом устройства, отличающееся тем, что, с целью повышения помехоустойчивости, введены блок управления, коммутатор, регистр сдвига, а также в каждый канал последовательно соединенные дискриминатор полярности и регистр сдвига, причем выход второго перемножителя в каждом канале соединен с входом дискриминатора полярности, выходы всех регистров сдвига соединены с входами коммутатора, выход которого соединен с вторым входом декодера, третий вход и второй выход которого соединены соответственно с первыми выходом и входом блока управления, вторые вход и выход которого соединены соответственно с вторым выходом блока синхронизации и управляющим входом коммутатора, выход дискриминатора полярности соединен с входом регистра сдвига, первый выход блока синхронизации соединен с управляющими входами всех регистров сдвига, причем третий выход блока управления является вторым выходом устройства.

1322499

Составитель Н. Лазарева

Техред М.Моргентал Корректор h. Тяско

Редактор Е. Папп

Заказ 2879/56 Тираж 638 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4