Генератор псевдослучайных чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике, в частности к устройствам для генерирования произвольных чисел, и .может быть использовано в системах автоматики , например, для управления сменой фиксированного числа значений перестраиваемого параметра системы. Целью изобретения является повышение надежности функционирования генератора. Устройство содержит генератор 1 тактовых импульсов, регистры 2, 9 и 11 памяти, элемент 3 задержки , регистры 4 и 25 сДвига, сумматоры 5 и 26, элементы И 6 и 8, счетчик 7, триггеры 10 и 12, формирователи 13, 19, 20 и 22, элемент И-НЕ 14, элементы ИЛИ 15 и 18, коммутатор 16, элементы НЕ 17, 24, 27 и 28. Поставленная цель достигается за счет введения новых схемных элементов и предложенной схемы функциональных связей между ними. 2 ил. СО Ю . о со «а4, ipufl

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5в 4 H 03 3 84

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4019320/24-2! (22) 10.02.86 (46) 15,07.87. Бюл. № 26 (72) В. А. Молотков, М. Н. Аронштам и 1О. С. Ицкович (53) 621.373 (088.8) (56) Авторское свидетельство СССР № 1239844, кл. Н 03 К 3/84, 1984. (54) ГЕНЕРАТОР ПСЕВДОСЛУЧАИНЫХ

ЧИСЕЛ (57) Изобретение относится к импульсной технике, в частности к устройствам для генерирования произвольных чисел, и»ожет быть использовано в системах автоматики, например, для управления сменой фик„„SU„„1324091 А 1 сированного числа значений перестраивасмого параметра системы. Целью изобретения является повышение надежности функционирования генератора. Устройство c одержит генератор 1 тактовых импульсов, регистры 2, 9 и 11 памяти, элемент 3 задержки, регистры 4 и 25 сдвига, сумматоры 5 и 26, элементы И 6 и 8. счетчик 7, триггеры

10 и 12, формирователи 13, 19, 20 и 22, элемент И-НЕ 14, элементы ИЛИ !5 и !8, коммутатор 16, элементы HE 17, 24, 27 и 28.

Поставленная пель достигается за счет введения HoBblx схемных элементов и предложенной схемы функциональных связей между ними. 2 ил.

1324091

Изобретение относится к импульсной технике, в частности, к устройствам для генерации произвольных чисел, и может быть использовано в системах автоматики, например, для управления сменой фиксированного числа значений перестраиваемого параметра системы.

Цель изобретения — повышение надежности функционирования генератора.

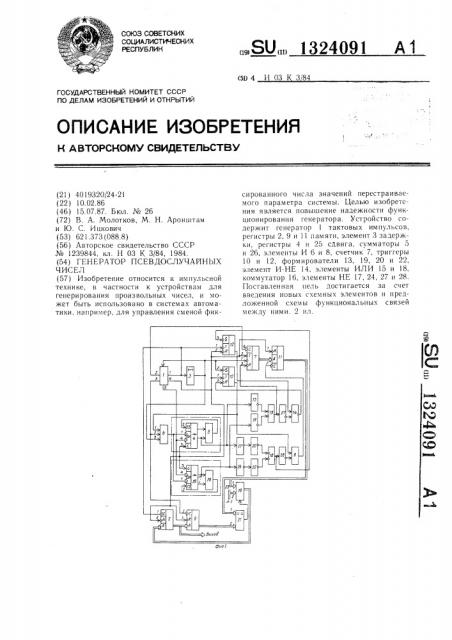

На чертеже представлена структурная схема генератора псевдослучайных чисел; на фиг. 2 — блок-схема генератора тактовых импульсов.

Г енератор псевдослучайных чисел содержит генератор 1 тактовых импульсов, первый регистр 2 памяти, элемент 3 задержки, первый регистр 4 сдвига, первый сумматор 5 по модулю два, первый элемент И 6, счетчик 7, второй элемент И 8, второй регистр 9 памяти, первый триггер 10, третий регистр 11 памяти, второй триггер 12, первый формирователь 13,:элемент И-HF 14, первый элемент ИЛИ 15, коммутатор 16, первый элемент НЕ 17, второй элемент ИЛИ

18, второй 19 и третий 20 формирователи, блок 21 сравнения, четвертый формирователь 22, шину 23 ввода числа п-1, второй элемент НЕ 24, второй регистр 25 сдвига, второй сумматор 26 по модулю два, третий

27 и четвертый 28 элементы HE.

Первый выход генератора 1 тактовых импульсов соединен с первым управляющим входом регистра 2 памяти и входом элемента 3 задержки, выходы разрядов регистров

4 и 25 сдвига в соответствии с коэффициентами генераторного полинома регистра 4 соединены с входами сумматоров 5, 26 по модулю два соответственно, вторые информационные входы регистров 4 и 25 сдвига соединены с выходами сумматоров 5, 26 по модулю два соответственно, выход элемента 3 задержки соединен с первым входом счетчика 7 и входом генератора 1 тактовых импульсов, третий выход генератора 1 тактовых импульсов связан с первым тактовым входом регистров -! и 25 сдвига через элемент И 6, выход первого трипера 10 соединен " первыми входами элементов И 6 и 8, первый вход триггера 12 соединен с первым выходом генератора 1 тактовых импульсов, четвертый выход которого соединен с первым входом триггера 10, с вторым и первым входами (входами установки «0»! регистров 2 и 9 памяти, с вторым входом триггера 12, вторым входом счетчика 7, третьими управляющими входами регистров 4 и 25 сдвига и первым входом регистра 1! памяти, входы группы входов которо о соединены с выходами счетчика

7, пятый выход генератора 1 тактовых импульсов соединен с четвертыми тактовыми входами регистров 4 и 25 сдви-à,,выход элемеппга 3 задержки соединен с третьим

5 !

О !

ЗО

4О

55 входом элемента И 6 и с вторым входом триггера 10, третий вход которого соединен с выходом элемента И-НЕ 14, первый вход которого соединен с выходом триггера 12, выходы последнего разряда регистров 4 и

25 сдвига соединены с входами формирователей 13, 19 соответственно, выходы которых соединены с входами элемента ИЛИ

15, выход которого соединен с третьим входом установки «О» счетчика 7 и входом элемента НЕ 27, выход которого соединен с вторым входом элемента И-НЕ 14, входы формирователей 13 и 19 соединены с входами элементов НЕ 7 и 24 соответственно, выходы которых связаны через формирователи 20 и 22 с входами элемента ИЛИ 18, выход которого соединен с третьим входом установки «1» тригге,)a 12 и входом элемента HE 28, выход которого соединен с вторым входом элемента И 8, выход которого соединен с вторым управляющим входом регистра 11 памяти, четвертый счетный вход счетчика 7 соединен с вторым выходом генератора 1 тактовых импульсов, выход регистра 11 памяти соединен с первыми входами коммутатора 16 и блока 21 сравнения, второй вход которого соединен с выходом регистра 9 памяти, второй управлякнций вход которого соединен с третьим выходом генератора 1 тактовых импульсов, выход блока 21 сравнения соединен с управляющим входом . коммутатора !6, второй вход коммутатора 16 соединен с группой входов регистра 2 памяти, выход которого соединен с группой входов регистра 9 памяти и является выходом устройств:=!.

Генератор 1 тактовых импульсов (фиг. 2) состоит из последовательно соединенных генератора 29 импульсов, первого делителя 30 частоты, формирователя 31, элемента

32 задержки, элемента НЕ 33, второго делителя 34 частоты, счет ика 35, дешифратора

36, выходы которого через переключатель

37 соединены с первым входом элемента

И-HE 38, второй вход которого подключен к выходу формирователя 31, выход генератора 29 импульсов соединен с вторым входом формирователя 31. Для формирования сигналов начальной установки используется цепь, состоящая из последовательно включенных триггера 39, элемента ИЛИ 40 и элемента ИЛИ 41, второй вход элемента

ИЛИ 40 обьединен с входом установки

«1» триггера 39, который соединен через резистор 42 с шиной 43 питания, а через коммутационный элемент 44 — с обгцей шиной 45 питания, вход установки «О» три гера 39 подключен к выходу RC-цепи 46, подключенной между шинами 43 и 44 питания.

Выход элемента ИЛИ 4! соединен с вхо;f,HMH сброса делителей 30 и 34 частоты и счетчика 35, выход элемеипга И-HE 38 яв1324091

10

55 ляется первым выходом генератора 1 тактовых импульсов, вторым, третьим четвертым и пятым выходами которого являются соответственно выход формирователя 31, выход элемента 32 задержки, выход элемента ИЛИ 40 и выход генератора 29 импульсов, второй вход элемента ИЛИ 41 является входом генератора 1 тактовых импульсов. Генератор 29 импульсов обеспечивает формирование импульсов со скважностью два. Он выполнен в виде кварцевого генератора, собранного по схеме емкостной трехточки и усилителя, обеспечивающего усиление сигнала по мощности и стандартизацию уровня. Установка в «О» производится сигналом низкого уровня.

Устройство работает следующим образом.

При появлении сигнала низкого уровня на четвертом выходе генератора 1 тактовых импульсов, что имеет место при включении напряжения питания или в момент пуска генератора, осуществляемого с помощью коммутационного элемента, устанавливаются в начальное нулевое состояние регистры 2, 9, 11 памяти, триггеры 10, 12 и производится сброс счетчика 7. Выходным сигналом низкого уровня с выхода триггера

10 блокируется прохождение тактовых импульсов через элемент И 6.

Регистры 4 и 25 сдвига в момент появления установочного сигнала низкого уровня на их входах приводятся в исходное положение в режиме параллельной записи, при котором в регистры 4, 25 сдвига записывают исходное число, постоянно заведенное на входы параллельной записи, запрещенным является только одно состояние регистра 4 и 25 сдвига — 00...0. В момент поступления циклового импульса с первого выхода генератора 1 на управляющий вход регистра 2 памяти в последний заносится код с выхода коммутатора 16.

При поступлении первого с момента пуска генератора циклового импульса (через время, равное Т>, после окончания сигнала начальной установки) вследствие равенства кодовых слов (все нули) на обоих входах блока 21 сравнения на выходе генератора формируется число, равное и-1. Необходимое условие постоянства сигнала на информационном входе регистра 2 памяти в течение необходимого времени после переднего фронта циклового импульса обеспечивается за счет задержки информации в регистре 9 памяти, так как изменение сигнала на выходе регистра 9 происходит по переднему фронту синхроим пульса, поступаюгцего с третьего выхода генератора

1 тактовых импульсов. Цикловый импульс поступает также на вход установки «О» триггера 12 и устанавливает последний в нулевое состояние. Задержанным цикловым импульсом. снимаемым с элемента 3 задержки, осуществляется сброс счетчика

7, установка триггера 10 в единичное состояние, при котором последний выдает сигнал, разрешающий прохождение тактовых импульсов с третьего выхода генератора 1 тактовых импульсов через элемент И 6 и возврат в исходное состояние цепи формирования цикловых им пульсов генератора

1 тактовых импульсов.

Для повышения надежности формирование числовой последовательности в регистре 11 памяти осуществляется с помощью двух идентичных синхронно работающих независимых формирователей М-последовательности, каждый из которых состоит из регистра 4 (25) сдвига с сумматором 5 (26) по модулю два в цепи обратной связи.

С приходом тактового импульса содержимое регистра 4 (25) сдвига сдвигается на один разряд вправо, а в освободившуюся ячейку записывается сигнал с выхода сумматора 5 (26) по модулю два. На выходе последнего разряда регистров 4 (25) сдвига формируются одинаковые псевдослучайные двоичные последовательности — М вЂ” последовательности.

С момента окончания импульса сброса на первом входе счетчика ? в нем фиксируются импульсы с второго выхода генератора 1 тактовых импульсов.

Для исключения прохождения сдвига в регистрах 4 и 25 сдвига в такте, соответствующем появлении ци клового им пульса, сигналом низкого уровня, снимаемым с выхода элемента 3 задержки, осуществляется блокировка элемента И 6, при этом величина задержки сигнала в элементе 3 задержки, определяющая момент установки триггера 10 в единичное состояние, должна несколько превышать величину задержки сигнала на третьем выходе генератора тактовых импульсов относительно сигнала на его втором выходе.

Как только в составе М-последовательности появляется «О», положительным иерепадом с выходов элементов НЕ !7, 24 запускаются формирователи 20 и 22, на BbIxoдах которых появляются отрицательные им пульсы, которые объединяются с пом ощью элемента ИЛИ 18, выходной сигнал которого через элемент НЕ 28 поступает на второй вход элемента И 8, управляемого по первому входу выходным сигналом триггера 10. При этом с выхода элемента И 8 на управляющий вход регистра 11 памяти поступает импульс заllиси, фиксирующий содержимое счетчика 7, накопленное в нем за время, пока в формируемом отрезке

М-последовательности проходит серия «1» (т.е. пока на выходе последнего разряда

1324091

20 регистра 4, 25 сдвига сохраняется высокий уровень сигнала).

При отсутствии неисправностей в формирователях М-последовательности сигналы на выходах регистров 4 и 25 сдвига совпадают, при этом импульсы на выходе формирователей 20, 22 появляются одновременно. В момент перехода в формируемой М-последовательности от «О» к «1» запускаются формирователи 13 и 19, выходные сигналы которых объединяются с помощью элемента ИЛИ 15, выходной сигнал которого через элемент HE 27 поступает на второй вход элемента И-НЕ 14, управляемого по первому входу выходным сигналом триггера

12, Если триггер 12 находится в единичном состоя нии, то выходным сигналом низкого уровня элемента И-HE 14 триггер 10 устанавливается в «О», при этом прекращается сдвиг в регистрах 4 и 25 сдвига, которые фиксируются в состоянии, соответствующем высокому уровню сигнала на выходе их последних разрядов.

В регистре 11 памяти оказывается сформированным псевдослучайное число, соответствующее количеству единичных сигналов в генерируемом за цикл работы устройства отрезке М-последовательности. Для исключения повторения смежных чисел на выходе устройства в блоке 21 производится сравнение кода на выходе регистра ll памяти с кодом в регистре 9. В случае их равенства на выходе блока 21 сравнения формируется сигнал низкого уровня, и коммутатор 16 переключается таким образом, что на информационный вход регистра 2 памяти поступает код с шины 23 числа и-1 (число, равное п-l, отсутствует на выходе регистра ll памяти). В противном случае на выход коммутатора 16 поступает код с выхода регистра 11 памяти.

В начале следующего цикла работы генератора псевдослучайных чисел в момент поступления циклового импульса с первого выхода генератора 1 тактовых импульсов осуществляется перезапись кода с выхода коммутатора 16 в регистр 2 памяти и установка в «О» триггера 12. Затем осуществляется сброс счетчика 7, установка триггера

10 в единичное состояние и происходит формирование очередного псевдослучайного числа в регистре 11 памяти. Описанный цикл работы генератора повторяется при формировании каждого нового числа.

Появление неиспра вности в одном из регистров 4, 25 сдвига приводит к тому, что один или несколько триггеров этого регистра постоянно находятся в одних и тех же (нулевых или единичных) состояниях.

Последовательно сдвигаясь, это состояние (не позже, чем через и тактов) проявляет себя на выходе последнего разряда

55 регистра сдвига, после чего уровень сигнала на выходе последнего разряда регистра сдвига перестанет изменяться. До этого момента последовательность двоичных символов на выходе последнего разряда неисправного регистра сдвига не имеет искажений. Если в очередном цикле прохождения сдвига до момента появления расхождения М-последовательностей на выходах последних разрядов регистров 4, 25 сдвига был высокий уровень сигнала, то на втором входе регистра 11 памяти возможно появ ление двух импульсов записи, при этом если на выходе исправного регистра переход из «1» в «О» происходит позже, чем в неисправном регистре, то в регистре 11 памяти зафиксируется недостоверное число, однако в одном из последующих тактов в данном цикле работы устройства поступает второй импульс, связанный с изменением значения сигнала на выходе исправного канала формирования М-последовательности. В противном случае к моменту поступления импульса на второй вход регистра 11 памяти, связанного с изменением сигнала в исправном канале формирования, на выходе неисправного регистра сдвига уровень сигнала перестает изменяться, что исклк>чает дальнейшую смену информации в регистре 11 памяти в данном цикле работы устройства. При этом в последующих циклах работы устройства на втором входе регистра 11 памяти в каждом цикле будет формироваться только один импульс записи, связанный с соответствующим изменением сигнала на выходе последнего разряда исправного регистра сдвига.

При появлении неисправности в последнем разряде одного из регистров 4, 25 сдвига в паузе между поступлениями циклового импульса элемент И 8 блокирует выходной сигнал элемента НЕ 28 (за счет поступления сигнала нйзкого уровня с выхода триггера 10), препятствуя таким образом смене информации в регистре 11 памяти.

Если в очередном цикле прохождения сдвига до момента появления расхождения

М-последовательностей на выходах последних разрядов регистров 4, 25 сдвига был низкий уровень сигнала, то в регистре 11 памяти фиксируется достоверное число. Однако в этом случае сдвиг в регистрах 4, 25 может прекратиться в момент, когда исправный регистр сдвига находится в состоянии, соответствующем низкому уровню сигнала на выходе его последнего разряда (если в неисправном регистре установится высокий уровень сигнала). Для обеспечения в этом случае формирования достоверных чисел в последующих циклах работы генератора прекращение сдвига в регистрах 4, 25 сдвига производится только после появления сигнала на выходе элемента ИЛИ

1324091

25

Формула изобретения

18, для чего его выходной сигнал поступает на вход установки «1» триггера 12, выходной сигнал высокого уровня которого обеспечивает разрешение работы элемента И-HE

14. Установка в нулевое состояние триггера

12 производится в начале каждого цикла работы устройства сигналом низкого уровня с первого выхода генератора 1 тактовых им пульсов.

С этой же целью выходным сигналом первого элемента ИЛИ 15 сбрасывается содержимое счетчика 7, накопленное при низком уровне сигнала на выходе исправного регистра сдвига.

Минимально допустимая величина временного интервала смены кода на выходе данного генератора Тч. мн определяется максимальной величиной формируемого за один цикл отрезка М-последовательности и составляет

Т„. = (и+ (п — 1) + (и — 2) )< = (Зп — 3), где — период повторения TBKToBbIx HMпульсов; и — максимальная значность серии единичных символов М-последовательности;

6-1, и-2 — максимальные значности серий нулевых символов М-последовательности.

Генератор 1 тактовых импульсов работает следующим образом.

При подключении напряжения питания триггер 39 с помошью RC-цепи 46 устанавливается в «О» за время заряда конденсатора С через резистор R. Выходным сигналом элемента ИЛИ 40 через элемент ИЛИ 41 осуществляется сброс делителей 30 и 34 частоты и счетчика 35. Сигнал с выхода элемента ИЛИ 40 поступает также на четвертый выход (начальной установки) генератора 1 тактовых импульсов.

Пуск генератора псевдослучайных чисел осуществляется с помощью коммутационного элемента 44, выходным сигналом которого устанавливается в единичное состояние триггер 39, а также осуществляется через элементы ИЛИ 40 и 41 сброс делителей 30 и 34 частоты и счетчика 35.

С помощью резистора 42 осуществляется привязка входа установки в «1» триггера 39 к уровню «1».

Цепь, состоящая из элемента HE 33, второго делителя 34 частоты, счетчика 35, дешифратора 36, переключателя 37 и элемента И-HE 38 обеспечивает формирование цикловых им пульсов с периодом Т>, которые по длительности и фазе совпадают с соответствующим и тактовыми импульсам и на втором выходе генератора тактовых импульсов. Элемент НЕ 33 формирует на своем выходе отрицательные импульсы. Делитель 34 частоты обеспечивает необходимую цепь импульсов, поступаюших на счетный вход счетчика 35. После окончания OI гнала сброса счетчик 35 начиняет по.Ic«e T импульсов, поступающих на его счстнь,й вход.

По истечении интервала времени, равноIo заданному цикловому интервалу T, »a соответствуюгцем выходе дешифратора 36 появляется сигнал единичного уровня. Опрос дешифратора 36 производится с помо цью элемента И-НЕ 38, на второй вход которого подаются тактовые импульсы с выхода формирователя 31. На первом выходе генератора 1 тактовых импульсов формируется цикловой импульс. После сформирования циклового импульса происходит сброс счетчика 35 и делителей 30, 34 частоты сигналом, поступающим на вход генератора 1 тактовых импульсов, имеющим задержку относительно импульса на первом выходе генератора 1, а затем начинается отсчет очередного временного интервала, равHOI0 T

Величина интервала Т„выбирается с помощью переключателя 37, устанавливаемого в определенное положение до момента пуска генератора псевдослучайных чисел.

Генератор псевдослучайных чисел, сoдержащий генератор тактовых импульсов, первый выход которого соединен с первым входом первого регистра памяти и входом элемента задержки, выход которого соединен с первым входом счетчика, первый элемент И, выход которого соединен с первым входом первого регистра сдвига, соответствующие выходы которого соединены с входами первого сумматора по модулю два, выход которого соединен с вторым входом первого регистра сдвига, второй элемент И, первый вход которого соединен с выходом первого триггера и с первым входом первого элемента И, второй вход которого соединен с третьим выходом генератора тактовых импульсов, второй триггер, выход которого соединен с первым входом элемента И-НЕ, первый вход второго триггера соединен с первым выходом генератора тактовых импульсов, четвертый выход которого соединен с первым входом первого триггера, вторым входом счетчика, третьим входом первого регистра сдвига, вторым входом первого регистра памяти, первым входом второго регистра памяти, вторым входом второго триггера, пятый выход генератора тактовых импульсов соединен с четвертым входом первого регистра сдвига, выход элемента задержки соединен с входом генератора тактовых импульсов, третьим входом первого элемента И и вторым входом первого триггера, коммутатор, выходы которого соединены с соответствующи1324091

1 о - 1

L фее 2

Составитель В. Чижов

Редактор М. Товтии Техрсд И Верее Корректор И. Эрдейи

3 и к а 3 2971!55 Тираж 901 Подписное

ВИИИПИ осударственного комитета СССР ио делам изобретений и открытий ! 1З035, Москва, !K — 35, Раушская наб., 1. 4/5

Производ."твс нво-иолиграфичсгкое вред:риятие, г. Ужгород, ул. Проектная, 4 ми входамп I руппы входов первого регистра памяти, блок сравнения, первая группа входов которого соединена с первой группой входов коммутатора, вторая группа входов которого соединена с шиной ввода числа, выход блока сравнения соединен с входом коммутатора, выходы второго регистра памяти соединены с второй группой входов блока сравнения, второй вход второго регистра памяти соединен с третьим выходом генератора тактовых импульсов, выходы первого регистра памяти соединены с группой входов второго регистра памяти, первый формирователь, первый и второй элементы ИЛИ, отличающийся тем, что, с целью повышения надежности, он содержит второй регистр сдвига, второй сумматор по модулю два, "ðåòèé регистр памяти, второй, третий и четвертый формирователи, первый, второй, третий и четвертый элементы НЕ, выходы счетчика соединены с соответствующими входами группы входов третьего регистра памяти, первый вход которого соединен с четвертым выходом генератора тактовых импульсов, второй вход третьего регистра памяти соединен с выходом второго элемента И, первый вход первого регистра сдвига соединен с первым входом второго регистра сдвига, соответствующие выходы которого соединены с входами второго сумматора по модулю два, выход которого соединен с вторым входом второго регистра сдвига, третий и четвертый входы которого соединены соответственно с третьим и четвертым входами первого регистра сдвига. выходы последнего разряда первого и второго регистров сдвига соединены соответственно с входами первого и второго элементов НЕ и с входами первого и второго формирователей, выходы которых соединены с входами первого элемента ИЛИ, выход которого соединен с третьим входом счетчика и входом третьего элемента НЕ, выход которого соединен с вторым входом элемента И-HF., выход которого соединен с третьим входом первого триггера, выходы первого и второго элементов НЕ соединены соответственно с входами третьего и четвертого формирователей, выходы которых соединены с входами второго элемента ИЛИ, выход которого соединен с третьим входом второго триггера и входом четвертого элемента НЕ, выход которого соединен с вторым входом второго элемента И, четвертый вход счетчика соединен с вторым выходом генератора тактовых импульсов, выходы третьего регистра памяти соединены с первой группой входов коммутатора.