Устройство для преобразования двоичной последовательности в блочный балансный троичный код

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Его использование в системах передачи цифровой информации , например, для контроля этих систем позволяет расширить область применения за счет обеспечения возможности работы в широком диапазоне частот . Устройство содержит преобразователь 1 последовательного кода в параллельный , переключатель 2 двоичных символов, кодирующую матрицу 3, переключатель 4 троичных символов, преобразователь 5 параллельного кода в последовательный и Аоомиоователь 6 балансного кода. Введение генератора 7 тактовой частоты, делителей 8, 9 частоты и элемента И 10 позволяет устройству работать с любой требуемой частотой. 2 ил., 1 табл. CpU2.f

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (11 4 Н 03 M 5/18 а .

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCMOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4015104/24-24 (22) 10.01.86 (46) 15.07.87. Бюл. И- 26 (72) В.А.Жаворонков и А.В.Пономаренко (53) 681 . 32 (088. 8) (56) Авторское свидетельство СССР

¹ 902294, кл. Н 03 М 5/18, 1980.

Патент Великобритании № 1481008, кл. Н 04 L 25/06, 1977. (54) УСТРОЙСТВО ДПЯ ПРЕОБРАЗОВАНИЯ

ДВОИЧНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ В БЛОЧНЫЙ БАЛАНСНЫЙ ТРОИЧНЫЙ КОД (57) Изобретение относится к вычислительной технике. его использование в системах передачи цифровой информа„„SU„„1324115 А 1 ции, например, для контроля этих систем позволяет расширить область применения за счет обеспечения возможности работы в широком диапазоне частот. Устройство содержит преобразователь 1 последовательного кода в параллельный, переключатель 2 двоичных символов, кодирующую матрицу 3, переключатель 4.троичных символов, преобразователь 5 параллельного кода в последовательный и йоомипователь 6 балансного кода. Введение генератора 7 тактовой частоты, делителей 8, 9 частоты и элемента И 10 позволяет устройству работать с любой требуемой частотой. 2 ил., 1 табл.

13241

Изобретение относится к вычислительной технике и может быть использовано в системах передачи цифровой информации, например, для контроля этих систем. 5

Цель изобретения — расширение области применения за счет обеспечения возможности работы в широком диапазоне частот.

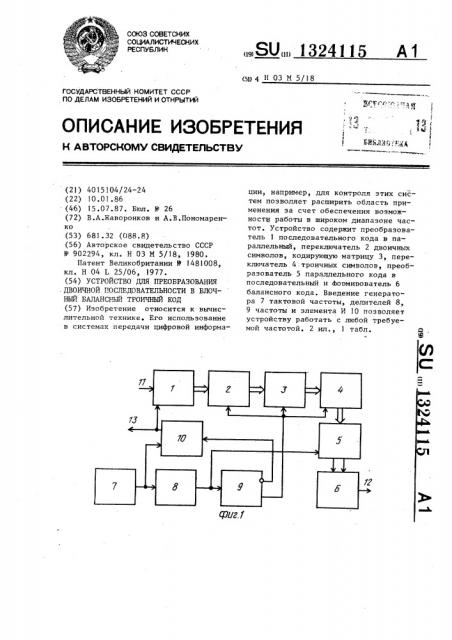

На фиг.1 приведена функциональная 10 схема устройства; на фиг,2 — временные диаграммы его работы.

Устройство содержит преобразователь 1 последовательного кода в параллельный, переключатель 2 двоичных 15 символов, кодирующую матрицу 3, переключатель 4 троичных символов, преобразователь 5 параллельного кода в последовательный, формирователь 6 балансного кода, генератор 7 тактовой 20 частоты, первыи 8 и второй 9 делители частоты и элемент И 10. На фиг.1 обозначены вход 11, информационный 12 и тактовый 13 выходы.

Преобразователь 1 выполнен на ре- гистре сдвига, переключатели 2 и 4 регистры-защелки. Кодирующая матрица может быть реализована на ПЗУ, преобразователь 5 — на мультиплексоре с управляющим счетчиком. В качестве 30 формирователя 6 может быть использован операционный усилитель.

Генератор 7 формирует сигнал, частота которого вдвое выше частоты поступления разрядов входного кода. 35

Первый делитель 8 осуществляет деле-! ние этой частоты на два а второй деt литель 9 делит полученную частоту на три.

Сигнал с выхода элемента И 10 по- 40 ступает на выход 13 для управления ввоДом сигнала на вход 11. В частности, сигнал с выхода 13 может тактировать работу генератора псевдослучайной последовательности (ПСП) при использовании рассматриваемого устройства для контроля системы передачи.

Работу устройства для преобразо"

I вания двоичной последовательности в блочный балансный троичный код рассмотрим применительно к формированию блочного балансного троичного кода

F0NOT, являющегося разновидностью блочного балансного троичного кода 4В . 3T. При этом четырехбитным бинарным блокам ставятся в соответствие блоки

I из трех троичных символов, принимающих значение (+); (-); (О). Вид тро15 2 ичного блока может меняться в зависимости от значения текущей цифровой суммы в конце предыдущего блока. Тран. слятор кодирования занесен в кодирующую матрицу 3.

Транслятор кода FOMOT приведен в таблице.

Как видно из таблицы, основной сложностью при преобразовании является синхронное формирование четырех битов двоичной последовательности за три тактовых интервала троичного сигнала. Задача решается применением генератора 7 с удвоенной тактовой частотой, формирующего за три такта троичного сигнала шесть импульсов сдвига (фиг.2,а) I Дпя исключения двух лишних импульсов сдвига используется элемент И 10 и делители 8 и 9 частоты, формирующие остановку входной последовательности на два тактовых интервала (фиг.2 б, г, д).

В результате сигнал на вход 11 подается на удвоенной частоте сдвига с остановками на два тактовых интервала (фиг,2,е), т.е. четыре бита двоичной последовательности на каждые три такта троичного сигнала.

С входа 11 последовательный бинарный код поступает на преобразователь 1 последовательного кода в параллельный.

Четырехбитные блоки (фиг.2,ж ) фиксируются на переключателе 2 двоичных символов импульсами блочной синхронизации с прямого выхода делителя 9 (фиг.2,в) в интервалах остановок входного сигнала. Время фиксации— три тактовых интервала троичного сигнала. Эти бинарные блоки (фиг.2, и) поступают на вход кодирующей матрицы 3, в которой записан алгоритм преобразования, задаваемый таблицей.

Получающиеся на выходе кодирующей матрицы 3 параллельные троичные блоки (фиг.2,к) стробируются в переключателе 4 троичных символов импульсами блочной синхронизации для устранения влияния времени задержки преобразования в кодирующей матрице 3, параллельные троичные блоки (фиг.2,л) поступают на вход преобразователя 5 параллельного кода в последовательный, и с его выходов (фиг.2, м,н) импульсы отрицательной и положительной полярности поступают на входы формирователя 6, на выходе которого и формируются смешанные импульсы троично1324

Троичные .блоки

Сумма 2

Бинарный блок

Сумма 1

Сумма 3 Сумма 4

-00

"00

-+ 0

-+О

-+ 0

-+ 0

+-О

+-0

+-0

+ — О

+00

+00

-О+

-О+

-О+ — О—

-О+0+

+0+

+О+0+О+0--О

--О

О++

О++

О+ 0

0-0

0-0

0+0

+ — +

ro кода необходимой амплитуды, подаваемые на выход 12 (фиг.2,п).

Таким образом, устройство способно работать на любой частоте заданно- 5 го диапазона.

Формула изобретения

Устройство для преобразования дво-1О ичной последовательности в блочный балансный троичный код, содержащее преобразователь последовательного кода в параллельный, информационный вход которого является входом устрой-t5 ства, выходы соединены с информационными входами переключателя двоичных символов, выходы которого подключены к информационным входам кодирующей матрицы, выходы кодирующей матрицы 20 соединены с информационными входами переключателя троичных символов, выходы которого подключены к информационным входам преобразователя параллельного кода в последовательный, вы. 25 ходы которого соединены с входамн формирователя балансного кода, выход

00 10

0011

О 100

0101

О l 1 О.

О 1 1 I

l 000

1001

1010

115 4 которого является информационным вы= ходом устройства, тактовые входы переключателей двоичных и троичных символов объединены, о т л и ч а ющ е е с я тем, что, с целью расширения области применения устройства за счет обеспечения возможности работы в широком диапазоне частот, в устрой" ство введены делители частоты, элемент И и генератор тактовой частоты, выход которого соединен с первым входом элемента И и входом первого делителя частоты, выход которого подключен к тактовому входу преобразовате" ля параллельного коде в последовательный и входу второго делителя частоты, прямой выход которого соединен с объединенными тактовыми входами переключателей двоичных и троичных символов и тактовым входом кодирующей матрицы, инверсный выход второго делителя частоты соединен с вторым входом элемента И, выход которого под-. ключен к тактовому входу преобразователя последовательного кода в параллельный и является тактовым выходом устройства.

I 324115

Продолжение таблицы

Трончные блоки

Викарии блок

Сумма

Сумма 2 Сумма 3 а 4

0-0-++о

++0

00+

00+

--0

0 +

О+О+О+0-+

0 -+

0-+

00Оолджьи им лм.

t о ж - ю ю л - ааГ юЭ

i дрок

Редактор Л.Веселовская

Заказ 2973/57

Тираж 901 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, И-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

1О11

»00

»01

1 1 1 1

Составитель О.Ревинский

Техред Л. Олейник Корректор Н.Король