Устройство для деления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных вычислительных машипах и системах. Целью изобретения является увеличение быстродействия работы устройства. Это достигается тем, что устройство для деления, содержащее регистры делителя 2, остатка 1 и частного 12, блок 3 памяти, умножитель 4, сумматор-вычитатель 6, вычитающий счетчик 5, блок 11 микропрограммного управления, счетчик циклов 10 и функциональные связи, дополнительно снабжено группой 7 элементов И, группой 8 элементов И-НЕ, группой 9 элементов ИЛИ и дополнительными функциональными связими, это позволяет реализовать алгоритм деления без восстановления остатка, в каждом цикле которого определяются одновременно р разрядов частного (р 2,3,...,п-3; п - разрядность операндов), и обеспечивает увеличение быстродействия устройства на 15% при р 4, п 32, 3 ил. 00 to СП 4 05

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (su 4 G 06 F 7/52

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY СВИДЕТЕРЬСТВУ

;у 3 (21) 4039839/24-24 (22) 19.03.86 (46) 23.07.87. Бюл. № 27 (72) А. И. Бобровский и Г. Н. Булкин (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 1104508, кл. G 06 F 7/52, 1982.

Авторское свидетельство СССР № 1283752, кл. G 06 F 7/52, 10.06.85. (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ (57) Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных вычислительных машинах и системах. Целью изобретения является увеличение быстродействия работы устройства. Это достигается тем, что устрой„„Я0„„1325467 А 1 ство для деления, содержащее регистры делителя 2, остатка 1 и частного 12, блок 3 памяти, умножитель 4, сумматор-вычитатель

6, вычитающий счетчик 5, блок 1 микропрограммного управления, счетчик циклов !О и функциональные связи, дополнительно снабжено группой 7 элементов И, группой 8 элементов И вЂ” НЕ, группой 9 элементов ИЛИ и дополнительными функциональными связями, это позволяет реализовать алгоритм деления без восстановления остатка, в каждом цикле которого определяются одновр»менно р разрядов частного (p =- 2,3,...,n — 3; и — разрядность операндов), и обеспечивает увеличение быстродействия устройства на

15% при р= 4, и= 32, 3 ил.

1325467

45

Изобретение относится к цифровой вычислительной технике, предназначно для деления чисел, представленных в двоичной системе счисления, и может найти применение в качестве операционного блока в высокопроизводительных вычислительных машинах и системах.

Цель изобретения — повышение быстродействия устройства для деления.

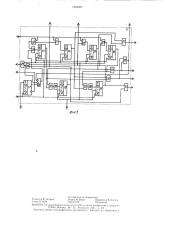

На фиг. 1 приведена функционаьная схема устройства для деления; на фиг. 2— граф переходов состояний и выходов блока микропрограммного управления; на фиг. 3— схема блока микропрограммного управления на основе D-триггеров с асинхронными

S- u R-входами с перемещаемой единицей.

Устройство для деления (фиг. 1) содержит регистр 1 остатка, регистр 2 делителя, блок 3 памяти, умножитель 4, вычитающий счетчик 5, сумматор-вычитатель 6, группу 7 элементов И, группу 8 элементов И вЂ” HE, группу 9 элементов ИЛИ, счетчик 10 цик лов, блок 11 микропрограммного управления, регистр 12 частного. Блок 11 (фиг. 3) содержит D-триггеры 13 — 19, элементы И 20- — 25, элементы ИЛИ 26 — 34, элементы 35 и 36 задержки. В блоке 3 хранятся р-разрядные коды предварительных значений очередных р разрядов частного Прошивка блока 3 сделана с учетом того, что старший разряд регистра 2 равен 1 и (р+1)-разрядный второй адресный вход блока 3 соединен со старшими разрядами регистра 2, начиная с второго старшего разряда, исключая первый, Блок 11 предназначен для организации процесса деления, который состоит из повторяющихся однотипных циклов. В каждом цикле определяются значения очередных р разрядов частного. Для этого блок 11 формирует последовательность управляющих си налов на своих выходах. На графе (фиг. 2) переходов состояний и выходов блок 11 управления Ao...Ae — состояния, на дугах указаны условия переходов, над стрелками названия выходных сигналов, формируемых при переходе в соответствующее состояние.

Устройство работает следующим образом.

В исходном состоянии Ао в регистре находится делимое, в регистре 2 — - делитель, счетчик 10 находится в начальном состоянии (обнулен или сигналом «Сброс» в него записан код дополнения).

По сигналу «Пуск», означающему начало операции деления, блок 11 переходит из состояния An в состояние Ai. При этом по значениям соответствующих старших разрядов делителя и модуля очередного (для первого цикла — исходного) делимого, поступающих из регистров 2 и 1 на соответствующие адресные входы блока 3 памяти, выбираетя код, являющийся предварительным значением очередных разрядов частного.

На выходе умножителя 4 формируется произведение выбранного кода на делитель.

Затем блок 11 переходит из состояния Ai в состояние А . При этом содержимое счетчика 10 увеличивается на единицу, а на сумматоре-вычитателе 6 вычисляется разность очередного делимого и произведения, полученного на умножителе 4. Полученный таким образом остаток записывается со сдвигом на р разрядов в сторону старших разрядов в регистр 1. В результате на регистре

1 оказывается сформированным новое очеред ное делимое. На счетчик 5 записывается код, выбранный из блока 3 памяти.

В дальнейшем в работе устройства имеется совмещение во времени операций по определению значений двух групп (по р разрядов в каждой) разрядов частного.

Блок 11 в зависимости от знака очередного остатка, полученного на сумматоревычитателе 6, переходит в состояние Аз (остаток отрицательный) или в состояние Ai (в противном случае). Но независимо от этого при переходе в состояния Ai и Ао формируется произведение, как описано для перехода Ao Ai, делителя на код, выбранный из блока 3 памяти по соответствующим значениям cTBpnlnx разрядов модуля нового очередного делимого и делителя.

Если произошел переход А An, то для получения истинных значений очередных разрядов частного уменьшается содержимое счетчика 5 на единицу младшего разряда, и полученный код со счетчика 5 записывается в младшие р разрядов регистра 12.

Если произошел переход А — э-А;. то код, хранящийся на счетчике 5, записывается в младшие р разрядов регистра 12. После этого блок 11 переходит из состояния Ai в состояние А, при этом в регистре 12 производится сдвиг на р разрядов в сторону старших разрядов.

Из состояния Ад в состояние А блок 11 переходит, как описано для перехода А А .

Отличие заключается в том, что вместо разности на сумматоре-вычитателе 6 вычисляется сумма нового произведения и нового очередного делимого. Г!олученный таким образом очередной остаток записывается со сдвигом на р разрядов в сторону старших разрядов в регистр 1.

Из состояния А блок 11 в зависимости от знака очередного остатка переходит в состояние А,-, или An аналогично переходам

А+ «An, i A> Ai. Or inчие заключается только в формировании истинных значений очередных р разрядов частного. Поскольку очередное делимое отрицательное (переход в состояние А ), то истинные значения очередных разрядов частного получаются взятием дополнения от коl3, хранящегося на счетчике 5 (состояние А;), либо взятием дополнения от кода, увеличенного на единицу младшего разряда (состояние А ). Поэтому при переходе A.i- - А,-, код на счетчике 5 умень шается на единицу и инвертируется, после чег0 записывается в младшие р разрядов

1325467

Формула изобретения

ПР регистра 12.При переходе А4 А6 код счетчика 5 просто инвертируется (— 1+1 = 0) и записывается в младшие 1з разрядов регистра 12.

В дальнейшем процесс деления происходит аналогично и заканчивается при появлении сигнала «Стоп» из счетчика 10, по которому блок 11 переходит в состояние Ао и формирует сигнал «Сброс», устанавливающий счетчик в начальное состояние.

Устройство для деления, содержащее регистры делителя, частного и остатка, умножитель, блок памяти, счетчик циклов, сумматор-вычитатель, вычитающий счетчик, блок микропрограммного управления, причем выходы старших (р+2) разрядов регистра остатка (где р = 2,3,....n — 3; n — разрядность операндов) соединен с первым адресным входом блока памяти, второй адресный вход которого соединен с выходом (р+

-+1) старших разрядов регистра делителя, выход которого соединен с входом первого сомножителя умножителя, вход второго сомножителя которого соединен с выходом блока памяти и с информационным входом вычитающего счетчика, выход сумматора-вычитателя соединен с информационным входом регистра остатка, выход которого соединен с первым информационным входом сумматоравычитателя, выход знакового разряда которого соединен с входом-анализа знака остатка блока микропрограммного управления, первый выход которого соединен с входом сброса счетчика циклов, выход переноса которого соединен с входом останова блока микропрограммного управления, второй выход которого соединен со счетным входом счетчика циклов, третий выход блока микро5 программного управления соединен с входом разрешения вычитания сумматора-вычитателя, вход разрешения сложения которого соединен с четвертым выходом блока микропрограммного управления, вход запуска которого является входом пуска устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены группа элементов И, группа элементов И вЂ” НЕ, группа элементов ИЛИ, причем выход умножителя соединен с вторым информационным входом сумматора-вычитателя, пятый выход блока микропрограммного управления соединен с входом разрешения умножения умножителя и с входом разрешения записи регистра частного, вход разрешения сдвига которого соединен с входом разрешения записи вычитающего счетчика и с шестым выходом блока микропрограммного управления, седьмой выход которого соединен с входом заема вычитающего счетчика, выходы разрядов которого соединены с первы25 ми входами элементов И группы и элементов И вЂ” НЕ группы, вторые входы которых соединены с восьмым выходом блока микропрограммного управления, девятый выход которого соединен с вторыми входами элементов И группы, выходы которых соединены с первыми входами элементов ИЛИ группы, вторые входы которых соединены с выходами элементов И вЂ” HE группы, выходы элементов ИЛИ группы соединены с информационными входами разрядов регистра частного.

1325467

Составитель Н. Маркелова

Редактор В. ГIстраш Текред И. Верее Корректор В. Ьу ига

Заказ 3 !! О/44 Тираж 672 Подписное

В1з ИИПИ Государственного комитета СССР по делам изобретений и открыл иг

1 !3035, Москва, ж-- 35, Раушская наб., д. 4!5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4