Квадратор

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении специализированных вычислителей, функциональных преобразователей , устройств для обработки сигналов и информационно-измерительных систем . Цель изобретения - расширение класса решаемых задач за счет увеличения диапазона обрабатываемых чисел. Поставленная цель достигается благодаря введению в квадратор, содержащий регистр 1 аргумента , сумматоры 2 и 3, блок памяти 4, дешифратор 5 и группы элементов И 8.1-8.т, дополнительной группы 6 элементов И и коммутаторов 7.1-7.(т + 1), что позволило исключить устройство нормировки при работе с квадратором. 3 и„1. U S (Л СО 1чЭ СП 4 05 СО Фиг.1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (зц4 G06 F7 552

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ. 8e ) (54) КВАДРАТОР (57) Изобретение относится к цифровой вычислительной технике и может быть исФиг.1 (21) 4039612/24-24 (22) 24.03.86 (46) 23.07.87. Бюл. № 27 (72) Ю. В. Хохлов, А. М. Литвин, В. Д. Циделко, С. В. Ляшенко и С. В. Шантырь (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 7881 06, кл. G 06 F 7/38, 1980.

Авторское свидетельство СССР № 1198516, кл. G 06 F 7/552, 1984.

ÄÄSUÄÄ 1325469 А 1 пользовано при построении специализированных вычислителей, функциональных преобразователей, устройств для обработки сигналов и информационно-измерительных систем. Цель изобретения — расширение класса решаемых задач за счет увеличения диапазона обрабатываемых чисел. Поставленная цель достигается благодаря введению в квадратор, содержащий регистр 1 аргумента, сумматоры 2 и 3, блок памяти 4, дешифратор 5 и группы элементов И 8.1 — 8.m, дополнительной группы 6 элементов И и коммутаторов 7.1 — 7. (m+1), что позволило исключить устройство нормировки при работе с квадратором. 3 ил.

1325469!

=2 Х (5) Х (0,!г), т. на интервале

2 - ТХ

1 (6) ФЪ<

Y== <1:+ . ) ; + с, i=1 (2) 55

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении специализированных вычислителей, функциональных преобразователей, устройств для обработки сигналов и информационно-измерительных систем.

Цель изобретения — расширение класса решаемых задач за счет увеличения диапазона обрабатываемых чисел.

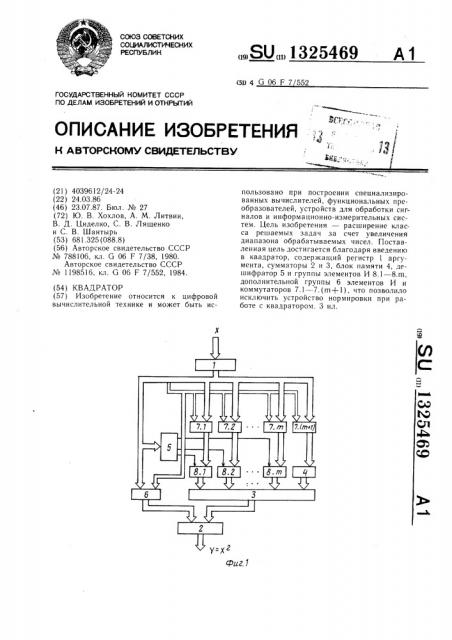

На фиг. 1 приведена структурная схема квадратора; на фиг. 2 — эпюры, поясняющие принцип преобразования; на фиг. 3— функциональная схема квадратора.

Квадратор (фиг. !) содержит регистр 1 аргумента, первый 2 и второй 3 сумматоры, блок 4 памяти, дешифратор 5, дополнительную группу элементов И 6, коммутаторы

7.1 — 7. (m+ 1), группы элементов И 8.1 — 8.m, В качестве регистра могут быть использованы, например, интегральные микросхемы К589ИР12, К155ТМ8 и др., в качестве 20 сумматоров — К155ИМ2, К155ИМЗ, в качестве блока памяти — К155РЕ 3, К556РТ4, К556РТ 5 и др., в качестве элементов И—

К155ЛИ1, в качестве коммутаторов

К155ЛП5, в качестве дешифратора

К155ИДЗ, К155ИД4.

Работа квадратора основана на принципе внешней кусочно-линейной аппроксимации (КЛА) исходной функции Y=X - Õ ((0,1) с последующей многоразовой параллельной коррекцией разности между исходной функцией и,ее приближением.

На фиг. 2 показана исходная функция

У=Х и аппроксимирующая ее функция <р.

На интервале Х< (О,+) <р= О, а на интервале

Х (— ",1) <р определяется уравнением касаЯ . 7 те.пьной к функции У= Х- в точке Х=-1. 35

О, Х C (О,—,"), (1)

2(Х вЂ” — ), Х (—,1).

Разность между функциями Y u <р — функ- 40 ция корреции D YI= Y — q (фиг. 2б) является симметричной функцией относительно оси, проведенной через точку Х= — — и на

1 интервале XC (О, - — ) DYI совпадает с функцией Y YI, может быть также. как и Y, аппроксимирована касательными в точке

Х= — . В свою очередь, разность YI—

1 — — Т<=.Я также выступает в роли функции коррекции и может быть аппроксимирована касательными (фиг. 2в). После m-го шаг;I к<(рр< кции (фиг. 2г) получают корректнр : он<ую функцик), тогда итоговые уравнения я преобразования ел< ануеT записать в внде

Значения коррекгирующей функции xpaIIsI <.sI в о Io(

Анализ показывает, что E — периодическая функция, симметричная на периоде относительно середины периода и

1 ь С 2 2(т+ и (3) Это означает, что при разрядности входного кода Х, равной N, объем блока памяти („(для хранения значений определяется выражением

Q= (N — 2(m+1)) 2 1 "+ ((4) из анализа которого следует, что количество шагов коррекции должно выбираться из условия m - — ——

)ч

Как видно из эпюр на фиг. 2, функция корреция g; является периодической с пе1 ридом Т;= — (<. Это означает, что достаточно задать функцию ф; на интервале (О; 2г:т), т.е. воспроизвести на первом пери1 оде, а на следующих использовать ту же функцию за счет смещения по оси Х. Кроме того, так как функция ф является симметричной функцией»а периоде Т; относительно середины периода и к тому же в первой и последней четвертях периода Т(„принимает нулевое значение согласно условиям построения КЛА, то функцию ф достаточно задать на интервале Х

C (2;.„ —,). Тогда уравнение; описывающее ф;, можно записать в виде где ЛХ=Х 2, — причем

ЛХ E (О 2 +

Для определения

Х (-(т,— ф ) можно воспользоваться той же формулой, заменив ь Х на л Х вЂ” дополнение ьХ до ZÜ;, ввиду симметрии функции ф,.

Из уравнений (!), (5) и (6) следует, что при определении < и <1., неободимо выполнять операцию умножения части аргумента

Х на некоторый коэффициент, определяемый как 2, где! — целое число. Это озна гает, что операция умножения может быть выполнена путем пространственного сдвига разрядов аргумента Х вправо или влево в зависимости от знака 1. Таким обрзом, работа комм,— таторов 7.1 — 7. (оп+1) заключается H гоч.

1325469

20 где (26 и значения хранятся в блоке

4 памяти объемом Q= 16)С 4 = 64 бит, управляемом через коммутатор 7.3 разрядами 3 — 6 входного кода Х. Для определения значения >рi и .> используются разряды

Π— 7 и 1 — 6 входного кода Х, так как значения аргумента этих функций лежат в ин- 45 тервалах) (О,— ") и (О,— „" ) соответственно, и при определении ф разряды входного кода дожны быть сдвинуты вправо на один разряд, что соответствует операции умножения па -у-.

Так как функции ф, ф>, являются симметричными при определении их значений на интервалах (— -, + для qi; (, -8 ) и

55 что в зависимости от участка апроксимации функций ф и F, они пропускают значения части Х без изменения или инвертируют, кроме того, на входах коммутаторов осуществляется пространственный сдвиг разрядов кода Х, т.е. выполняется операция умножения.

Управление коммутаторов осуществляется старшими разрядами Х через буферный повторитель. Работа элементов И

8.1 — 8 m состоит в том, что на участках аппроксимации, где 1 ; не равны нулю, они пропускают пространственно сдвинутые значения Х или их дополнения на вход второго сумматора 3. Управление элементами

8.1 — 8 гп осуществляет дешифратор 5, определяющий участки аппроксимации, где не равны О. Таким образом, на выходе вто рого сумматора 3 образуется значение суммы всех корректирующих функций ф,...,gm и — ф+ g, поступающие на первую груп1 пу входов первого сумматора 2. Значение функции р образуется на выходах дополнительной группы элементов И 6, причем преобразование (1) обеспечивается путем управления дополнительной группой элементов

И старшим разрядом кода Х через буферный повторитель и пространственным сдвигом на один разряд вправо при суммировании в первом сумматоре 2. Следовательно, на выходе первого сумматора 2 образуется значение Y = X согласно итоговому уравнению преобразования (2).

На фиг. 3 приведена функциональная схема квадратора для разрядности входного кода Х N = 10 (разряды пронумерованы с О до 9; 9 — старший разряд) при количестве шагов коррекции m= 2. Для этого случая уравнение преобразования следующее: у (р+ 11+ 1 2+ 1 (3 7 ), 1, (1 1) (s 1) (8 3) (- -,1) для ) используется тот же прием, что и для интервалов (", — ) для (oi, (—, ) и

1 1

4 Z S 4

4 з) для (> (О -1 — ) (1 — ) (— - -) и (.й (4

-- -) для, если в качестве аргумента использовать дополнение части кода Х. Операция дополнения обеспечивается коммутаторами 7.1 для Ч; 7.2 для Ч и 7.3 для1, которые выполнены на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ. Управление этими коммутатоми осуществляется разрядами 9.8 и 7 входного кода Х через буферный повторитель.

Выходы коммутаторов 7.1 и 7.2 подключаются к входам первой ступени сумматора

3 через элементы И 8. 1 и 8.2, управляемые дешифратором 5. Дешифратор 5 состоит из позиционного дешифратора трехразрядного двоичного кода в позиционный и двух элементов 4ИЛИ, с помощью которых формируются управляющие сигналы для групп элементов И 8.1 и 8.2.Группа элементов И 8.1 открыта на интервалах (вЂ, - -), (- -, †), (8 ) (+6 ° 4 ) т.e. (< ° ) группа 3. teментов И 8.2 — на интервалах (вЂ, †-), 1 1

$ (1 -з — ) (), (-, 7),т.е. (ф-) и (5-, 8). Это означает, что группы элментов

Формула изобретения

Квадратор, содержащий регистр аргумента, вход которого соединен с информационным входом квадратора, дешифратор, я групп элементов И (где и= 1+ 1од>а. а количество участков аппроксимации), блок памяти, первый и второй сумматоры, выходы первого из которых являются выходами квадратора, а первач группа входон первого сумматора подклюена к выходам второго сумматора, входы первого и второго слагае>мых которого соединены соответственно

И 8.1 и 8.2 открыты на тех интервалах, где функции >1;> и не равны О. Управление дешифратором 5 осуществляется тремя старшими разрядами кода Х (9, 8 и 7).

Таким образом, на выходе первой ступени сумматора 3 образуется сумма + ф>>, а на выходе второй, т.е. на выходе сумматора 3

+ р2+ g. Для определения ср часть входного кода Х (разряды Π— 8) через элементы

И 6 подключены к входам В1 — В9 сумматора 2, причем управление элментами И 6 осуществляется старшим разрядом (разряд9) ко да Х, обеспечивая ч>= О для XE(0,+). Следует отметить, что разряды Π— 8 кода Х подключены через элементы И 6 к входам сумматора 2 с пространственным сдвигом влево на один разряд, обеспечивая таким образом операцию умножения на два. Следовательно, на выходе сумматоре 2 образуется сумма y+ >(>>+ >1>>+, определяемая уравнением преобразования квадратора.

1325469

Y9"

z2

4Y,P< g г

1 1 5 1 .й Ю 2 1 Х

В а г а 4 г луу r

2г», о г

1 2m

2 -2

2 в+т

Ясг 2

Составитель Н. Шелобанова

Реда кто р В. Петра ш Техред И. Верес Корректор В. Бутяга

Заказ 3 l 10/44 Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 с выходми элементов И m групп и выходами блока памяти, управляющие входы элементов И т групп подключены к выходам дешифратора, входы которого соединены с выходами старших разрядов регистра аргумента, отличающийся тем, что, с целью расширения класса решаемых задач за счет увеличения диапазона обрабатываемых чисел, в него введены (m+1) коммутаторов и дополнительная группа элементов И, выходы которых подключены к второй группе входов первого сумматора, управляющие входы элементов И дополнительной группы и (т+1) коммутаторов соединены с выходами старших разрядов регистра аргумента, причем информационные входы элементов И дополнительной группы соединены с выходами остальных разрядов регистра аргумента и информационными входами (т+1) коммутаторов, а выходы т коммутаторов и выход (m+ 1)-ro коммутатора соединены с информационными входами элементов И m групп и адресными входами блока памяти соответственно.