Устройство приоритетного доступа к общей памяти

Иллюстрации

Показать всеРеферат

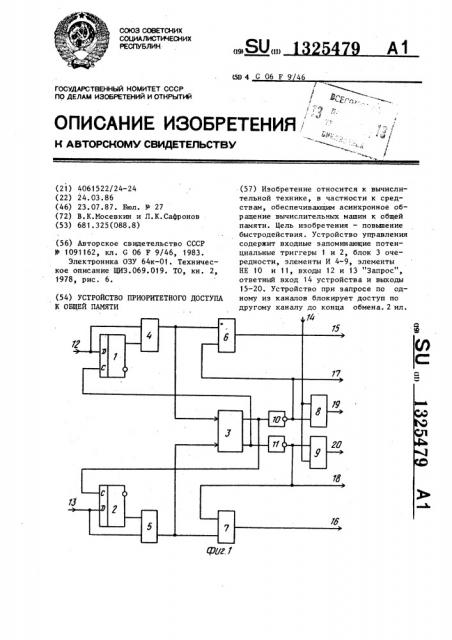

Изобретение относится к вычислительной технике, в частности к средствам , обеспечиваюпц1М асинхронное обращение вычислительных машин к общей памяти. Цель изобретения - повышение быстродействия. Устройство управления содержит входные запоминающие потенциальные триггеры 1 и 2, блок 3 очередности , элементы И 4-9, элементы НЕ 10 и 11, входы 12 и 13 Запрос, ответный вход 14 устройства и выходы 15-20. Устройство при запросе по одному из каналов блокирует доступ по другому каналу до конца обмена. 2 ил. 1U 15 О) с 77 Ю 8 79 7/1 20 78 76 Фиг.1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (1% (И) А1 (Ю 4 G 06 F 9 46

«

Р ф 1-.

«. К1,,, ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4061522/24-24 (22) 24. 03. 86 (46) 23.07.87. Бюл. Р 27 (72) В.К.Мосевкнн и Л.К.Сафронов (53) 681.325(088.8) (57) Изобретение относится к вычислительной технике, в частности к средствам, обеспечивающим асинхронное обращение вычислительных машин к общей памяти. Цель изобретения — повышение быстродействия. Устройство управления содержит входные запоминающие потенциальные триггеры 1 и 2, блок 3 очередности, элементы И 4-9, элементы

НЕ 10 и 11, входы 12 и 13 "Запрос", ответный вход 14 устройства и выходы

15-20. Устройство при запросе по одному из каналов блокирует доступ по другому каналу до конца обмена. 2 ил. (56) Авторское свидетельство СССР

11«1091162, кл. G 06 F 9/46, 1983.

Электроника ОЗУ 64к-01. Техническое описание ЩИЗ.069.019. ТО, кн, 2, 1978, рис ° 6. (54) УСТРОЙСТВО ПРИОРИТЕТНОГО ДОСТУПА

К ОБЩЕЙ ПАМЯТИ!

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,,-/

К ASTOPCHOMY СВИДЕТЕЛЬСТВУ

13

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для организации работы двух ЦВМ на общее поле памяти.

Цель изобретения — повышение быстродействия и надежности устройства.

На фиг.1 представлена функциональная схема устройства, на фиг.2 — функциональная схема блока очередности.

Устройство содержит триггеры 1 и .

2, блок 3 очередности, элементы И

4-9, элементы НЕ 10 и 11, входы 12 и

13 запроса, вход 14 ответа из общей памяти, выходы 15 и 16 обращения к общей памяти, выходы 17 и 18 выбора направления, выходы 19 и 20 ответа устройства. Блок 3 содержит элементы

И 21 и 22.

Устройство работает следующим образом.

В исходном состоянии от сопрягаемой аппаратуры на входах 12-14 устройства создаются потенциалы низкого . уровня "0", а на его выходах 15-20 формируются также потенциалы низкого уровня, так как на выходах элементов

И 4 и 5 создаются низкие потенциалы, что приводит к формированию на выходах блока 3 сигналов высокого уровня

"1" и "0" на выходе элементов НЕ 10 и 11. При этом на входах стробирования триггеров 1 и 2 поддерживаются сигналы 1", а на единичных выходах записывается "0".

В момент прохода по одному из входов 12 и 13 запроса сигнала "1" (пусть это будет сигнал запроса по входу 12) происходит запись в триггер 1 сигнала

"Запрос", и на его единичном выходе формируется потенциал высокого уровня "1". В связи с наличием на обоих входах элемента И 4 сигналов "1" на его выходе также формируется сигнал

"1" и в единичное плечо триггера записывается "0", при этом триггер 2 запирается по входу стробирования, на выходах 15 17 и 16 18 формируются соответственно сигналы "1" и "0" °

По выходу 17 устройство разрешает доступ к общей памяти по первому каналу, à по выходу 15 формируется потенциал высокого уровня, по переднему фронту которого общая память при наличии готовности производит обмен информацией, при завершении которого по входу 14 формируется сигнал "1", поступающий в первую вычислительную

25479 2 машину для снятия сигнала по входу 12 запроса. После этого схема устройства устанавливается в исходное положение.

5

В случае прихода сигнала "Запрос" по входу 13 на выходах 16, 18 и 20 формируются сигналы "1". Если во время обмена информацией, предположим, по первому каналу приходит сигнал

"Запрос" по входу 13 устройства, триггер 2 не записывает пришедший сигнап окончания обмена с первой вычислительной машины, а сразу же после окончания обмена, когда на единичном выходе блока 3 вновь сформируется

"1", происходит запись сигнала "Запрос" в блок 3 и начинается обмен информацией второй вычислительной машины.

При одновременном поступлении от обеих вычислительных машин сигналов

"Запрос" по входам 12 и 13 очередность обработки запросов устройством произвольная и определяется отклонениями параметров блока 3, при этом сначала производится обмен информацией с ОПП одной машиной, а после окончания сразу же с другой.

Формула

Устройство приоритетного доступа к общей памяти, содержащее два триггера, два элемента И, информационный вход первого триггера является первым входом запроса устройства и соединен с первым входом первого элемента И, второй вход которого соединен с прямым выходом первого триггера, информационный вход второго триггера является вторым входом запроса устройства и соединен с первым входом второго элемента И, второй вход которого соединен с прямым выходом второго триггера, о т л и ч а ю щ е е— ся тем, что, с целью повышения быстродействия, в него дополнительно введены четыре элемента И, два элемента

НЕ и блок очередности, причем выходы первого и второго элементов И соединены с первым и вторым входами блока очередности соответственно, первый и второЦ выходы блока очередности соединены с входами стробирования первого и второго триггеров соответственно, входы первого и второго элементов

НЕ соединены с первым и вторым выходами блока очередности соответственСоставитель В.Бородин

Техред Л.Сердюкова

Корректор В.Бутяга

Редактор В.Петраш

Тираж 672

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раутская наб., д. 4!5

Заказ 3111/45

Подписное

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 з 1325479

4 . но, выход первого элемента НЕ являет- и четвертого элементов И соответстся первым выходом выбора направления венно, выходы четвертого и шестого устройства и соединен с первыми вхо- элементов И являются первым и вторым дами третьего и четвертого элементов выходами обращения к общей памяти

И, выход второго элемента НЕ является устройства, выходы третьего и пятого вторым выходом выбора направления элементов И являются первым и вторым устройства и соединен с первыми вхо- выходами ответа устройства, вход отдами пятого и шестого элементов И, вета общей памяти устройства соединен выходы первого и второго элементов И 1д с вторыми входами третьего и пятого соединены с вторыми входами шестого элементов И.