Устройство для извлечения квадратного корня из суммы квадратов

Иллюстрации

Показать всеРеферат

Изобретение относится к аналоговой вычислительной технике. Цель изобретения - повышение быстродействия. Устройство содержит N ключей, N схем сравнения, шину опорного напряжения, первый интегратор , сумматор, блок вычитания, второй интегратор , нуль-орган, RS-триггер, N информационных входов, вход запуска. Входные напряжения подаются на сумматор в течение интервала времени от начала интегрирования опорного напряжения до сравнения каждого входного напряжения с линейным . Разность напряжения сумматора и линейного напряжения интегрируется до момента обнуления интеграла. Интервал времени от начала до момента обнуления соответствует искомой величине. 1 ил. оо ьо СП СЛ N3 Ю

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1325522 (51)4 G06G7 20

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ - ;, К АBTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 4036788/24-24 (22) 17.03.86 (46) 23.07.87. Бюл. № 27 (71) Институт прикладной физики АН БССР (72) С. Г. Сандомирский (53) 681.3(088.8) (56) Патент США № 3816737, кл. G 06 G 7/16, G 06 G 7/20, опублик. 1974.

Авторское свидетельство СССР № 955!08, кл. G 06 G 7/20, 1981. (54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ

КВАДРАТНОГО КОРНЯ ИЗ СУММЪ|

КВАДРАТОВ (57) Изобретение относится к аналоговой вычислительной технике. Цель изобретения — повышение быстподействия. Устройство содержит N ключей, М схем сравнения, шину опорного напряжения, первый интегратор, сумматор, блок вычитания, второй интегратор, нуль-орган, RS-триггер, N информационных входов, вход запуска. Входные напряжения подаются на сумматор в течение интервала времени от начала интегрирования опорного напряжения до сравнения каждого входного напряжения с линейным. Разность напряжения сумматора и линейного напряжения интегрируется до момента обнуления интеграла. Интервал времени от начала до момента обнуления соответствует искомой величине. 1 ил.

1325522

1()бретение (: носится к а(:I.loão:)<)É вы, (тел ьной гехни ке.

Цель изобретения — и:)!И.)п)ение б((с.(родействия.

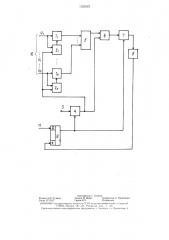

На чертеже представ. Сп(((хема l(редлагаемого устройства.

Устройстp<) с0, (ержит ключи I I — !х, сx(.м(, 2(2, сравнен;(и. !,.IHII(, 3 of орного

:);) (ряжения, первый инте! ратор 4, суM.)!à)р 5, блок 6 вычи гания, I: T()ðoé ин гсг рп гор 7, нуль-орган ":, RS-три(.гс р 9, информационные входы 1(), вход 11 запуска.

Устройство рабо! ает следую(цим образом.

П<п обра::yea, „.;i;ill",,:яжения UI..., U нос((li(ilt)I на cooT". гст)1(ю цие информационIII>I(Hõoä!ç1 I!) Г:)()ист(1(I. В исхОднОм сост()HI!(Ill интеграг<)ры 4 и 7 выключены, напряже;!ия ii::, и.; выходах равны нулю. К.)ючи 1, ° Открыты. Напряжение на выходе схмматор(! 5 и блока 6 вычитания равно сумме вхо.jl(llx. Б момент времени ti на l;iла III)Eобразования на второй установо

2(—, 2 сравнения, а также с весовым коэффициентом, равным двум, — — на вычитаюгций вход блока 6 вычитания. При достижении напряжением интегратора 4 величины о (ередного входного сигнала соответствуюгцая схема сравнения срабатывает и отключает это в.(одное напряжение от входа сумматора 5.

Таким образом, каждое входное напряжение !); и(пегрируется интегратором 7 в T(И, чение времени t; = т()-!, а напряжение на вых()де интегратора 4 после срабатывания всех схем сравнения имеет вид: н т)1:<)I=o т(т

П »I : ;:.;. (е ии срабатывает нульоргап .", (,);;; ãc ) :. отклк)чает интеграгоры. Пр .есс преобра ования заканчивается. РИICI-.I)û.i времени, проll:åäøèé от моменI а запуска до окончания интегрирования, П 3 (:(. Ii т=, qt .z,U,, а напряжение 1;1 на выходе интегратора 4

10 в момент времени окончания и(ггегрирования равно

tJÄ= ХЦ

2 (!

Формула изобретения

Устройство для извлечения квадратного корня из суммы квадратов, содержа(цее сумматор, N входов которого соединЕны че20 рез соответствующие ключи с информационными входами устройства, первый интегратор, информационный вход которого соединен с шиной опорного напряжения, а выход — с первым входом первой схемы сравнения, блок вычитания, второй интегратор, отличающееся тем, что, с целью повышения быстродействия, устройство содержит нуль-орган, RS-триггер и схемы сравнения с второй по N-ю. первые входы которых соединены с выходом первого интегратора, вторые входы N схем сравнения соединены с соответствующими информационными входами устройства, а их выходы — с управляю(цими входами соответствующих ключей, выход сумматора соединен с первым, а выход первого интегратора с вторым входами блока вычитания, выход которого соединен с информационным входом второго интегратора, выход которого через нуль-орган соединен с первым установочным входом RS-триггера, второй установочный вход которого является входом запуска устрой4О ства, а выход RS-триггера соединен с входом пуска интеграторов.

1325522

Составитель Г. Осипов

Редактор Н. Тупица Техред И. Верес Корректор Л. Пилипенко

Заказ 31! 3/47 Тираж б72 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раугвская наб., д. 4 5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная. 4