Ключ

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в автоматизированных системах контроля микропроцессорных БИС для коммутации напряжений и токов в широком диапазоне, для согласования логических элементов различных типов. При соответствующем выборе резисторов делителя напряжения на резисторах 5 и.16 и делителя на резисторах 8 и 17 обеспечивается симметричное управление выходными транзисторами 18 и 19, что позволяет изменять коммутируемые опорные напряжения в широком диапазоне как положительных, так и отрицательных значений и формировать на выходе ключа высокий и низкий уровни сигнала с идентичными нагрузочными и частотными характеристиками. Введение в предложенное устройство резистивных делителей напряжения, источника положительного напряжения смещения и выходных транзисторов, подключенных к источникам опорных напряжений повьш1ает быстродействие ключа и расширяет его функциональные возможности. 1 ил. 7 J-jSUt Л 20 Чоп2

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (ll) (59 4 Н 03 К 17/60

ОПИСАНИЕ ИЗОБРЕТЕНИЯ: (21) 3883773/24-21 (22) 15.04.85 (46) 23.07.87. Бюл. В 27 (54) КЛЮЧ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАЦ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

M А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (72) Ю.А.Безбородько, А.П.Иайоров и Ю.В.Кузнецов (53) 681.30.55(088.8) (56) Авторское свидетельство СССР, У 627590, кл. Н 03 К 17/60, 07 ° 12.76. . Патент ФРГ Р 2114215, кл. Н 03 К 17/60, 12.10.1972. (57) Изобретение относится к импульсной технике и может быть использовано в автоматизированных системах контроля микропроцессорных БИС для коммутации напряжений и токов в широком диапазоне, для согласования логических элементов различных типов. При соответствующем выборе резисторов делителя напряжения на резисторах 5 и.16 и делителя на резисторах 8 и 17 обеспечивается симметричное управление выходными транзисторами 18 и 19, что позволяет изменять коммутируемые опорные напряжения в широком диапазоне как положительных, так н отрицательных значений и формировать на выходе ключа высокий и низкий уровни сигнала с идентичными нагрузочными и частотными характеристиками. Введение в предложенное устройство резистивных делителей напряжения, источника положительного напряжения смещения а и выходных транзисторов, подключенных к источникам опорных напряжений повышает быстродействие ключа и расширнет его функциональные возможности. .1 ил. и.

13

Изобретение относится к импульсной технике и может быть использовано в автоматизированных системах контроля микропроцессорных БИС для коммутации напряжений и токов в широком диапазоне, для согласования логических элементов различных типов.

Цель изобретения — расширение функциональных воэможностей и повышение быстродействия.

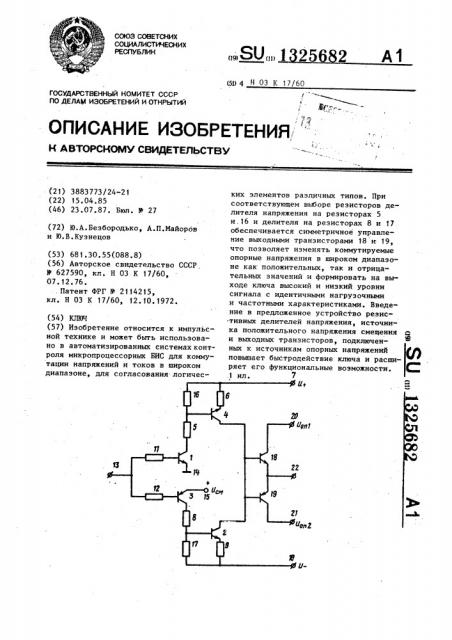

На чертеже представлена принципиальная электрическая схема ключа.

Ключ содержит первый 1 и второй 2 транзисторы одного типа проводимости, третий 3 и четвертый 4 транзисторы противоположного типа проводимости, первый 5 и второй 6 резисторы, положительный полюс 7 первого источника питания U +, третий 8 и четвертый 9 резисторы, отрицательный полюс 10 второго источника питания U â€, пятый 11 и шестой 12 резисторы, входную шину

13, общую шину 14, положительный полюс 15 источника напряжения смещения

П, седьмой 16 и восьмой 17 резисторы, пятый. 18 и шестой 19 транзисторы противоположного типа проводимости, первый 20 и второй 21 источники опорного питания Пд„,, П,„, выходную шину 22. При этом первые выводы пятого и шестого резисторов соединены с входной шиной, вторые выводы — соответственно с базой первого и третьего транзисторов, эмиттер первого транзистора соединен с общей шиной, эмиттер третьего — с положительным полюсом источника напряжения смещения.

Коллектор первого транзистора 1 соединен с первым выводом первого делителя напряжения, включающим первый 5 и седьмой 16 резисторы, второй вывод которого подключен к положительному полюсу 7 первого источника питания U+, и к первому выводу второго резистора 6, второй вывод которогс подключен к эмиттеру четвертого транзистора 4, база которого подключена к средней точке первого делителя напряжения, коллектор — к коллектору второго транзистора 2, эмиттер которого подключен к первому выводу четвертого резистора 9, бара — к средней точке второго делителя напряжения„ включающего третий 8 и восьмой 17 резисторы, первый вывод которого подключен к коллектору третьего транзистора 3, второй вывод — к отрицатель25682 2 ному полюсу 10 второго источника питания U — - и к второму выводу четвертого резистора 9, коллекторы пятого 18 и шестого 19 транзисторов подс, ключены соответственно к первому 20 .и второму 21 источникам опорного nuUon< UO« ЭМИттЕРЫ вЂ” К ВЫХОДной шине 22 ключа, базы — к общей точке соединения коллекторов второго 2 и четвертого 4 транзисторов.

Ключ работает следующим образом.

При наличии на входе ключа сигнала высокого уровня первый 1 и управляемый им четвертый 4 транзисторы открыты, третий 3 и управляемый им второй 2 транзисторы закрыты. Уровейь отпирающего четвертый транзистор сигнала определяется источником питания

U+ и первым делителем напряжения, Второй транзистор 2 запирается отрицательным сигналом, поступающим на его базу через восьмой резистор 17 с отрицательного полюса 10 источника

25 питания U-. Открытый четвертый транзистор 4 открывает пятый транзистор 18 и закрывает шестой 19. В результате на выходную шину 22 подается напряжение первого источника 20 опорного пи30 НН< Un1 UOns Uon2

При подаче на входную шину 13 ключа сигнала низкого уровня первый 1 и управляемый им четвертый 4 транзисторы запираются, а третий 3 и вто-рой 2 — открываются.

Уровень сигнала, отпирающего вто-, 35 рой транзистор 2, определяется вторым делителем напряжения, подключенным к источнику питания U — - и через тре40 тий транзистор 3 — к источнику напряжения положительного смещения UoÄ .

Четвертый транзистор 4 запирается положительным сигналом, поступающим на его базу через седьмой резистор 16 с. положительного полюса 7 источника

45 питания U+.

При этом открывается выходной шестой транзистор 19 и закрывается пятый 18. Через открытый шестой тран5g зистор 19 напряжение второго источника 2f опорного питания Uo 2 постуОП2 пает на выходную шину 22.

Введение резистивных делителей напряжения, источника положительного

55 напряжения смещения и выходных транзисторов, подключенных к источникам опорных напряжений позволяет повысить быстродействие ключа и расширить его функциональные возможности. При соотСоставитель И.Шевейко

Редактор Г.Гербер Техред И.Попович Корректор Л.Бескид

Заказ 3 124/55 Тираж 90.1 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная, 4 з 132568 ветствующем выборе резисторов первого делителя напряжения (первого 5 и седьмого 1б резисторов) и второго делителя (третьего 8 и восьмого 17 реэисто5 ров) имеет место симметричное управ- . ление выходными пятым 18 и шестым 19 транзисторами, позволяющее изменять коммутируемые опорные напряжения Uo« и U в широком диапазоне как голоon 2 жительнык, так и отрицательных значений, и тем самым формировать на выходе ключа высокий и низкий уровень сигнала с идентичными нагрузочными и частотными характеристиками. 15

Формула изобретения

Ключ, содержащий первый и второй транзисторы одного типа проводимости, о третий и четвертый транзисторы противоположного типа проводимости, коллектор первого транзистора соединен через первый резистор,с базой четвертого транзистора, эмиттер которого соеди- р5 нен через второй резистор с положительным полюсом первого источника питания, коллектор — с коллектором второго транзистора, база которого соединена через третий резистор с коллекто.ЗО ром третьего транзистора, эмиттерчерез четвертый резистор с отрицательным полюсом второго источника питания, отличающийся тем, что, с целью расширения функциональных возможностей и повышения быстродействия, введены пятый и шестой резисторы, первые выводы которых соединены с входом ключа, вторые выводы — с базами первого и третьего транзисторов соответственно, эмиттер каждого иэ которых соединен соответственно с общей шиной и с положительным полюсом источника напряжения смещения, седьмой резистор, который включен между базой четвертого транзистора и положительным полюсом первого источника питания, восьмой резистор, который включен между базой второго транзистора и отрицательным полюсом второго источника питания, пятый и шестой транзисторы противоположного типа проводимости, коллекторы которых соединены соответственно с первым и вторым источниками опорного питания, эмиттеры соединены с выходной шиной, базы — с общей точкой соединения коллекторов второго и четвертого транзисторов °