Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике и предназначено для преобразования большого числа аналоговых сигналов методом поразрядного уравновешивания с цифровой коммутацией каналов и одиночных широкополосных сигналов последовательно-параллельным методом. Целью изобретения является расширение функциональных возможностей за счет увеличения числа преобразуемых сигналов . в устройство, содержащее группу 1 с первого по ()-й компараторов, делитель 2 напряжения, два цифроаналоговых преобразоваетеля 7 и 10, параллельный регистр 3, первый аналоговый сумматор 11, блок управления 9, с целью расширения функциональных возможностей за счет увеличения числа преобразуемых сигналов введены мультиплексор 4, коммутатор 5, регистр 6 последовательногЪ приближения, счетчик 8 импульсов„ второй аналоговый сумматор 12. В устройстве обеспечивается измерение как сигнала U одного источника последовательно-параллельным методом преообразования, так и любого из сигналов ., , М источ-S НИКОВ методом поразрядного уравновешивания . 1 з.п.ф-лы, 4 ил. (Л с со 1C ел Oi со о:

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (51) 4 Н 03 И 1 14, 1/38

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

Г10 ДЕЛАМ И306РЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ .""""": ".

Фиг. 1

Н A ВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 4042012/24-24 (22) 25.03.86 (46) 23.07.87. Бюл. У 27 (71) Институт теплофизики СО АН СССР и Новосибирский государственный университет им.Ленинского комсомола (72) Е.В.Кожухова и В.И.Титков (53) 681.325 (088.8) (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к измерительной техникеи предназначено для преобразования большого числа. аналоговых сигналов методом поразрядного уравновешивания с цифровой коммутацией каналов и одиночных широкополосных сигHcUIoB последовательно-параллельным методом.

Целью изобретения является расширение функциональных возможностей за счет увеличения числа преобразуемых сигналов. В устройство, содержащее группу

1 с первого по (2 -1)-й компараторов, делитель 2 напряжения, два цифроаналоговых преобразоваетеля 7 и 1О, параллельный регистр 3, первый аналоговый сумматор 11 блок управления 9, с целью расширения функциональных возможностей эа счет увеличения числа преобразуемых сигналов введены мультиплексор 4, коммутатор 5, регистр

6 последовательного приближения, счетчик 8 импульсов,, второй аналоговый сумматор 12. В устройстве обеспечивается измерение как сигнала U одного источника последовательно-парал- лельным методом преообразования, так и любого из сигналов 0 -0,, М источ- 9 ников методом поразрядного уравновешивания. 1 з.п.ф-лы, 4 ил.

1 13?56

Изобретение относится к измерительной технике и может использоваться для преобразования одино нных аналоговых сигналов последовательно-параллельным методом и .большогс числа аналоговых сигналов метоцом поразрядного уравновешивания с цифровой коммутацией каналов.

Целью изобретения является расширение функциональных вазможностей за счет увеличения числа преобразуемых сигналов.

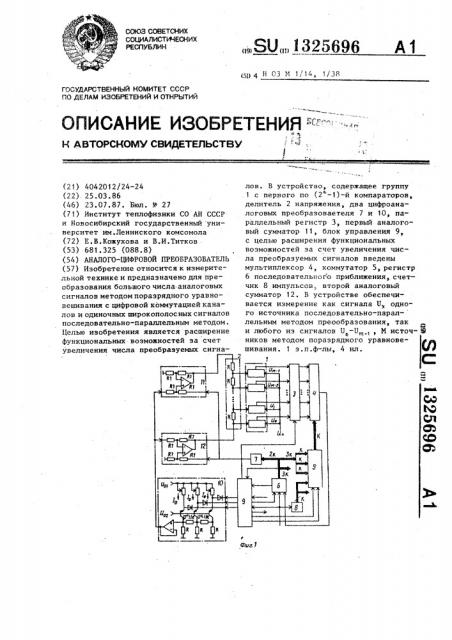

На фиг.1 приведена функциональная схема устройства; на фиг,2 — схема блока управления на фиг.З и 4 — вре-- 15 менные диаграммы, поясняющие работу устройства в многоканальчсм и одноканальном режимах работы соответственно.

Устройство содержит группу 1 ксиА параторов 1.0-1.И, где И = 2, делитель 2 напряжения, параллельный регистр 3, мультиплексор 4, коммутатор

5, регистр 6 последовательного" приб-лижения, первый цифроаналоговый преобразователь (ЦАП) 7, счетчик 8 импульсов, блок 9 управления, второй

ЦАП 10 первый 11 и второй 12 аналоговые сумматоры.

Блок 9 управления содержит 13-триг- 30 гер 13, тактовый генератор 14, первый мультиплексор 15, первый демультиплексор 16, первый элемент И 17, первый счетчик 18 импульсов, второй мультиплексор 19, второй счетчик 20 импульсов, элемент ИЛИ-НЕ 21, второй

В-триггер 22, элемент HF. 23, третий счетчик 24 импульсов, второй 25 и третин 26 элементы И, второй демультиплексор 27 и одновибратор 28.

На временных диаграммах (фиг.3) многоканального режима показан измеряемый сигнал U< на втором входе компа-ратора 1 1, где 1=0,1,...,М-1, отмечены моменты t u t начала и конца

I цикла преобразования, моменты с. стро1 бирования регистра 6 последовательного приближения, где i.=0,1,...,2K, моменты t стробирования регистра 3, I где i 1, «2К и показана величина .,л н

t одного такта преобразования. Иа временных диаграммах (фиг,4) одноканального режима показан измеряемый сигнал П „ ка вторых вхоцах ксмпараторов 1,0-1,N-1, отмечены моменты с и t начала и конца цикла пресбразс1 вания, моменты t . изменения кода на

1 входах ЦАП 10 и ка адресных входах коммутатора 5, где i=0 1 и 2, момек96 2

abI t. стробирования регистра 3; где

1=1 2 и 3, и величина t одного такТо та преобразования. Кроме того, на диаграммах (фиГ.З и 4) показаны величины Ц амплитудного диапазона ЦАП 7 и его выходной спгHQJ: Пц, сигнал Ь на прямом выходе генератора 14 и период его частот„U,„и -Ц„, на первом и втором входах делителя 2., сигналы I1-I4 ка первом-четвертом входах блока !3 н сигналы 01-08 на его первом-восьмом выходах.

Устройство работает следующим образом.

На первые и вторые входы аналоговых сумматоров 11 и 12 поступают выходные сигналы Ц (t) UAH ? z U« (t)

ЦАП 10, а на их выходах образуются соответственно суммарный сигнал +U „, равный U„(t)+U„,(t) и разносткый сигнал -11 „, ранний И,,(t)-Ц.,(t). Эти сигналы поступают на входы делителя

2 из М одинаковых регистров, а с его выходов — на первые входы компараторов 1.0-1.И-1. На вторые входы компараторов 1.0-1.,И-1 поступают в многоканальном режиме работы М измеряемых сигналов U -U,„,, а в одноканальном режиме — один измеряемый сигнал U>

ПАП 10 управляет блок 9, а ЦАП ? регистр 6 последовательного приближения. В мнс "оканальном режиме на вход ЦАП 10 поступает нулевой код с выходов блока 9, что обеспечивает нулевой сигнал UÄ (t) ка вьжоде ЦАП 10 и., соответственно, позволяет сформировать на первых входах всех компараторов одинаковый сигнал, равный П,„(г.), Таким образом„ в многоканальном режиме производится сравнение каждого из измеряемых сигналов U -U, с эталонным сигналом U (t) ЦАП 7 с помощью коипараторов 1.0-1.N-1. В одноканальном режиме ка входах ЦАП 10 формируется такая последовательность двоичных кодов, что выходной сигнал

U

Ф

Это обеспечивает формирование на первых входах коикараторов 1,0-1 ° N-1 вначале "грубой" шкалы опорных напряжений первого такта в диапазоне 0„(с )-ц /2-UI„(t )+U /2, затем более точной шкалы второго такта в диапазоне и наконец точной шкалы третьего такта в диапазоне Ьч (t <) -д . -Ца,(С3)+

696 4 приближения следующим образом. В исходном состоянии старший разряд (иэ группы н К разрядов) РПП 6 установлен в единичное состояние, а все младшие его разряды — в нулевое, таким образом, на адресных входах мультиплексора 4 установлен двоичный номер компаратора 1.M/2. Соответственно, выходной сигнал этого компаратора (этого разряда регистра 3) поступает на информационный вход РПП 6. По тактовому сигналу в старший разряд РПП 6 заносится значение сигнала компаратора 1.М/2 и одновременно более младший,разряд РПП 6 устанавливается в едикицу.и, таким образом, формируется номер компаратора, который будет опрашиваться следующим сигналом. Если выходной сигнал компаратора 1.М/2 равен нулю (значит, и сигналы всех компараторов с большими номерами тоже равны нулю в унитарном коде), то на адресных входах мультиплексора фор мируется номер компаратора 1.М/4, а в противном случае — номер компаратора 1.3М/4 и т.д., т.е. на адресных входах мультиплексора 4 формируются номера компараторов по алгоритму по- . следовательного приближения. Такой способ шифровакия является быстродействующим, так как на получение К- разрядного двоичного кода из М-разрядного унитарного затрачивается время, равное К t, где период tE частоты тактировакия РПП 6 в этом случае выбирается исходя из времени суммар-, ной задержки в РПП 6, коммутаторе 5 и мультиплексоре 4, например, на по лучение трех-четырех разрядного дво" ичного кода из семи-, 15-разрядногоунитарного кода затрачивается время порядка 100-120 кс, что вполне сравнимо с временем задержки в параллель" ном приоритетном шифраторе известного устройства.

Таким образом, схема совмещает на своих элементах два отдельных устройства, выбор любого из которых осуществляется путем установки соответствующего кода режима на втором входе блока 9 управления (фиг.2), и позволяет произвести преобразование одного измеряемого сигнала U последовательУ но-параллельным методом и получить

ЗК-разрядный результат за три такта и преобразование любого из входных сигналов Б,-П, его каналов путем занесения двоичного номера этого канала в счетчик 8 на время текущего

3 1325

+El 2 ""1 с которыми сравнивается

Itl измеряемый сигнал U с помощью компараторов 1.0- 1.М-1. Это позволяет получить последовательность М-разрядных унитарных эквивалентов сигнала U> с точностью U„(t,)+11„,2, U.(t )+

+U . 2 " " и U (t )+U ° 2 " 1 в neptn 3 вом, втором и третьем тактах соответственно, Результаты сравнения входных сигналов с эталонными сигналами зано- 10 сятся в моменты t. в регистр 3, а с

его выходов поступают на информационные входы мультиплексора 4, которым управляет выходной код коммутатора 5.

В многоканальном режиме íà адрес- 15 ных входах коммутатора 5 постоянно установлен адрес его нулевого группового входа. Это обеспечивает подключение к адресным входам мультиплексора 4 выходного кода счетчика 8, в ко-20 тором находится двоичный номер канала 1, сигнал U которого подлежит преобразованию в текущем цикле с -с и позволяет подключить выход компаратора 1.1 через регистр 3 и мультиплексор 4 к информационному входу регистра 6 последовательного приближения (РПП) и получить в РПП 6 двоичный 2К-разрядный эквивалент сигнала

U эа 2К тактов с помощью ЦАП 7 мето- 30

0 дом поразрядного уравновешивания.

В одноканальном режиме на адресных входах коммутатора 5 формируется последовательность двоичных адресов вначале его третьего, затем второго и наконец первого груцповых входов, что обеспечивает подключение к .адресным входам мультиплексора 4 выходного кода вначале К старших, затем К последующих и, наконец, К млад-4р ших разрядов РПП 6 в первом, втором и третьем тактах преобразования соответственно. Это позволяет произвести преобразование М-разрядных унитарных эквивалентов сигнала U„(t,), U «(t<) 45 и U „(t >) в его К-разрядные двоичные эквиваленты старших, промежуточных и младших разрядов РПП 6 с помощью мультиплексора 4, коммутатора 5 и блока 9 управления и получить в РПП

6 ЗК-разрядный двоичный эквивалент сигнала U /t1) за три такта с помощью ЦАП 7 последовательно-параллельным методом.

Преобразование М-разрядного унитарного Мода компараторов 1.0-1.М-1, хранящегося в регистре 3, в К-разрядный двоичный код РПП 6 осуществляется по алгоритму последовательного

5 132 696 . 6 цикла преобразования и получить 2К- сится результат срс разрядный результат методом пораэряд- И„- со шкалой онори ного уравнове?ии13ания за 2К тактов.

Так, например, временные диаграммы фиг.3 поясняют работу схемы на примере работы 8-канального 6-разрядного устройства, перестраиваемого в одноканальное 9-разрядное устройство, работу которого поясняют диаграммы фиг.4. 10

В момент й, поступления запускающего сигнала Т1 на первый вход блока

9 управления (фиг.2) в устройстве начинается ??икл преобразования. В зависи?ласти от значения кода Х2 на вто- 15 ром входе блока 9 управления на его выходах 01-08 вырабатывается последовательность управляющих сигналов многоканального (фиг.3) или одноканального (фиг.4) режимов. При работе 20

i в ?лногоканальном режиме в моменты с: вырабатываются импульсы тактирования

РПП 6. По тактовому импульсу в момент с РПП 6 устанавливается в исходное состояние {старший разряд — в единич- 25 ное состояние, а все остальные разряды — в нулевое), и, соответственно, выходной сигнал П„ D)?П 7 достигает к моменту t исходного состояния и ра-1 вен половине амплитудного диапазона

U>, Так же, в момент t, содержимое счетчика 8 увеличивается на единицу и на его выходах устанавливается двоичный номер канала 1, сигнал U которого подлежит преобразованию в текущем цикле с<-t . Результаты сравнений сигнала U с эталонным сигналом

U заносятся в моменты t. в регистр

3, поступают с выхода 1-го его разряда через мультиплексор 4 на инфор- 10 мационный вход РПИ 6 и заносятся в ! него в моменты t,, что обеспечивает уравновешнвание си U2 талонн сигналам U по алгоритму йоразрядного уравновешивания эа время, равное

2K t „, где t „=Н .t, причем период

t< генератора 14 (фиг.2) определяется временем суммарной задержки сигналов в мультиплексоре 4, РПП 6 и коммутаторе 5 а коэффициент пересче- о та Н счетчика 18 выбирается иэ условия, что время ?.„„ не меньше времени переходного процесса в ЦАП 7 (ЦАП 10), ?внения сигнала

ых напряжений первого такта. На интервале t.-t, проис3 ходит г3реобразование М-раэрядногс унитарного эквивалента сигнала U„(t }

1 .в двоичный К-разрядный код старших разрядов РПП 60 а на интервале t

Ю 1

2 происходит грубое уравновешивание сигнала U< сигналом П и установка

?? шкалы более точных опорных напряжений второго такта. В момент t„ pe2 зультат сравнения сигнала 4 с этой шкалой заносится в регистр 3 и преобразуется на интервале t t„ в двоич2 2 ный К-разрядный код следующях разрядов РПП 6, в соответствии с которым происходит более точное уравновешиванне сигнала Ц„ сигналом Uö на интервале t --t ., Так же на этом интерз з вале устанавливается шкала опорных напряжений третьего такта, результат сравнения с которой сигнала U.(tэ) заносится в момент с a pe? acTp 3 и преобразуется на интервале t,-t., в

К разрядный двоичный код Злладших раз рядов РПП 6. Таким образом, в устройстве формируется ЗК-разрядный результат преобразования сигнала П„ за время 3 t, где t „ — 1„Н+К)-

В устройстве обеспечивается измерение как сигнала U одного источника последовательно-параллельным методом преобразования, так и любого иэ си1налов ц -U„, М источников методом поразрядного уравновешивания, что расширяет функциональные воэможностипредлагаемой схемы, а следовательно, и область ее применения по сравнению с известной. Предлагаемая схема позволяет получить существенный экономический эффект„ так как одно предлагаемое устройство с гибкими, програм" мно-изменяемьвли параметрами заменяет собой два таких отдельных устройства, как одноканальное госледовательно-параллельное устройство и М-канальное устройство поразрядного уравновешивания с цифровым коммутатором кана лов, что обеспечивает сокращение затрат как на разработку, так и на изготовление. формула изобретения сумматорах 11 и 12, компараторах

1.0- 1.II — 1, регистре 3„ мультиплексоре 4 и РПЛ б. Р одноканальном режиме на интервале t,-с, происходит уста11овка устройства в исходное состояние, а в момент tÄ в регистр 3 зано1. Аналого-цифровой преобразователь, содержащий группу с первого цо ъ,» (2 -1)-й компараторав первые входы которых соединены соответственно с выходами делителя налряженчя, первый

10 результата".

7 132 цифроаналоговый преобразователь, параллельный регистр, первый аналоговый сумматор, блок управления, первый, второй и третий выходы которого подключены соответственно к первому, второму и третьему входам второго цифроаналогового преобразователя, о т л ич а ю шийся тем, что, с целью расширения функциональных возможностей за счет увеличения числа преобразуемых сигналов, в него введены мультиплексор, коммутатор, регистр последовательного приближения, счетчик импульсов, второй аналоговый сумматор, выход которого соединен с первым входом делителя напряжения, второй вход которого подключен к выходу первого аналогового сумматора, первый вход которого объединен с первым входом второго аналогового сумматора и подключен к выходу второго цифроаналогового преобразователя, а второй вход объединен с вторым входом второго аналогового сумматора и подключен к выходу первого цифроаналогового преобразователя, первые и вторые входы которого объединены соответственно с первыми и вторыми информационными входами коммутатора, подключены соответственно к первым и вторым выходам регистра последовательного приближения и являются первыми и вторыми выходами информационными шинами, а третьи информационные входы коммутатора объединены соответственно с третьими выходами регистра последовательного приближения и являются третьими выходными информационнымишинами, причем выходы коммутатора соединены соответственно с адресными входами мультиплексора, выход которого подключен к информационному входу регистра последовательного приближения, а информационные входы соединены соответственно с выходами параллельного регистра, информационные входы которо о подключены соответственно к выходам компаратором группы, вторые входы которых являются соответствующими входными информационными шинами, при этом чет-, вертый выход блока управления соединен с тактируемым; входом регистра последовательного приближения, вход установки которого объединен с первым входом блока управления и суммирующим входом счетчика импульсов и являются шиной "Пуск", причем выходы счетчика импульсов соединены соответственно с четвертыми информационными

5696 8 входами коммутатора и являются шинами кода номера канала, второй вход ,блока управления является шиной режима, а третий вход подключен к четвертому выходу регистра последовательного приближения, выход "Конец преобразования" которого соединен с четвертым входом блока управления, пятый и шестой выходы которого соединены соответственно с первым и вторым адресными входами коммутатора, седьмой выход подключен к входу синхронизации параллельного регистра, а восьмой выход является шиной "Готовность

2. Преобразователь по п.1, о т— л и ч а ю шийся тем, что блок управления выполнен на первом и втором D òðèããåpàõ, тактовом генераторе, первом и втором мультиплексорах, первом и втором демультиплексорах, первом, втором и третьем элементах

И, первом, втором и третьем счетчиках импульсов, элементах ИЛИ-НЕ и

НЕ и одновибраторе, вход которого объединен с входом синхронизации первого D-триггера, подключен к выходу первого мультиплексора и является восьмым выходом блока управления, первым входом которого является вход установки в "1" первого D-триггера, информационный вход которого является шиной логического нуля, а прямой выход соединен с входом управления тактового генератора, прямой выход которого подключен к информационному входу первого демультиплексора, а инверсный выход соединен с входом стробирования первого мультиплексора, первый и второй информационные входы которого являются соответственно третьим и четвертым входами блока управления, а адресный вход объединен с первыми входами первого, второго и третьего элементов И, адресным входом второго мультиплексора, информационным входом второго демультиплексора и является вторым входом блока управления, четвертым входом которого является выход второго мультиплексора, первый информационный вход которого объединен с первым входом элемента ИЛИ-.НЕ, входом элемента НЕ, входом суммирования третьего счетчика импульсов и подключен к выходу переноса первого счетчика импульсов, вход суммирования которого соединен с первым выходом первого демультн1?>2 .?696 предустанОвки нервов ? сне » ч>!к » явля"" >>о > а !»1

""-">»-Г; 1 (r с 1 — C(»» =: —;-,>j 2»3

» 1 J ! ! (« r r

Г

»

» .1>?, Гp»>г

» »3 «с> 3

3. (1

> .Л

> >

>>> >, -3 б

:j

Щ„! >

I>:- - -"-

» !

" т °

Г»=т-= -c» >> T

Д (И

„. ......... .Л

Р. » — ==-- —: у

1

1! 1

> 1 (»>» Е

h4»

;»лексора,, адресный вход которого под-кл»очен к выходу первого эпемента 3», в"> Орой» EIOEI KOTopoE o ooc.>»«I»E»."-.!» с пряМЫМ ВЬ»ХОДОМ BTOPOI ? >»3 ТРИГ" PP> I ИН "

E3epcH6Æ выход соединен с его инфорМаЦИОККЫМ ВХОДОМс ВХС»Д СИ -»ХР )НИЗЯЦИ » подкп»пче»» к Выходу олемен-a NiY;--HV., а вход установки E3» об 6j-:,è»»åj» <"

»>»> входами синхронивации первого. т.торого и третьего счетчи»;ов импул».сов и соединен с вьв»одом одновибрато»?»» „

ПРИЧЕЬ» ВЫХОД ПРРРНОСР«HTO ?>?ÃO С E>=ТЧ>Ч ка соединен с Вторым входом э»»еме:- :та

РЛЯ-НК вход суммиро»-". »н»»Я с>бъед»»»! и с вторым информацион»3ым в-к»?1!.-,,» Втоь?сго мультинлексОра и»3»одк!»»Оч>ен к Бто рок»у Выходу первого дРмулт, типлексс Ва а Вх о дь? ? 3 р е ц с T а н о в к и я») !» я »>«т с я с, Р

> ветственно Шинами кода», >> -2 >, Вход»ь!

vTcs! cooTE3eToTE!анно ш3»»»ам»» кода (И» ) с

Где »! — коэффициент кратности времени такта уст»? Ойства периоду частоты тактОВОГО Ге»!ВРатОРас пРPEÇI>»A и ВтОРОй адресные входы второго демультиплексора объединены соответственно с вторыми Входами ВтО>>?ОГО и трс тьР ГО элементов И и нодкл»»?чень» соответств(-нно к выходам первого и второго раэрядов

j(7 ТРРТНЕГО СЧЕТЧИКа ИМПУЛЬСОВ П>»?> bg и второй вход!.! предустановки которо-! о явля»»?Тся соОтВетстВРННО шинами лОГН

-»:.ñêoãà нуля и логической единицы, перВЬ»М с ВТРРЬ»М И ТРЕТЬИМ ВЫХОДаМИ ЬЛ>ЭКа УП

»5»?Яе»3»ения являк>тся сООтзетственно пер»3ый, второй и третий выходы второго ре-мультиплексора, а лятьж, нтесты»» н седьмым вь»ходами .- Выходы соответстве:p.

>.: Т».?;.?»? Г о 33 т р е т 6 е Г о 3 л е и е и т О В» н э л е и е и

1325696

Р

If

lt гд

Е4

Of

ff

OI

ФФ

4 ti и г

os

Ob о

Уие Ф

Составитель Ю.Спиридонов

Техред И. Попович

КорРектоР В.Бутяга

Редактор И.Николайчук

Заказ 3124/55 Тираж 901

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная,4