Преобразователь перемещения в код

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью упрощения в преобразователе, содержащем формирователь 1 импульсов точно06 го отсчета (ТО), регистр 2, блок 3 сравнения и сумматор 4, один выход формирователя 1 подключен к С-входу регистра 2 и управляющему входу блока 3 сравнения, сумматор 4 выполнен в виде реверсивного счетчика, а блок 3 сравнения содержит сумматор 5 и элементы И 5 и 7. В конце каждого цикла преобразования на одном выходе формирователя 1 вьфабатывается импульс . В сумматоре 5 происходит вычитание кода предыдущего цикла из кода текущего цикла. Если между соседними циклами преобразования произошел переход через границу диапазона ТО в сторону увеличения перемещения, то инверсные выходы старщего разряда суммы и переполнения сумматора 5 будут в единичном состоянии и в сумматор 4 запишется +1. При переходе через границу диапазона ТО в сторону уменьшения перемещения в сумматор 4 запишется -1. 1 з.п. ф-лы, 1 ил. I (Л с со ls ел

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 Н 03 M 1/30

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ р »-, „

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ., К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3984949/24-24 (22) 02. 12.85 (46) 23.07.87. Бюл. ¹ 27 (71) Московский институт радиотехники, электроники и автоматики (72) M.А. Габидулин и И.Д. Лейбович (53) 681.325(088.8) (56) Электромеханические преобразователи угла с электрической редукцией:

/Под ред. А. Ахметжанова.-М.: Энергия, 1978, с. 201, рис. 6-9.

Авторское свидетельство СССР

Р 746657, кл. G 08 С 9/04, 1978. (54) ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЯ В

КОД (57) Изобретение относится к автоматике н вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью упрощения в преобразователе, содержащем формирователь i импульсов точноÄÄSUÄÄ 1325700 А1 го отсчета (ТО), регистр 2, блок 3 сравнения и сумматор 4, один выход формирователя 1 подключен к С-входу регистра 2 и управляющему входу блока 3 сравнения, сумматор 4 выполнен в виде реверсивного счетчика, а блок

3 сравнения содержит сумматор 5 и элементы И 5 и 7. В конце каждого цикла преобразования на одном выходе формирователя 1 вырабатывается импульс. В сумматоре 5 происходит вычитание кода предыдущего цикла из кода текущего цикла. Если между соседними циклами преобразования произошел переход через границу диапазона ТО в сторону увеличения перемещения, то инверсные выходы старшего разряда суммы и переполнения сумматора 5 будут в единичном состоянии и в сумматор 4 за. пишется +1 . При переходе через гре- ( ннцу диапазона ТО в сторону уменьшения перемещения в сумматор 4 запишет- 2 ся -1 . 1 э ° tl JIbl 1 3адрб

Изобретение относится к автоматике и вычислительной техники и может быть использовано для связи аналоговых источников информации с цифровым вычис5 лительным устройством.

Целью изобретения является упрощение преобразователя.

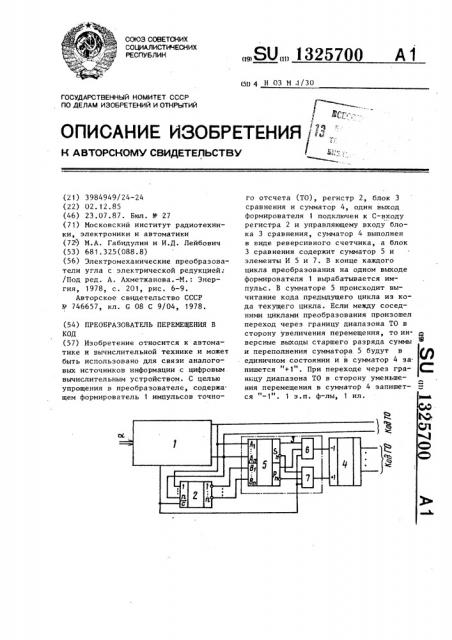

На чертеже представлена структурная схема преобразователя перемещения 1О в код.

Преобразователь содержит формирователь 1 кода точного отсчета (ТО), регистр. 2, блок 3 сравнения, сумматор

4, выполненный в виде реверсивного счетчика. Блок 3 сравнения содержит сумматор 5 и элементы И 6 и 7. Формирователь 1 кода ТО содержит блок преобразования перемещения в код и регистр.

Преобразователь работает следующим образом.

700 2 мерениями элементы И 6 и 7 закрыты по одному из входов и импульсы на вход реверсивного счетчика не поступают. В результате в конце каждого цикла преобразования на выходе формирователя 1 формируется текущее значение кода ТО, а на выходе реверсивного счетчика 4 — текущее значение кода грубого отсчета.

Максимально допустимое перемещение между соседними циклами преобразования в сторону увеличения перемещения составляет 0,5 с, (где с — диапазон перемещения в ТО), а в сторону уменьшения перемещения (0,5 — — 2-„)» где и — число разрядов кода ТО на выходе формирователя 1 (регистра 2)..

Формула изобретения

В конце каждого i-цикла преобразо25 вания на одном выходе формирователя

1 .вырабатывается импульс окончания цикла преобразования, а на группе выходов формирователя 1 вырабатывается код ТО. В сумматоре 5 происходит суммирование кодов ТО текущего i-цик30 ла с выходов формирователя 1 и предыдущего (i-1)-цикла с инверсных выходов регистра 2..Если между соседними циклами формирования кодов ТО происходит переход через границу диапазона З5

ТО в сторону увеличения перемещения, то после суммирования инверсные выходы старшего разряда суммы и переполнения сумматора 5 оказываются в единичном состоянии. Выходной импульс "О формирователя 1 проходит через открытий элемент И 7 на вход суммирования реверсивного счетчика 4. Задним фронтом этого импульса код ТО текущего

i-цикла заносится в регистр 2. Если 45 между соседними циклами формирования

1 кодов ТО происходит переход через границу диапазона ТО в сторону уменьшения перемещения, то после суммирования в единичном состоянии прямые выходы старшего разряда суммы и переполнения сумматора 5. Выходной импульс формирователя 1 проходит через открытый элемент И 6 на вход вычитания реверсивного счетчика 4. 55

При отсутствии перехода через гранину диапазона ТО между соседними из1. Преобразователь перемещения в код, содержащий формирователь кода точного отсчета, группа выходов которого подключена к 0-входам регистра и к первой группе входов блока сравнения, к второй группе входов которого подключены выходы регистра, первый и второй выходы блока сравнения подключены к соответствующим входам сумматора, .отличающийся тем, что, с целью упрощения преобразователя, один выход формирователя кода точного отсчета подключен к С-входу регистра и к управляющему входу блока сравнения, а сумматор выполнен в виде реверсивного счетчика.

2. Преобразователь по п. 1, о т л и ч а ю шийся тем, что блок сравнения содержит сумматор, первый и второй элементы И, первая и вторая группы входов сумматора являются соответственно первой и второй группами входов блока сравнения, прямые выходы переноса и старшего разряда сумматора подключены к первому и второму входам первого элемента И, инверсные выходы переноса и старшего разряда сумматора подключены к первому и второму входам второго элемента И, третьи входы первого и второго элементов И являются управляющим входом блока сравнения, а выходы первого и второго элементов И являются соответственно первым и вторым выходами блока сравнения.