Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для создания управляющих автоматов . Цель изобретения состоит в экономии оборудования за счет разделения выходных сигналов на статические и одиночные динамические сигналь: . Уст ройство содержит регистр 1 задания режима, блок 2 памяти микрокоманд , регистр 3, содержащий поле 4 и поле 5, дешифратор 6, мультиплексор 7. Указанная цель достигается с помощью вьшеуказанной совокупности признаков. 6 ил. с (Л ОО ГС

СОВХОЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (5D 4 G 06 F 9/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сфд

Ю

Ю

4ь

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21).3964178/24-24 (22) 14.10.85 (46) 30,07.87. Вюл. Р 28 (72) А.И,Обросов, Ю,Т.Галиев, В.В.Кирпиченко и В.Д.Руденко (53) 681,3 (088.8) (56) Авторское свидетельство СССР

Р 935958, кл. G 06 Р 9/22, 1981.

Авторское свидетельство СССР

Р 964640, кл. С 06 F 9/22, 1981.

„„SU„, 1327104 А 1 (54) 11ИКРОПРОГРАИМНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ (57) Изобретение относится к вычислительной технике и может быть использовано для создания управляющих автоматов. Цель изобретения состоит в экономии оборудования sa счет разделения выходных сигналов на статические и одиночныз динамические сигналы. Устройство содержит регистр 1 задания режима, блок 2 памяти микрокоманд, регистр 3, содержащий поле 4 и поле 5, дешифратор 6, мультиплексор 7, Указанная цель достигается с помощью вышеуказанной совокупности признаков. 6 ил.

1327104

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении управляющих автоматов. . 5

Целью изобретения является экономия оборудования.

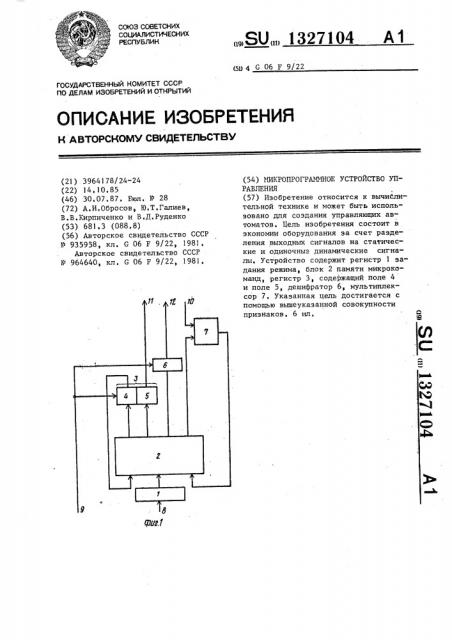

На фиг. 1 приведена структурная схема устройства; на фиг, 2 — графсхемы фрагментов алгоритмов, которые 10 способно выполнять предлагаемое устройство; на фиг. 3 — принцип размещения микропрограмм вышеуказанных фрагментов алгоритмов в блоке памяти; на фиг ° 4 — блок памяти микрокоманд; 15 на фиг. 5 — временные диаграммы работы устройства; на фиг. 6 — временная диаграмма выполнения первого такта алгоритма, Микропрограммное устройство управ- 2р ления (фиг. 1 ) содержит регистр 1 задания режима, блок 2 памяти микрокоманд, регистр 3 микрокоманд, содержащий поле 4 адреса, поле 5 микроопераций (выходной статической функции), 25 дешифратор 6, мультиплексор 7 логических условий, вход 8 задания режима устройства, вход g синхронизации устройства, вход 10 логических условий устройства, Выход l1 является 30 первым выходом микроопераций устройства, выход 12 — вторым выходом микроопераций устройства, Адресное поле блока 2 памяти (фиг. 4) включает в себя поле 13 кода, 35 текущего состояния, поле 14 кода режима, поле 15 кода внешнего условия. Поле выходов блока 2 памяти подразделяется на поле 16 адреса, первое поле 17 микроопераций параллельного кода выходной статической функции, второе поле 18 микроопераций кода выходных импульсных сигналов, поле 19 кода логических условий.

Устройство работает следующим об- 45 разом (фиг. 5 и 6 ), До начала работы устройства на первом и втором входах блока 2 памяти присутствуют нули, на третьем входе — ноль или единица> на всех выходах блока памяти — нули, Тактовые импульсы, поступающие на регистр 3, производят по каждому импульсу фиксацию нулей в этом регистре, на инфор55 мационных выходах устройства отсутствуют выходные сигналы нулевой выход дешифратора, выполняющего функции формирователя 6 одиночных импульсных сигналов не используется, так как на этом выходе возникает сигнал в то время, когда устройство не работает

Устройство начинает работать после того, как в регистр 1 режима работы будет записан код режима работы !ненулевой), который поступает с выхода регистра 1 на. второй вход блока 2 памяти. В ответ на это на первом — четвертом выходах блока 2 появляется информация: на первом выходе — код слеI дующего состояния, в соответствии с условием, приходящим на третий вход блока 2 памяти), на втором — код выходной статической функции (соответствующей данному режиму, нулевому состоянию алгоритма и внешнему условию, анализируемому в нулевом состоянии,на третьем — все нули, на четвертом — код адреса внешнего условия. После того, как на блок 7 проверки условий подан.код адреса, соответствующее условие с входа 10 коммутируется на выход блока 7 и поступает на третий вход блока 2, если это условие отличается от предыдущего (был "0", а стала " 1" или наоборот), то на первом, втором и третьем выходах блока 2 изменяется. информация.

Информация на четвертом выходе блока 2 не зависит от условия на третьем входе блока 2, По переднему фронту тактового импульса в регистре 3 фиксируется: в поле 4 — код нового состоянии, в поле 5 — код выходной статической функции. Код выходной статической функции с поля 5 поступает на выход 11 устройства. С выхода поля 4 регистра 3 код нового состояния посту. пает на первый вход блока 2, На всех выходах памяти появляется информация, соответствующая новому состоянию и старому условию. После этого, так как изменился код адреса условий, может измениться само условие на третьем входе блока 2 памяти, вследствие чего происходит еще одно переключение выходной информации, содержащей коды следующего состояния, следующей статической функции, нынешнего динамического одиночного сигнала. Код адреса внешнего условия остается прежним не зависит от состояния третьего входа блока 2, На этом переходный процесс в устройстве управления для данного такта заканчивается, После окончания тактового импульса (на входе 9 устройства "0") возбуждается один из выз )3271 ходов формирователя 6, соответствующий коду выходных импульсных сигналов, поступающему с третьего выхода блока 2 памяти на второй вход формирователя 6 выходных одиночных импульсных сигналов. Так функционирует данное устройство управления в первом такте после записи кода режима в регистр 1 режима работы, т.е, в первом такте работы устройства по алгоритму.

Временная диаграмма работы устройства в последующих тактах полностью соответствует описанной выше начиная с переднего фронта тактового импульса.

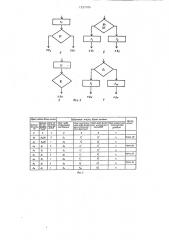

На фиг. 2 приведены примеры фрагментов алгоритмов, которые способно выполнять предлагаемое устройство уп20 равпения. Фрагмент 0 характеризует состояние алгоритма, в котором формируется выходная функция, независящая от условия, и из которого переход возможен в одно из двух других состояний в зивисимости от внешнего условия; во фрагменте Гпереход и функция зависят от внешнего условия; во фрагменте о переход и функция не зависят от внешнего условия; во фрагменте 3 от внешнего условия зависит только функция, 30

На фиг, 3 приведен пример прошивки ПЗУ для фиг, 2.

В ячейках адреса, который содержит пулевой код режима, записаны все нули. Благодаря этому при нулевом коде режима автомат удерживается все время в начальном (уле ) состоянии.

Ячейка, которая выбирается первой по алгоритму, имеет адрес, состоящий из кода режима Ло, приходящего на поле кода режима, кода текущего состояния

40 и равного нулю для начального состояния алгоритма и условия, приходящего на поле кода внешнего условия. Каждому текущему состоянию одного алгоритма соответствуют в блоке 2 памяти две ячейки, отличающиеся адресами.

У одной ячейки адрес содержит ноль в поле кода внешнего условия, а у второй — единицу. Содержимое этих ячеек совпадает полями адреса аналиI зируемого условия, Остальные выходные поля этих ячеек хранят различную информацию, Количество разрядов, отведенных под поле кода режима, определяет число алгоритмов, реализуемых

04 4 устройством управления без смены программы в блоке 2 памяти. Количество разрядов адреса, образующих поле кода текущего состояния, определяет максимальное число состояний алгоритма. Количество разрядов адреса, занимаемых кодом внешнего условия, определяет максимально возможное количество переходов из текуЩего состояния алгоритма в последующие состояния (в рассматриваемом случае поле кода внешнего условия занимает один разряд адреса).

Ф о р м у л а и з обретения

Микропрограммное устройство управления, содержащее блок памяти микрокоманд, мультиплексор логических условий, регистр микрокоманд, причем выход поля адреса регистра микроко манд соединен с первым адресным входом блока памяти микрокоманд, выход поля микроопераций регистра микроко-. манд соединен с первым выходом микроопераций устройства, о т л и ч а ю— щ е е с я тем, что., с целью экономии оборудования, устройство содержит дешифратор, регистр задания режима, причем вход задания режима устройства соединен с информационным входом регистра задания режима, выход которого соединен с вторым адрес ным входом блока памяти микрокоманд, выходы поля адреса и первого поля микроопераций которого соединены со" ответственно с информационными входа ми регистра микрокоманд, выход поля кода логических условий блока памяти микрокоманд соединен с управляющим входом мультиплексора логических условий, выход которого соединен с третьим адресным входом блока памяти микрокоманд, выход второго поля микроопераций которого соединен с информационным входом дешифратора, выход которого соединен с вторым выходом микроопераций устройства, вход синхронизации устройства соединен с вхо- . дом синхронизации регистра микрокоманд и с входом стробирования дешифратора, вход логических условий устройства соединен с информационным входом мультиплексора логических условий, 1327104

l(S1

1327104

&.И.д.

Рби.ад

Еба. МЮ

Рьи. ZbP

Рб!Я. 12

1327 104

Составитель А.Михайлов eõPeÀ Л.Сердюкова Корректор М,Пожо

Редактор Л,Веселовская

Заказ 3390/45

Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, 5-35, Раутнская наб,, д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4