Устройство для анализа случайных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в медицине при обработке сигналов электроэнцефалограмм. Цель изобретения - расширение функциональных возможностей за счет возможности усреднения сигнала по произвольному числу реализаций. Работа устройства основывается на совмещении во времеии режимов накопления, индикации, аналогового и цифрового вывода информа цки, обеспечивая при этом взаимную независимость указанных режимов. Устройство содержит аналого-цифровой преобразователь 1 , ари етико-логнческий блок 2, блок 3 памяти, регистры 4, 14, 15, 16, блок 5 микропрограммного управления, генератор 6 тактовых импульсов, счетчики 7, 11, 12, 13, цифроаналоговые преобразователи 8, 17, 18, демультигшексоры 19 и 20, мультиплексор 21. Устройство позволяет обрабатывать сигналы, устраняя myMt методом усреднения сигнала по ансамблю реализаций 1 з.п. ф-лы, 3 ил. S О)

СОЮЗ СОВЕТСНИХ

COUHAЛИСТИЧЕСНИХ

РЕСПУБЛИН

09) (1И

А1 (51)4 С 06 Р 15/36

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4030894/24-24 (22) 13.12.85 (46) 30.07.87. Бюл. № 28 (71) Московский авиационный институт им. Серго Орджоникидзе (72) О.В.Гурский, С.В.Кузин, Е.А.Кубышкин и В.Н.Алехин (53) 681.3(088.8) (56) Авторское свидетельство СССР

Ф 1049922, кл. G 06 F 15/36, 1983.

Прозоров С.П. Цифровой накопитель повторяющихся сигналов. — Приборы и техника эксперимента, 1984, ¹ 2, с. 97. (54) УСТРОЙСТВО ДЛЯ АНАЛИЗА СЛУЧАЙНЫХ

СИГНАЛОВ (57) Изобретение относится к вычислительной технике и может быть использовано в медицине при обработке сигналов злектроэнцефалограмм. Цель изобретения — расширение функциональных возможностей за счет возможности усреднения сигнала по произвольному числу реализаций. Работа устройства основывается на совмещении во времени режимов накопления, индикации, аналогового и цифрового вывода информации, обеспечивая при этом взаимную независимость указанных режимов. Устройство содержит аналого-цифровой преобразователь 1, арифметика-логический блок 2, блок 3 памяти, регистры 4, 14, 15, 16, блок 5 микропрограммного управления, генератор 6 тактовых импульсов, счетчики 7, ll

12, 13, цифроаналоговые преобразователи 8, 17, 18, демультиплексоры 19 а ф и 20, мультиплексор 21. Устройство позволяет обрабатывать сигналы, устраняя шумы методом усреднения сигнала по ансамблю реализаций, 1 з.п. ф-лы, 3 ил.

1327123

ЗО

36

4Б

БО

Изобретение относится к вычисли3 тельной технике и может быть использовано в системах обработки сигнала, где требуется устранение шумов методом усреднения сигнала по ансамблю реализаций, в частчости в медицине при обработке сигналов злектрознце-.

° фалограмм и электромнограмм.

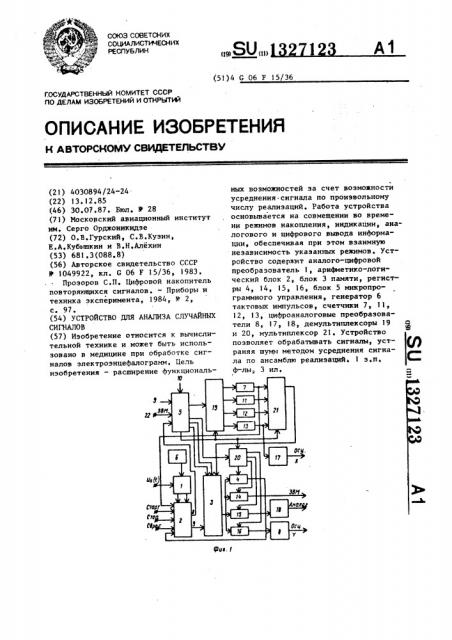

Целью изобретения является расширение функциональных возможностей устройства за счет возможности усреднения сигнала по произвольному числу реализаций, На фиг.l представлена структурная схема устройства; на фнг.2 — схема блока микропрограммного управления;, на фиг.3 — схема арифметнко-логического блока, Устройство для анализа случайньгх сигналов (фиг.l) содержит аналогоцифровой преобразователь (АЦП) 1 арифметика-логический блок 2, блок 3 памяти, второй регистр 4, блок 5 микропрограммного управления„ генератор

6 тактовых импульсов„ счетчик 7, третий цифроаналоговый преобразователь

8, вход 9 команды выдачи аналогового сигнала среднего значения, тактовый вход 10, счетчики 11, 12 и 13 регистры 14, 15..и ° 6, цифроаналоговые. преобразователи 17, 18, демультиплексоры 19, 20, мультиплексор 2!, вход 22 команды выдачи цифрового сигнала среднего значения.

Блок микропрограммного управления (фиг.2) содержит счетчик 23, элемент ИЛИ 24, триггеры 25-32, элементы ИЛИ 33, 34 и 35, блок 36 памяти микропрограмм, Арифметико-логический блок (фнг.3) содержит узел 37 усреднения, счетчик

38„ триггер 39, элементы И 40 41.

Устройство работает следующим образом.

Устройство имеет четыре реь-,има работы: накопления; индикации на экран осциллографа; цифровой вывод на

ЭВМ; аналоговый вывод в растянутом масштабе времени (на самописец или другой медленно действующий регистратор). Режимы включаются сигналами, поступающими на входы блока 5 микро программного управления.

Для указанных режимов работы установлен следующий приоритет: режим накопления обладает высшим приоритетом; режим вывода на ЭВМ; режим аналогового вывода; режим индикации.

Режим индикации включен в течение всего времени„ когда на входах разрядов кода команд блока 5 микропрограммного управления отсутствуют сигналы команд режимов, Если на одном нз указанных входов появился сигнал команды, устройство выполняет команду, а затем возвращается в режим индикации. Зтим обеспечивается постоянное наличие сигнала на экране осциллографа, независимо от частоты переклкчення режимов„ Сигналы на входе кода команд блока 5 микропрограммного управления (БУ) о":"сутствуют. Двухразрядный двоичный код "11 с выхода

БУ поступает на управляющие входы демультнплексоров 19> 20 и мультиплексора 21, в результате чего выходы счетчика соединены с входом блока

3 памяти и входом цифроаналогового преобразователя 17, предназначенного для формирования сигнала горизонтального отклонения луча осциллографа.

Выход регистра 16 подключен к входу цифроаналогового преобразователя (ЦАП) 8, предназначенного для формирования сигнала вертикального отклонения луча осциллографа, Импульсом, поступающим с выхода Бу.на вход разрешения записи регистра 16, информация, находящаяся в блоке 3 памяти по адресу, установленному в счетчике 13, переписывается в регистр 16. Затем на информационный вход счетчика 13 поступает импульс, увеличивающий значение счетчика на единицу. С выхода регистра 16 информация поступает на вход ЦАП 8, формируя ординату очередной выборки. Абсцисса выборки формируется в ЦАП 17, на вход которого подан код адреса выборки. На этом цикл индикации заканчивается БУ.

Режим накопления включается в случае, если на вход первого разряда кода команд БУ поступил сигнал с выхода арифметико-логического блока 2, формируемый иэ сигнала готовности

АЦП в случае, если на вход арифметико-логического блока 2 был подан сигнал запуска устройства, означающий начало обработки очередной реализации.

По сигналу остановки устройства режим накопления останавливается, а сигнал установки в "0" устройства подается, если накопление необходимо начать сначала.

На управляющие входы дешифраторов и мультиплексора в режиме накопления

3 13271 поступает код "00". С помощью импульса генератора 6, поданного на вход запуска АЦП, производится взятие очередной выборки сигнала и преобразова5 ние ее в двоичный код, после чего АЦП выдает сигнал окончания преобразования, поступающий на вход арифметикологического блока. В арифметико-логическом блоке происходит сложение кодов н деление результата на количество реализаций, Окончательный результат с выхода арифметико-логического блока 2 поступает на вход блока 3 памяти. Затем происходит приращение ад- 15 реса в счетчике 7, после чего устройство переходит в режим индикации, по окончании которого цикл заканчивается и блок управления вновь готов к анализу состояний входов. 20

Если на вход BY 5 поступила коианда выдачи цифрового сигнала среднего значения, то информация, находящаяся в блоке 3 памяти по адресу, записанному в счетчик ll переписывается в 25 регистр 14, затеи происходит прира- щение счетчика 11 импульсом, поступающим на его вход с выхода БУ, после чего устройство переходит в режим индикации, по окончании которого цикл Э0 завершается и БУ переходит в исходное состояние.

В режиме аналогового вывода устройство работает так же, как в режиме вывода на ЭВМ.

Блок 5 микропрограммного управления работает следующим образом.

В момент, когда состояние счетчика

23 "000", на выходе элемента ИЛИ 24 появляется логическая единица,.производящая перезапись состояния триггеров 25-28 в триггеры 29-31 с учетои приоритета. После того, как запрос принят одним иэ триггеров 29-32, 45 соответствующий триггер 25-28 сбрасывается для приема нового сигнала.

Блок 36 памяти микропрограмм запрограммирован следующим образом. По адресам "1000-1111" находится программа режима "Накопление", по адресам "1000-10111" — программа режииа работы с ЭВМ, по адресам "100000100111" — программа режима выдачи . аналоговой информации, по адресам

"100000-1000111" — программа режима индикации. Импульс запроса режима индикации записан по последнему адресу программы каждого режима.

23

В арнфметико-логическом блоке элемент И 41 анализирует состояния выходов счетчика 38 ° На его выходе появляется сигнал логической единицы в том случае, когда во всех разрядах счетчика 38 записаны единицы.

Это означает, что очередная реализация обработана, н в этот момент происходит остановка режима накопления и прекращение работы блока 2. Для обработки следующей реализации на вход запуска устройства должен быть подан импульс. На вход узла 37 усреднения кроме кода количества реализаций подаются коды с выхода АЦП и выхода блока памяти. Узел 37 усреднения производит сложение кодов с выходов АЦП и блока памяти и деление суммы на код количества реализаций.

Результат поступает на вход блока

3 памяти.

Формула изобретения

1. Устройство для ачалиэа случайных сигналов,, содержащее аналогоцифровой преобразователь,.арифметикологический блок, блок памяти, первый регистр, счетчик, цифроаналоговый преобразователь, блок микропрограммного управления, генератор тактовых импульсов, вход аналого-цифрового преобразователя является информационным входом устройства, выход генератора тактовых импульсов соединен с входом запуска аналого-цифрового преобразователя, выход окончания преобразования которого соединен с входом разрешения анализа сигнала арифметикологического блока, информационный выход аналого-цифрового преобразователя соединен с информационным входом арифметико-логического блока, информационный выход которого соединен с ннформационныи входои блока памяти, выход которого соединен с информационным входом первого регистра, выход которого соединен с входом первого цифроаналогового преобразователя, выход которого является выходом аналогоного сигнала среднего значения ус1ройства, тактовый вход блока иикропрограммного. управления является так, товым входом устройства, первый выход группы блока микропрограммного управления соединен с входом разрешения записи блока памяти, о т л и ч а ющ е е с я тем, что, с целью расам123

5 1З27 рения функциональных воэможностей устройства за счет возможности усреднения сигнала по произвольному числу реализаций, в него введены два демультиплексора, три счетчика., мультиплексор, три регистра, два цифроаналоговых преобразователя, причем арифметика-логический блок содержит триггер, счетчик, два элемента И, . узел усреднения, в арифметика-логи- >0 ческом блоке первый вход первого элемента И является входом разрешения . анализа сигнала блока, информационный вход узла усреднения является информацнОнным ВхОДОИ блока ВхОДы установки в "1" и в "0" триггера являются входом запуска и входом останова устройства соответственно, вход установки в "0" счетчика является входом установки в "0" устройства, вход среднего 20 значения накопленных данных узла усреднения соединен с выходом второго регистра, входы второго элемента И соединены с соответствующими разрядными выходами первого счетчика, входы установки s "0" триггера и информационный вход счетчика соединены с выходам второго элемента И, Выход счетчика соединен с входом значения количества выборок узла усреднения„ .@ выход которого является информационным выходом арифметика-логического блока, выход триггера соединен с вторым входом первого элемента И, выход которого соединен с входом первого 35 разряда кода команды блока микропрограммного управления, с первого по четвертый выходы первого демультиплексора соединены со счетными входами одноименных счетчиков, выходы которых соединены с соответствующими входами мультиплексора, выход которого соединен с адресными входами младших разрядов блока памяти, выход которого соединен с информационными входами с второго по четвертый регистров, выход третьего регистра является выходом цифрового сигнала среднего значения устройства, выход четвертого счетчика соединен с входом второго 5@

f цифроаналогового преобразователя, выход которого является выходом аналогового сигнала ординаты устройства, выход четвертого регистра соединен с входом третьего щ фроаналогавого пре55 образователя, выход которого является выходом аналогового сигнала абсциссы устройства, с первого по четвертый вы" ходы Второго демультиплексара соединены с входами разрешения записи одноименных регистров, вход команды вьщачи аналогового сигнала среднего значения и вход команды выдачи цифрового сигнала среднего значения блока микропрограммного управления являются соответственно одноименными входами устройства, с второго по шестой выхады группы блока микропрограммного управления соединены соответственна с первым и вторым разрядными информационными входами первого демультиплексора, с управляющими входами первого, второго демультиплексоров и мультиплексора, с адресными входами старших разрядов блока памяти, с информационным входам второго демультиплексора.

2. Устройство по п.l, о т л и— ч а ю щ е е с я тем, что блок микропрограммного управления содержит счетчик, четыре элемента ИЛИ, восемь триггеров, блок памяти микропрограмм, причем вход счетчика является тактовым входом блока, выходы первого, второго и третьего-разрядов счетчика соединены с одноименными входами первого элемента ИЛИ и одноименными разрядными входами блока памяти .Микропрограмм, вход установки в "1" первого триггера является входом первого разряда кода команды блока, вход установки в "1" второго триггера является входам второго разряда кода команды блока, вход установки в "1" третьего триггера является входом третьего разряда кода команды блока, выходы с первого по четвертый триггеров соединены с входами установки в "1" с пятого па восьмой триггеров соответственно, выходы с пятого по восьмой триггеров соединены с входами установки в "0" с первого по четвертый триггеров соответственно, входы разрешения записи с пятого по восьмой триггеров соединены с выходом первого элемента ИЛИ, первые входы с второго па четвертьй элементов ИЛИ соединены с выходом пятого триггера, вторые входы с второго по четвертый элементов ИЛИ и вход установки в "0" пятого триггера соединены с адресным выходом поля микраопераций блока памяти микропрограмм, .третьи входы третьего и четвертого элементов ИЛИ соединены с выходом шестого триггера, Составитель В.Орлов

Техред И.Попович Корректор A. Тяско

Редактор М.Бандура

Заказ 3391/46 Тирал(672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ултород, ул. Проектная, 4

7 13 четвертый вход четвертого элемента

ЮЧИ соединен с выходом седьмого триггера, выходы с второго по четвертый элементов ИЛИ соединены с входами установки в "0" с шестого по восьмой триггеров соответственно, выходы с пятого по восьмой триггеров соедине27123 8 ны с четвертого по седьмой адресными входами блока памяти микропрограмм соответственно, с первого по шестой выходы поля микроопераций группы 5 блока памяти микропрограмм являются соответственно с первого по шестой выходами блока.