Запоминающее устройство с одновременной выборкой информации из нескольких ячеек

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой автоматике и может быть использовано при запоминании наборов двоичных единиц информации (битов), когда соответствующие биты одновременно выбираемых ячеек запоминающего устройства (ЗУ) собираются при считывании по схеме ИЛИ. Цель изобретения - упрощение устройства. Устройство содержит &if

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) (51) 4 G 11 С 11/00

ГОСУДА СТВЕННЫЙ КОМИТЕТ CCCP

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3965506/24-24 (22) 16, 10 . 85 (46) 30.07,87. Бюл. У 28 (72) Е.И,Николаев, В.П.Раев, Е,З.Храпко, С,A.Øàêèí и В.И.Шпаков (53) 681.327.6 (088.8) (56) Авторское свидетельство СССР

11 993268, кл. G 11 С 17/00, 1981.

Полупроводниковые запоминающие устройства и их применение/ Под ред.

А.Ю.Гордонова. М.: Радио и связь, 1981, с.135-138, рис.3.24, 3.27. (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОДНОВРЕМЕННОЙ ВЫБОРКОЙ ИНФОРМАЦИИ ИЗ НЕСКОЛЬКИХ ЯЧЕЕК (57) Изобретение относится к цифровой автоматике и может быть использовано при запоминании наборов двоичных единиц информации (битов), когда соответствующие биты одновременно выбираемых ячеек запоминающего устройства (ЗУ) собираются при считывании по схеме ИЛИ. Цель изобретения — упрощение устройства. Устройство содержит

1327 генератор 3, счетчик 4, дешифратор 5, группу формирователей 6 импульсов, мультиплексоры 7 и 8, накопитель 9, группу элементов И 10, группу одновибраторов 1 1, Сущность из об ре тения заключается в уменьшении числа одинаковых

182

ЗУ в устройстве до одного. В устройстве производится одновременная параллельная выббрка информации с поочередной обработкой входных адресных сигналов и сигналов разрешения считывания. 4 ил.

Изобретение относится к цифровой автоматике и может быть использовано при запоминании наборов двоичных единиц информации (битов), когда соответствующие биты одновременно выбираемых ячеек запоминающего устройства (ЗУ) собираются при считывании по схеме ИЛИ.

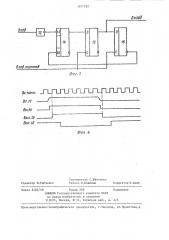

Цель изобретения - упрощение уст.Ройства, На фиг.I представлена структурная схема устройства, на фиг.2 — временная диаграмма, поясняющая его работу, на фиг,3 — вариант выполнения формирователя импульсов, на фиг.4 — временная диаграмма его работы.

Устройство содержит адресные входы 1, входы 2 разрешения, генератор

3, счетчик 4, дешифратор 5, группу формирователей 6 импульсов, мультиплексоры 7 и 8, накопитель 9, группу элементов И 10, группу одновибраторов 11 и информационные выходы 12.

Временная диаграмма устройства (фиг.2) составлена для случая применения накопителя с четырьмя адресными входами. Она содержит последовательность тактовых импульсов Г на . выходе генератора 1, сигналы СТ1 и

СТ2 на выходе счетчика 5, тактовые импульсы ТО...ТЗ на выходе дешифратора 5 (выходные сигналы разрешающих дешифраторов внутри мультиплексоров

7 и 8), сигналы разрешения считывания СО...C3 на выходах формирователей.б, привязанные своими передними и задними фронтами к передним фронтам соответственно импульсов ТО ° ..ТЗ, сигналы MO...МЗ на фоне помех с выходов .ячеек накопителя 9, сигналы

МГО...МГЗ на выходах элементов И 10, сигналы ФО...ФЗ на выходах одновибраторов 11 после воздействия на их входы соответственно сигналов МГО..

МГЗ.

Формирователь импульсов (фиг, 3) содержит генератор 13 и триггеры 1416.

Устройство работает следующим об2 PG3OM

Генератор 3 вырабатывает последовательность тактовых импульсов Г (фиг.2), поступающих на счетный вход счетчика 4, Информационные сигналы

СТ1 и СТ2 с выхода счетчика 4 поступают на дешифратор 5 и управляющие входы мультиплексоров 7 и 8. Дешифратор 5 формирует четыре последовательности тактовых сигналов ТО...T3, сдвинутые один относительно другого на один период импульсов Г. Сигналы

ТО...ТЗ поступают на четыре тактовых входа формирователей 6.

Каждый формирователь 6 (фиг.3) осуществляет привязку переднего и заднего фронтов разрешающего сигнала к передним фронтам тактовых импульсов с помощьн> инвертора 13 и трех триггеров: фиксирующего 14, формирующего 15 и буферного 16 (фиг.4).

Сигналы СТ1 и СТ2, управляющие работой мультиплексоров 7 и 8, формируют на выходе их внутренних дешифраторов стробируюшие сигналы ТО...ТЗ, которые поочередно опрашивают четыре разрешающих сигнала, поступающих соответственно на вхоць| 1 и 2, и как бы "дробят" их. Подобное "дробление" позволяет считывать несколько ячеек

35 с адресами АО...АЗ в накопителе 9 даже при одновременном появлении нескольких сигналов разрешения считывания.

40 На выходах ячеек накопителя 9 ин-. формация имеет "раздробленный" вид

МО...МЗ на фоне помех. С целью ее восстановления сигналами МО. МЗ сначала стробируются на элементах И 10

45 импульсами Г для устранения помех, 82

СТ!

СТЯ

ТО

Т!

ТЯ

ТЗ

Cl

СЛ

СЯ

3 13271 а затем запускают полученными сигналами МГО...МГЗ одновибраторы 11.

При запуске каждого одновибратора 11 íà его выходе образуется импульс с длительностью, превышающей на 10207. период сигналов ТО...ТЗ. В результате "раздробленная" информация восстанавливается и принимает вид

ФО...ФЗ, соответствующий первоначальным сигналам разрешения считывания 10

СО...СЗ.

Формула изобретения

Запоминающее устройство с одновременной выборкой информации из не- 15 скольких ячеек, содержащее накопитель, адресные входы которого подключены к выходам мультиплексора адресов, информационные входы которого являются адресными входами устройства, генера-2р тор, выход которого подключен к входу счетчика, дешифратор, группу элементов И, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит группу формирователей импульсов, группу одновибраторов, и мультиплексор сигналов разрешения, выход и информационные входы которорого подключены соответственно к входу разрешения накопителя и к выходам формирователей импульсов группы, первые входы которых являются входами разрешения устройства, вторые входы формирователей импульсов группы подключены к выходам дешифратора, входы которого подключены к выходам счетчика и управляющим входам мультиплексора адресов и мультиплексора сигналов разрешения, выходы накопителя подключены к первым входам элементов И группы, вторые входы которых подключены к выходу генератора, выходы элементов И группы подключены к входам одновибраторов группы, выходы которых являются информационными выходами устройства.

1327182 фЦЯ, ) Составитель С.Шустенко

Техред Л.Олийнык

Редактор И.Рыбченко

Корректор Т.Колб

Тираж 589

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Заказ 3404/49

Подписное

Производственно-полиграфическое предприятие, г.ужгород, ул,Проектная,4