Устройство для управления 2 @ -ячейковым преобразователем напряжения

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике и может использоваться в импульсных стабилизаторах, усилителях мощности. Целью изобретения является повышение точности и быстродействия. В данном устройстве поля разверток и тактовые интервалы преобразовательных ячеек сдвинуты по фазе на угол 1/2. Это позволяет при суммировании напряжений ячеек реализовать на нагрузке преобразователя многозонную модуляцию . Нулевые паузы симметрично размещаются в интервале полупериода тактовой частоты и не накладываются друг на друга, что позволяет увеличить точность преобразования. 3 ил. с (Л 00 ю sj КС ел

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (so 4 Н 02 М 5/48

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4029238/24-07 (22) 28.02.86 .(46) 30. 07.87. Бюп. Р 28 (71) Научно-исследовательский институт автоматики и электромеханики при

Томском институте автоматизированных систем управления и радиоэлектроники (72) Н.М.Музыченко и А.В.Шарапов (53) 621.316;727 (088.8) (56) Тараскин А.В. Многозонная многофазная модуляция и ее особенности.

В кн.: Электромеханические и электрические системы и устройства автоматизации технологических процессов, Томск: Изд-во ТГУ, 1981, с.91-93.

Авторское свидетельство СССР

9 1051685, кл. Н 02 P 13/16, 1982.

„„Я0„„1327250 А 1 (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ 2"

ЯЧЕЙКОВЫМ ПРЕОБРАЗОВАТЕЛЕМ НАПРЯЖЕНИЯ (57) Изобретение относится к электротехнике и может использоваться в импульсных стабилизаторах, усилителях мощности, Целью изобретения является повьнпение точности и быстродействия.

В данном устройстве поля разверток и тактовые интервалы преобразовательных ячеек сдвинуты по фазе на угол

li/2 . Это позволяет при суммировании напряжений ячеек реализовать на нагрузке преобразователя многозонную модуляцию. Нулевые паузы симметрично размещаются в интервале полупериода тактовой частоты и не накладываются друг на друга, что позволяет увеличить точность преобразования. 3 ил.

1327250

Изобретение относится к электротехнике, в частности к преобразованию и регулированию переменного и постоянного напряжений, и может найс. ти применение в многофазных импульсНых стабилизаторах, амплитудных модуляторах, усилителях мощности„системах электропитания аппаратуры средств связи и радиоэлектроники. 10

Цель изобретения — повышение точности и быстродействия устройства.

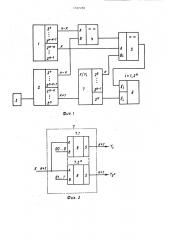

На фиг. 1 приведена функциональная схема устройства; на фиг.2 — блок сумматоров; на фиг. 3 — схема ячейки 15 преобразователя.

Устройство для управления 2 ячейковым преобразователем напряжения (фиг.l) содержит п-разрядный формирователь l кода управления и (n+l)-раэ- 20 рядный двоичный счетчик 2, счетный вход которого подключен к генератору

3 импульсов. Выходы младших (и-К) разрядов формирователя 1 и двоичного счетчика 2 подключены к входам сравнения (n-К) -разрядного цифрового компаратора 4, выход переноса которого подключен к входам переноса блока 5 из 2 К-разрядных цифровых компараК торов, выходы которых предназначены ЗО для подключения через логический узел к управляющим входам преобразовательных ячеек 6. Выходы старших (К+1) разрядов двоичного счетчика 2 подключены к входам блока 7 из 2" сумматоров (К+1)-разрядного кода, выходы старшего разряда которых предназначены для подключения через логический узел к управляющим входам преобразователей ячеек 6. Первые вхо- 4g ды сравнения цифровых компараторов

5 подключены к выходам старших К разрядов формирователя 1, вторые входы сравнения — к выходам младших

К разрядов кода 7.

Блок 7 (фиг.2) содержит 2 (К+1)разрядных двоичных сумматоров 8, первые суммирующие входы которых образуют входы блока, вторые суммирующие входы предназначены для подачи уров- 50 ней, соответствующих (К+1)-разрядному двоичному коду чисел от 0 до 2 -1

К (00 ... Оу 00. ° . 1, 01... 1) . Выходы сумматоров 8 (Y„..., Y Y «) образуют выходы блока 7. 55

Логический узел состоит из элементов И 9 и 10, подключенных к ключам преобразователя, состоящего из ключей 11 — 14 и элемента НЕ 15.

Запись i = 1,2" (фиг,1) означает, сс что i пробегает значения от 1 до 2 с шагом

При аналоговом сигнале управления U (фиг,l) формирователь кода управления может быть выполнен в виде АЦП, тактовый вход которого подключен к генератору 3.

Принцип работы устройства состоит в следующем.

Каждый из К-разрядных цифровых компараторов блока 5 совместно с (и-k)-разрядным цифровым компаратором 4 образует и-разрядный цифровой компаратор, формирующий ШИМ-сигнал управления i-й ячейки 6 в результате сравнения кода управления с кодом развертки i-ro канала.

Для первого канала код развертки формируется на выходах младших и разрядов счетчика 2, а тактовый сигнал формируется на выходе старшего разряда счетчика 2 (сумматор 8 блока .7 первого канала повторяет код старших (К+l) разрядов счетчика 2 и может быть исключен). Полупериод тактовой частоты преобразователя

П составляет 2 периодов колебаний генератора 3.

Код развертки и тактовый сигнал для i-го канала формируются путем сдвига по фазе выходных сигналов счетчика 2 на величину, равную

i-1 (-- †-) полупериода напряжения так2

К товой частоты. Для 2 ячейкового преобразователя такой сдвиг может быть осуществлен путем добавления к коду счетчика 2 двоичного кода числа,рав2 (i — 1) -К ного или 2 (i-1) с

2 игнорированием результата суммы в (n+2)-м разряде. При этом во всех каналах коды развертки младших (и-К) разрядов совпадают, что позволяет в каче стве их ис поль зов ать выходы младших (п-К) разрядов двоичного счетчика 2, а сравнение этих сигналов с соответствующими разрядами кода управления осуществить в общем цифровом компараторе 4.

Преобразование кода старших (К+1) разрядов счетчика осуществляется в каждом канале с помощью сумматора 8 (фиг.2) путем суммирования этого кода с кодом числа i-1. На выходе суммы (К+1) разряда формируется такто1327250 вый сигнал i-й ячейки,а на выходах младших К разрядов сумматора 8 — код старших К разрядов развертки, который сравнивается в цифровых компараторах блока 5 со старшими разрядами кода управления. При серийном производстве блок 7 сумматоров S можно выполнить на микросхеме ПЗУ, для программирования которой используются выходные сигналы блока 7, реализованного на сумматорах (фиг.2).

Функции формирователя 1 кода управления может выполнять АЦП, тактирование работы которого удобно производить от генератора 3.

Таким образом, поля разверток и тактовые интервалы преобразовательных ячеек сдвинуты по фазе на угол

К

)(/2, что позволяет при суммировании напряжений ячеек реализовать на нагрузке преобразователя многозонную многофазную модуляцию. Выходной сигнал формируется в 2 зонах и имеет к по сравнению с одноканальной ШИИ в к

2 раз меньший уровень пульсаций и в 2к раз большую их частоту. Нулевые паузы симметрично размещаются в интервале полупериода тактовой частоты и не накладываются друг на друга,что позволяет увеличить точность преобра— зования по сравнению с прототипом.

Предлагаемое устройство позволит выполнить условия, равноценные увелиК чению в 2 раз тактовой частоты преобразователя, а в прототипе — лишь в 2 раза. Следовательно, при одинаковой тактовой частоте быстродействие преобразователя может быть увелик-1 чена в 2 раз по сравнению с прототипом. Кроме того, устройство обеспечивает высокую надежность и помехоустойчивость, серийнопригодность.

10 двух элементов И, выходы которых ды,, соответствующие номеру (К+1)-раз50 рядного сумматора в блоке из 2" (К+1) -разрядных сумматоров.

Формула изобретения

Устройство для управления 2 ячейковым преобразователем напряжения, каждая ячейка которого представляет собой мостовую ключевую схему с анодной и катодной группами ключей, со15

45 держащее п-разрядный формирователь кода управления, вход которого предназначен для подключения к источнику сигнала управления, генератор импульсов, выход которого соединен с (и+1)разрядным двоичным счетчиком, логический узел по числу ячеек преобразователя, состоящий иэ элемента НЕ и предназначены для подключения к управляющим входам одной группы ключей, вход и выход элемента HE подключены к первым входам элементов И и предназначены для подключения к управляющим входам другой группы ключей, вторые входы элементов И объединены, отличающее с я тем, что, с целью повышения точности и быстродействия управления, оно снабжено (n-К)-разрядным цифровым компараток ром, блоком из 2 К-разрядных цифрок вых компараторов, блоком из 2 (К+1)разрядных сумматоров, причем первые (n-К) разрядов и-разрядного формирователя кода управления и (n+1)-разрядного двоичного счетчика соединены с первым и вторым входами (n-К)-разрядного цифрового компаратора, выход которого соединен с входами переноса всех К-разрядных цифровых компараторов, первые информационные входы которых объединены и соединены с последними К разрядами и-разрядного формирователя кода управления, а вторые информационные входы соединены с младшими К разрядами выходов блока из

2 (К+1)-разрядных сумматоров, (К+1)-е разряды которых соединены с входами соответствующих элементов НЕ, первые входы всех (К+1)-разрядных сумматоров объединены и подключены к (К+1) последним выходным разрядам (п+!)-разрядного двоичного счетчика, выходы блока к из 2 К-разрядных компараторов подключены к вторым входам соответствую" щих элементов И, на вторые входы (К+1)-разрядных сумматоров поданы ко1327250

1327250

Составитель С.Лузанов

Техред Л. Олийнык

Корректор A. Зимокосов

Редактор М.Дыпын

Заказ 3406/53

Тираж 659

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Подписное

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная, 4