Статистический анализатор конечной разности фазы

Иллюстрации

Показать всеРеферат

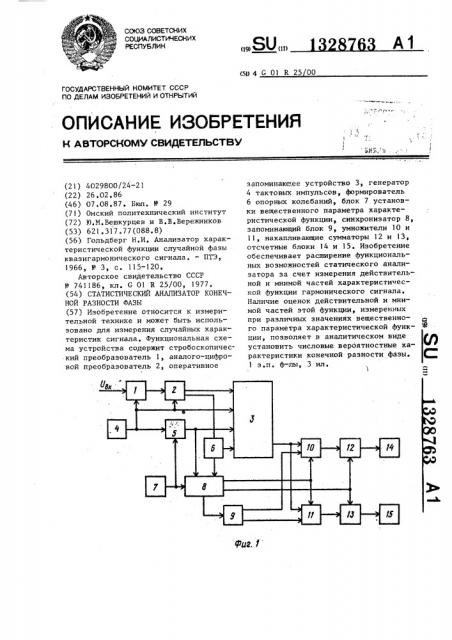

Изобретение относится к измерительной технике и может быть использовано для измерения случайных характеристик сигнала. Функциональная схема устройства содержит стробоскопический преобразователь 1, аналого-цифровой преобразователь 2, оперативное запоминающее устройство 3, генератор 4 тактовых импульсов, формирователь 6 опорных колебаний, блок 7 установки вещественного параметра характеристической функции, синхронизатор 8, запоминаюпщй блок 9, умножители 10 и II, накапливающие сумматоры 12 и 13, отсчетные блоки 14 и 15. Изобретение обеспечивает расширение функциональных возможностей статического анализатора за счет измерения действительной и мнимой частей характеристической функции гармонического сигнала. Наличие оценок действительной и мнимой частей этой функции, измеренных при различных значениях вещественного параметра характеристической функции , позволяет в аналитическом виде установить числовые вероятностные характеристики конечной разности фазы. 1 з.п. ф-лы, 3 ил. I (Л с «г /

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (11) (5D 4 G 01 R 25 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCH0MV СВИДЕТЕЛЬСТВУ

Фиг. 1

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4029800/24-21 (22) 26.02.86 (46) 07.08.87. Бюл. № 29 (71) Омский политехнический институт (72) Ю.N.Вешкурцев и В.В.Вережников (53) 621.317.77(088.8) (56). Гольдберг Н.И. Анализатор характеристической функции случайной фазы кваэигармонического сигнала. — ПТЗ, 1966, ¹ 3 с. 115-120.

Авторское свидетельство СССР

¹ 741186, кл. G 01 R 25/00, 1977. (54) СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР КОНЕЧНОЙ РАЗНОСТИ ФАЗЫ (57) Изобретение относится к измерительной технике и может быть использовано для измерения случайных характеристик сигнала. Функциональная схема устройства содержит стробоскопический преобразователь 1, аналого-цифровой преобразователь 2, оперативное запоминающее устройство 3, генератор

4 тактовых импульсов, формирователь

6 опорных колебаний, блок 7 установки вemeственного параметра характеристической функции, синхронизатор 8, запоминающий блок 9, умножители 10 и

1!, накапливающие сумматоры 12 и 13, отсчетные блоки 14 и 15. Изобретение обеспечивает расширение функциональных возможностей статического анализатора за счет измерения действительной и мнимой частей характеристической функции гармонического сигнала.

Наличие оценок действительной и мнимой частей этой функции, измеренных при различных значениях вещественного параметра характеристической функции, позволяет в аналитическом виде установить числовые вероятностные характеристики конечной разности фазы.

1 з.п. ф-лы, 3 ил.

8763 2

ЭО

1 132

Изобретение относится к измерительной технике и может быть использовано для измерения случайных характеристик сигнала.

Цель изобретения — расширение функциональных возможностей анализатора за счет обеспечения возможности измерения действительной и мнимой частей характеристической функции гармонического сигнала, На фиг.1 представлена структурная блок-схема статистического анализатора; на фиг.2 — структура оперативного запоминающего блока; на фиг.3 —временные диаграммы, поясняющие работу элементов устройства.

Статистический анализатор конечной разности фазы содержит стробоскопический преобразователь 1, первый вход которого соединен с входом всего устройства, соединенный через аналого-цифровой преобразователь 2 (АЦП) с первым входом оперативного запоминающего блока 3, второй вход которого соединен с вторыми входами стробоскопического преобразователя 1, аналого-цифрового преобразователя 2 с выходом генератора 4 тактовых импульсов и входом управляемого умножителя

5 частоты, выход которого соединен с третьим входом оперативного запоминающего блока 3, четвертый вход которого соединен с выходом формирователя 6 опорного колебания. Блок 7 установки вещественного параметра характеристической функции через синхроблок 8 соединен с входом постоянного запоминающего блока 9.. Второй выход синхроблока 8 соединен с входами умножителей 10 и 11, а третий его выход соединен с входами управления накапливающих сумматоров 12 и 13, выходы которых соединены соответственно с первым 14 и вторым 15 о гсчетными блоками. Кроме того, второй выход аналого-цифрового преобразователя 2 чеpcs формирователь 6 опорного колебания соединен с первым входом синхроблока 8, второй вход которого соеди- нен с третьим входом оперативного запоминающего блока 3, выход которого соединен с первыми входами первого

10 и второго 11 умножителей, выходы которых соединены соответственно с первым 12 и вторым 13.накапливающими сумматорами,. а первый и второй выходы постоянного запоминающего блока 9

Ф соединены соответственно с вторыми входами первого 10 и второго 11 управляемых умножителей. Оперативный запоминающий блок 3 содержит дна запоминающих блока 16 и 17, первый счетчик 18, первый элемент 19 задержки, второй счетчик 20, второй элемент 21 задержки, триггер 22, первый

23, второй 24, третий 25, четвертый

26 элементы И и первый 27 и второй 28 элементы ИЛИ.

При этом первый вход оперативного запоминающего блока 3 соединен с информационными входами запоминающих блоков 16 и 7, выходы которых соединены с соответствующими его выходами. Адресные входы первого

16 и нторого 17 запоминающих блоков соединены с первым 18 и,нторым 20 счетчиками. Второй вход блока 3 соединены со счетным входом триггера 22, прямой выход которого соединен с перными входами первого 23 и треть его

25 элементов И и первыми входами второго запоминающего блока 17 и второго счетчика 20. Инверсный выход триггера

22 соединен с первыми входами первого запоминающего блока 16 и первого счетчика 18 и первыми входами второго 24 и четвертого 26 элементов И, выходы первого 23 и четвертого 26 элементов И через первый элемент ИЛИ

27 соединен с вторым входом первого счетчика 18 и через первый элемент

19 задержки с третьим входом парного запоминающего блока 16. Выходы второго 24 и третьего 25 элементов И соединены через второй элемент 28 с вторым входом второго счетчика 20 и через второй элемент 21 задержки — с третьим входом второго запоминающего блока 17.

Третий вход блока 3 соединен с вторыми входами первого 23 и второго 24 элементов И, а четвертый вход блока

3 соединен с вторыми входами третьего

25 и четвертого 26 элементов И.

Статистический анализатор ко..ечной разности фазы работает " ег..ющим образом.

В исходном состоянии все блоки устройства обнулены. Исследуемый сигнал U cos (и t + q (t)) поступает на вход стробоскопического преобразователя 1 и с помощью АЦП 2 и генератора 4 тактовых импульсов преобразуется в последовательность цифровых кодов (фиг ° 3 a ««b ««ь) 3 132

Измерение оценок характеристической функции производится поэтапно, причем номер этапа численно равен значению вещественного параметра.

На M-ом этапе измерения производится измерение оценок характеристической функции при значении вещественного параметра Б = М. При этом с помощью установочного переключателя $ блока 7 установки вещественного параметра устанавливают коэффициенты умножения управляемых умножителей частоты соответственно равными MM u

NP.

Сигнал с выхода знакового разряда

АЦП 2 поступает на вход формирователя 6 импульсов, который формирует на своем выходе импульс в момент смены потенциала с высокого на низкий (фиг.3 г 1. Импульсы с выхода формирователя 6 импульсов формируют опорный (фи..З а >.

Импульс с выхода формирователя 6 импульсов поступает на второй вход блока 3 и устанавливает триггер 22 в состояние (фиг.3 е, ж ), при котором на прямом выходе триггера 22 устанавливается потенциал логической "1".

Задний фронт импульса с инверсного выхода триггера 22 сбрасывает счетчик 18 в нулевое состояние. Потенциал инверсного выхода триггера 22 устанавливает блок 16 по первому входу в режим "Запись", а потенциал прямого выхода триггера 22 с помощью логических элементов И и ИЛИ 23 и 27 разрешает прохождение импульсов с выхода генератора 4 на второй вход счет. чика 18. Цифровые коды с выхода АЦП

2 поступают на второй вход блока 16.

Импульс, появившийся на втором входе счетчика 18, формирует с его помощью адрес для блока 16 и, после того как адрес сформирован, через элемент 19 задержки формирует сигнал выборки для блока 16. Иким образом, в течение интервала времени, равного периоду исследуемого сигнала, т.е, пока на прямом выходе триггера 22 присутствует потенциал логической "1", счетчик

18 производит суммирование поступающих на его второй вход импульсов с выхода генератора 4 тактовых импульсов и формирует коды адреса для блока 16 для записи кажцого цифрового кода, поступающего с выхода АЦП 2.

Следующий импульс с выхода формирователя 6 импульсов (фиг.3 z, ) соот8763

4 ветствует началу следующего периода исследуемого сигнала и устанавливает прямой выход триггера 22 в нулевое состояние. Передний фронт импульса с инверсного выхода триггера 22 устанавливает цикл счета счетчика 18 численно равным количеству импульсов с выхода генератора 4 тактовых импульсов, поступивших в счетчик 18 за вреся, в течение которого на прямом выходе триггера 22 был установлен потенциал логической "1". Задний фронт импульса с прямого выхода триггера

22 обнуляет счетчик 20, а его потенциал устанавливает блок 17 по первому входу в режим "Запись". Потенциал инверсного выхода триггера 22 с помощью логических элементов И и ИЛИ 24 и 28 разрешает прохождение импульсов с выхода генератора 4 тактовых импульсов на второй вход счетчика 20 ° Импульс, появившийся на втором входе счетчика 20, формирует с его помощью

25 адрес для блока 17, и после того, как адрес сформирован, через элемент

21 задержки формирует сигнал выборки для блока 17. Таким образом, в течение следующего периода исследуемо30 го сигнала, т.е. пока на прямом выходе триггера 22 присутствует потенциал логического "0", счетчик 20 производит суммирование поступающих на его второй вход импульсов с выхода генератора 4 тактовых импульсов и

35 формирует коды адреса для блока 17 для записи в него каждого цифрового ,кода, поступающего с выхода АЦП 2.

В то же самое время, когда прямой

40 выход триггера 22 устанавливается в нулевое состояние, инверсный выход триггера 22 устанавливает блок 16 в режим "считывание" и разрешает прохождение импульсов с выхода управ45 ляемого умножителя 5 частоты на второй вход счетчика 18, цикл счета которого установлен передним фронтом импульса с инверсного выхода триггера

22. Счетчик 18 осуществляет счет им50 пульсов с выхода управляемого умножителя 5 частоты, частота которых в

М раз больше, чем частота генератора

4 тактовых импульсов, и формирует коды адреса для блока 16. Элемент 19

55 задержки формирует на своем выходе сигнал выборки для блока 16. За время второго периода исследуемого сигнала, т.е. пока на прямом выходе триггера

22 установлен потенциал логического

13?8763

"0", иэ блока 16 производится считы вание цифровых кодов циклично М раэ, С началом следующего периода исследуемого сигнала триггер 22 вновь устанавливается в состояние, при котором на прямом выходе триггера 22 присутствует потенциал логической

"1". При этом описанные процессы повторяются. В дополнение к этому прямой выход триггера 22 устанавливает 10 блок 17 в режим "Считывание" и с помощью логических элементов 25 и 28 разрепает прохождение импульсов с выхода управляемого умножителя 5 частоты на второй вход счетчика ?О, цикл счета которого установлен передним фронтом импульса с прямого выхода триггера 22. Счетчик 20 осуществляет счет импульсов с выхода управляемого умножителя 5 частоты и формирует ко- 20 ды адреса для блока 17 ° С помощью элемента 21 задержки формируется сигнал выборки для блока 17. Цифровые коды из блока 17 считываются циклично М раз.

С началом очередного периода исследуемого сигнала триггер устанавливается в состояние, при котором на прямом выходе триггера. 22 присутствует потенциал логического "0".

Такой процесс попеременной записи цифровых кодов в блоки 16 и 17 и попеременного считывания. цифровых кодов из блоков 16 и 17 производится в течение всего М-го этапа. измерения. 35

Таким образом, с выхода блока 3 на о первые входы перемножителей 10 и 11 подается последовательность цифровых кодов, сформированных из сигнала U cosjQt + Q(t)$ в виде

UcosM(yt+q(t)J =U co s (Mut+M q(t)J .

Считанные из блока 3 цифровые коды подаются на первые входы перемножителей 10 и 11, на вторые входы которых подаются коды чисел, формируе45 мых в блоке 9 и пропорциональных значениям тригонометрических функций в точках деления периода опорного сигнала на Р частей. Выборка цифровых кодов иэ блока 9 осуществляется им50 пульсами с первого выхода синхроблока 8, которые делят период опорного сигнала на P частей (фиг.3 к ). Таким образом, на первых входах умножителей 10 и 11 информация постоянно сме55 няется, а перемножение производится в моменты времени, когда появляются цифровые коды с выхода блока 9, Для IIB ремножения цифровых кодов в эти моменты времени синхроблок 8 формирует управляющие сигналы. Накапливающие сумматоры накапливают произведение цифровых кодов за время M-го этапа измерения и усредняют их по его окончании. После усреднения на выходах цифровых отсчетных блоков 14 и 15 получаются оценки действительной и мнимой частей характеристической функции в виде

МИ1

А(М) = — —.-- 2 х cos М у p t;

М.N:P миГ

}3(M) = — — —.— х sin Mtvdt, M N Ð где х. — коды мгновенных значений ис1 следуемого сигнала;

f2 — частота исследуемого сигнала;

N — количество периодов исследуамого сигнала, укладывающихся в длительность М-го этапа измерения;

М вЂ” коэффициент, численно равный установленному значению вещественного параметра характеристической функции Uz;

Т/Р где Т вЂ” период исследуемого сигнала.

Наличие оценок действительной и мнимой частей характеристической функции, измеренных при различных значениях вещественного параметра U характеристической функции, позволяет в аналитическом виде установить числовые вероятностные характеристики конечной разности фазы.

Формула изобретения

I. Статистический анализатор конечной разности фазы, содержащий две параллельные ветви, в каждой из кото1 рых последовательно включены умножитель, накапливающий сумматор и цифровой отсчетный блок, причем первые входы перемножителей объединены, а к вторым входам первого и второго перемножителей подключены первый .= второй выходы постоянного запоминающего блока, вход которого подключен к первому выходу синхроблока„ стробоскопический преобразователь, выход которого подключен к входу аналого-цифрового преобразователя, а вход "является входом устройства, отличающийся тем, что, с целью расптирения функцио7 13287 нальных возможностей, в него введены генератор тактовых импульсов, первый управляемый умножитель частоты, оперативный запоминающий блок формироЭ

5 ватель опорного колебания, и блок установки вещественного параметра харак" теристической функции, выход которого подключен к первому входу синхроблока и второму входу первого управляемого умножителя частоты, первый вход которого подключен к выходу генератора тактовых импульсов, к вторым входам стробоскопического преобразователя и аналого-цифрового преобразователя и к 15 первому входу оперативного запоминающего блока, а выход к второму входу синхроблока и второму входу оперативного запоминающего блока, третий вход которого подключен к первому выходу аналого-цифрового преобразователя, второй выход которого подключен к входу формирователя опорного колебания, первый выход которого подключен к четвертому входу оперативного запоминаю- 25 щего блока, а второй выход к третьему входу синхроблока, второй выход которого подключен к тактовым входам накапливающих сумматоров, третий выход к тактовым входам умножителей, объеди-gp ненные входы которых подключены к выходу оперативного запоминающего блока.

2. Анализатор по ц.1, о т л и ч а юшийся тем, что синхроблок вклю63 8 чает в себя три элемента задержки, элемент И, триггер и второй управляемый умножитель частоты, первый вход которого является входом синхроблока и подключен к второму выходу формирователя опорного колебания, второй вход является первым входом синхроблока и подключен к выходу установки вещественного параметра характеристической функции и к второму входу первого управляемого умножителя частоты, а выход является первым выходом сиихроблока и подключен к входу постоянного запоминающего блока и входу второго элемента задержки, выход которого подключен к S-входу триггера, выход которого подключен к второму входу элемента И, а R-вход подключен к выходу первого элемента задержки и первому входу элемента И,выход которого является третьим выходом синхроблока и подключен к тактовым входам первого и второго перемножителей и к входу третьего элемента задержки, выход которого является вторым выходом синхроблока и подключен к тактовым входам первого и второго накапливающих сумматоров, причем вход первого элемента задержки является вторым входом синхроблока и подключен к выходу первого управляемого умножителя частоты и к третьему входу оперативного запоминающего блока.

1328763 гт

Редактор О,Головач

Заказ 3480/48

Производственно-полиграфическое предприятие, r, Ужгород, ул. Проектная, 4

Фз

Бадр

% хо

П2 ж „"„", Релком

ОУ 1б

/P)tf Q

ОЪУ f7 Выхо

УЫЧ Ф

Составитель В;Шубин

Техред М.Ходанич Корректор Л.Пилипенко

Тираж 730 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-3 >, Раушская наб., д. 4/5

1»