Триггер на мдп-транзисторах

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано в интегральных устройствах динамической логики. Цель изобретения - повышение надежности работы. Цель достигается за счет введения дополнительных транзисторов 10, 11 записи, транзисторов 12, 13 считывания , фррсирующих транзисторов 16, 17,аарядных транзисторов 18, 19, разрядного транзистора 21 и второй тактовой шины 20, позволяющих исключить паразитные емкостные выбросы и ускорить рекомбинационные процессы в подложке . 2 ил. Я сл со со ТГ) ел 4 фе/ff.f

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК ()9) (ll) А1 (5))4 G )l С li 40

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К ABTOPCKOMY СВИДЕТЕЛЬСТВУ (21) 3989273/24-24 (22) 10.12.85 (46) 15.08.87. Бюп. )) 30 (72) П.А.Копыл, В.П.Рева, А.М.Торчинский и Л.Л.Утяков (53) 681.327.6(088.8) (56) Авторское свидетельство СССР

Ф 277856, кл. С 11 С 11/40, 1970.

Патент Франции )) 2)03592, кл. С 11 С ll/00, опублик. 1972 ° (54) ТРИГГЕР НА МДП-ТРАНЗИСТОРАХ (57) Изобретение относится к цифровой вычислительной технике и может быть использовано в интегральных устройствах динамической логики. Цель изобретения - повышение надежности работы. Цель достигается эа счет введения дополнительных транзисторов 10, ll записи, транзисторов 12, 13 считывания, форсирующих транзисторов 16, l7, ьарядных транзисторов 18, 19, разрядного транзистора 21 и второй тактовой шины 20, позволяющих исключить паразитные емкостные выбросы и ускорить рекомбинационные процессы в подложке. 2 ил.

1 13306

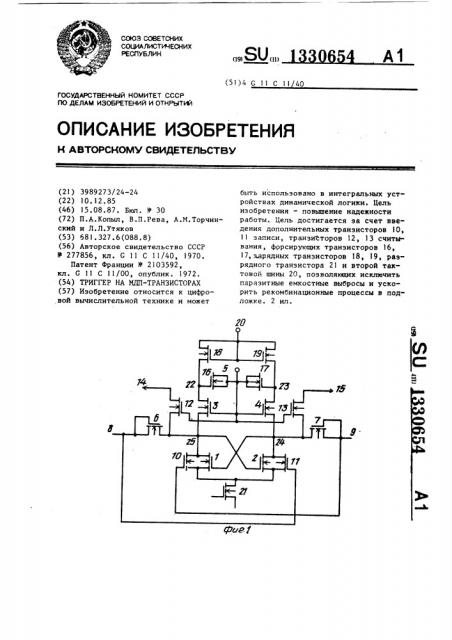

Изобретение относится к цифровой вычислительной технике и может быть использовано в интегральных устройствах динамической логики, На фиг.l представлена принципиальная электрическая схема триггера; иа фиг.2 — временные диаграммы его рабоTbl

Триггер на ЯДП-транзисторах (фиг. 1) Ip содержит первый 1 и второй 2 транзисторы хранения, первый 3 и второй 4 нагруэочные транзисторы, первую 5 тактовую шину, первый 6 и второй 7 транзисторы записи, первый 8 и второй 9 входы, третий 10 и четвертый

ll транзисторы записи, первый 12 и второй 13 транзисторы считывания, первый 14 и второй 15 выходы, первый

16 и второй 17 форсирующие транзисторы, первый 18 и второй 19 зарядные транзисторы, вторую 20 тактовую шину и разрядный транзистор 21.

Триггер работает следующим образом. 25

Во время действия тактового импульса (20) происходит заряд узлов

22 и 23 (фиг.l) до напряжения где

Триггер на МДП-транзисторах, содержащий первый и второй транзисторы хранения, истоки которых соединены между собой, а затвор и сток первого транзистора хранения соединены со

1-1т Пеор э

30 амплитуда тактовых импульт сов;

U„, — пороговое напряжение транзисторов (момент времени фиг.2).

Во время действия тактового импульса, (5) может происходить запись информации в триггер. Запись происходит высоким уровнем напряжения на одном из входов 8 или 9 триггера. В момент времени t,-с (фиг.2) узел 24 разряжается до нулевого потенциала через транзисторы 11, 21, а узел 25 заряжается до напряжения U = 45

U, — 0„„ через транзистор 6 (при этом цепь азряда — транзисторы 10 и 1 закрыты). Если запись информации в триггер не происходит (момент времени t и -t ), то он сохраняет свое предыдущее состояние, при этом узел

24 подзаряжается емкостным током от узла 22 через транзистор 3, а узел

23 разряжается до нулевого потенциала через транзисторы 2, 4 и 21. Pasряд узла 23 до нулевого потенциала приводит к уменьшению емкости между первой тактовой шиной 5 и узлом 23 до величины емкости перекрытия зат54 2 вор — сток, затвор — исток. Поэтому при уменьшении напряжения на тактовой шине 5 до нуля в узле 23 не будет выброса напряжения обратной полярности, как в случае, если вместо

Форсирующих транзисторов 16, 17 используются емкости. Затем во время действия тактового импульса р (20) происходит заряд узлов 22 и 23, при этом неосновные носители, накопленные под затворами нагрузочных транзисторов 3 и 4, рекомбинируют на источнике тактового напряжения. При записи противоположной информации в триггер процесс симметрично повторяется. Транзисторы 12 и 13 считывания подключают выходы 14, 15 триггера к узлам 24, 25 хранения только на время действия тактового импульса Ф,(5), все остальное время информация на выходах триггера остается неизменной °

Таким образом, введение в триггер зарядных транзисторов 18, 19 позволяет осуществить рекомбинацию накопленных неосновных носителей на источнике тактового напряжения (тактовой шине 20), что исключает зависимость работы триггера от рекомбинационных процессов в объеме полупроводника (в подложке) и повьппает помехозащищенность и быстродействие триггера, Введение форсирующих транзисторов 16, 17 исключает емкостные выбросы напряжения противоположной полярности в подложку, что также повышает помехозащищенность триггера. Дополнительные транзисторы 10 и 11 записи позволяют осуществить надежную запись информации в триггер. Введение транзисторов

12, 13 считывания позволяет разделить узлы 24, 25 хранения и выходы

I 4,,15 триггера, что уменьшает емкостную нагрузку на выходах триггера и повыпает его быстродействие при работе в логических схемах. Следовательно, предложенное выполнение триггера позволяет увеличить его помехозащищенность и быстродействие, что приводит к повышению надежности его работы формула изобретения

1330б54

М2 8д МФ

ФиР.2

Составитель Д. Ковалдин

Техред М. Ходан»»ч Корректор А. Обручар

Редактор M.Êåëåìå»U

Заказ 3586/52

Тираж 589 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 стоком и затвором второго транзистора хранения соответственно, первый и второй нагрузочные транзисторы, истоки которых соединены со стоками первого и второго транзисторов хране5 ния соответственно, а затворы подключены к первой тактовой шине триггера, первый и второй транзисторы записи, истоки которых соединены со стоками первого и второго транзисторов хранения соответственно, а стоки являются установочным входом и входом сброса триггера соответственно, о т л и— ч а ю шийся тем, что, с целью повышения надежности работы, в триггер введены третий и четвертый транзисторы записи, истоки и стоки которых соединены с истоками и стоками соответственно первого и второго транзисторов хранения, а затворы соединены со стоками второго и первого транзисторов записи соответственно, первый и второй транзисторы считывания, затворы которых подключены к первой тактовой шине триггера, истоки соединены со стоками первого и второго транзисторов хранения соответственно, а стоки являются соответственно прямым и инверсным выходами триггера, первый и второй форсирующие транзисторы, истоки и стоки которых подключены к первой тактовой шине триггера, а затворы соединены со стоками первого и второго нагрузочных транзисторов соответственно, первый и второй зарядные транзисторы, затворы и стоки которых подключены к второй тактовой шине триггера, а истоки соединены со стоками первого и второго нагрузочных транзисторов соответственно, и разрядный транзистор, сток которого соединен с истоками первого и второго транзисторов хранения, затвор и исток подключены к первой и второй тактовым шинам триггера соответственно, а затворы первого и второго транзисторов записи соединены со стоками первого и второго траиэис»оров записи соответствен

J но.