Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и цифровой автомати- .ке и может быть использовано для сопряжения вычислительных устройств различного быстродействия между со- . бой и устройствами ввода-вывода в интерфейсах вычислительных систем и (Л со со 1чЭ СО 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1332384

А2

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCKOMY СВИДЕТЕЛЬСТВУ

t0

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

00 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1138835 (21) 4049936/24-24 (22) 08.04.85 (46) 23.08.87. Бюл. У 31 (72) В.А.Лисицын и Л.В.Гольдреер (53) 681.327.6(088.8) (56) Авторское свидетельство СССР

Н 1138835, кл. G 11 С 19/00, 1983. (54) БУФЕРНОЕ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и циФровой автомати,ке и может быть использовано для сопряжения вычислительных устройств различного быстродействия между собой и устройствами ввода-вывода в интерфейсах вычислительных систем и

133 логических анализаторах. Цель изобретения - расширение области примене ния sa счет асинхронных записи и считывания данных. Устройство содержит последовательно соединенные информационные регистры 1, каждый из которых управляется сигналами с разрядных выходов реверсивного сдвигового .регистра 2 управления и сигналами с последующего регистра, указывающих на то, хранит он информацию или нет.

Устройство работает в двух режимах.

В первом режиме "Первый вошел — первый вышел данные поступают по сигна11 лам с входов 14 на первый регистр и автоматически продвигается в сторону последнего до первого занятого, данными регистра. Считывание осуществляется из последнего регистра по сигналам чтения, поступающим на вход !5.

2384

Во втором режиме работы — режиме буфера — задается глубина буферизации на входах 22 кода глубины буферизации по сигналу на входе 13. Запись данных происходит в первый регистр по сигналам на входе 14. С каждым сигналом весь массив данных сдвигается в сторону последнего регистра.

Считывание осуществляется из последнего регистра по сигналам 15. С каждым сигналом считывания весь массив данных сдвигается в сторону последнего регистра, Элементы И 5, 6, 23 и 24, элементы ИЛИ 3, 4, 27 и 28, элементы НЕ 7, 8, 29 и 30, элементы задержки 33 и 34, триггеры 31 и 32 обеспечивают возможность независимого синхронного обращения в режимах записи и чтения данных. 4 ил. 1 табл.

Изобретение относится к вычислительной технике и цифровой автоматике, может быть использовано для сопряжения вычислительных устройств !

i различного быстродействия между собой и устройствами ввода-вывода в интерфейсах.вычислительных систем и логических анализаторах и является усовершенствованием устройства по авт. св. Р 1138835.

Целью изобретения является расширение области применения устройства за счет обеспечения воэможности асин" хронных записи и считывания данных.

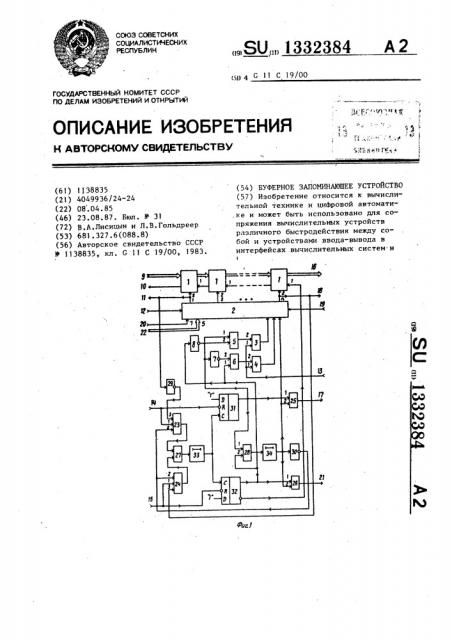

На фиг.! приведена схема буферного запоминающего устройства; на фиг.2 — временная диаграмма работы . при поочередном поступлении на вход устройства сигналов Загрузка|1, одно н 20 временном поступлении сигналов "Заrpy3Ka" и "Разгрузка" и сигнала "Разгрузка"; на фиг.3 — временная диаграмма работы при поступлении сигнала "Разгрузка" до .окончания сигнала

"Загрузка" и поочередном выполнении этих операций; на фиг.4 — пример реализации информационного регистра.

Буферное устройство содержит информационные регистры I, реверсивный сдвиговый регистр 2 управления, первый и второй элементы ИЛИ 3 и 4, первый и второй элементы И 5 и 6, первый и второй элементы НЕ 8, группу информационных входов 9, управляющий выход 10 устройства, выход 11 сигнала загруженности устройства, первый информационный вход 12 устройства, вход 13 записи. кода глубины буферизации, вход 14 сигнала записи, вход

15 сигнала чтения, группу информаци- онных выходов 16„ вьжод 17 сигнала ответа при записи, выход 18 сигнала освобождения устройства, второй информационный вход 19 устройства, вход

20 начальной установки, выход 21 сигнала ответа при чтении, группу входов 22 кода глубины буферизации, третий, четвертый, пятый и шестой элементы И 23 — 26, третий и четвертый элементы ИЛИ 27 и 28, четвертый и третий элементы НЕ 29 и 30, первый и второй триггеры 31 и 32 и первый и второй элементы 33 и 34 задержки.

Группа информационных входов 9 (фиг.1) являегся входом цепочки последовательно соединенных информаци.онных регистров 1, а группа информационных выходов 16 — выходом цепочки информационных регистров 1 ° Первый вход синхронизации каждого, кроПервый вход

Режим

Второй вход

0

Нет операции

Сдвиг вправо

Сдвиг влево

Параллельная запись

0 з 1ЗЗг ме последнего, информационного регистра 1 соединен с управляющим выходом следующего информационного ре> гистра а последнего в цепочке — с в

5 инверсным выходом триггера 32. Эти связи служат для распространения сигнала продвижения информации по цепочке информационных регистров 1 (при чтении данных). Второй вход синхронизации каждого информационного регист" ра I подсоединен к выходу соответствующего разряда реверсивного сдвигового регистра 2 управления.

С помощью этих связей регистр 2 управления задает режим работы каждого информационного регистра 1: пропускание информации при логическом

"0" на вторых входах синхронизации информационных регистров или запись (".эащелкивание") текущей информации при появлении на этих входах . логической "1". При наличии уровня логической "1" на втором входе синхронизации информационных регистров 25 разрешается запись информации с входов регистров по отрицательному фронту сигнала на первом входе синхронизации. Управляющий выход первого в цепочке информационного регист- З0 ра 1 является управляющим выходом

10 устройства.

Выходы первого и последнего разрядов регистра 2 управления являются соответственно выходом 11 сигнала за- . груженности устройства и выходом 18

35 сигнала освобождения устройства и служат для индикации загруженности устройства. Первый и второй входы задания режима регистра 2 управления 40 управляют его работой, которая определяется в соответствии с таблицей.

Первый и второй входы задания режима регистра 2 управления подключены соответственно к выходам элемен384 4 тов ИЛИ 3 и 4, первые входы которых соединены с входом !3 записи кода глубины буферизации, что позволяет задавать регистру 2 режим параллельной записи кода с входа 22 (пятый вход регистра 2 управления). Цепи прохождения сигналов на вторые входы элементов ИЛИ 3 и 4 с выходов триггеров 31 и 32 через элементы НЕ 7 и 8 и И 5 и 6 обеспечивают поступление на первый и второй входы регистра 2 управления не более одного единичного сигнала при любых сочетаниях сигналов на выходах триггеров 31 и 32.

При одновременном поступлении единичных сигналов с выходов триггеров

31 и 32 и при нулевом сигнале на, входе 13 йа первый и второй входы регистра 2 управления поступают О, что соответствует режиму "Нет операции" (таблица). Третий и четвертый входы регистра 2 управления соединены соответственно с первым 12 и вторым 19 информационными входами устройства и служат для последовательного ввода в регистр 2 управления 1 (справа через вход 19) или 0 (слева через вход

12) .

Пятый, шестой и седьмой входы реверсивного сдвигового регистра 2 управления являются входами соответственно параллельной записи информации, синхронизации и начальной установки регистра и соединены с группой

22 входов кода глубины буферизации устройства, выходом элемента 34 задержки и входом 20 начальной установки устройства.

Триггеры 31 и 32 предназначены для фиксации признаков соответственно записи и чтения данных на время выполнения соответствующих операций.

Элемент 33 задержки, выход которого соединен с синхронизирующими входами триггеров, формирует интервал времени Т1 необходимый для обеспечения времени предустановки триггеров..

Элемент 34 задержки формирует интервал времени Т2, обеспечивающий время предустановки сигналов на входах задания режима регистра 2 относительно сигнала на его входе синхронизации, а в совокупости с элементом

33 задержки — время, необходимое для прохождения информации через все информационные регистры в режиме записи, и время, необходимое для распространения сигнала продвижения ин5 1332 формации в режиме чтения через все регистры, начиная с последнего, т.е. время, необходимое для перезаписи информации в каждом из информационных регистров 1 (продвижение информации

s устройстве на один шаг вправо).

Последние два условия обеспечивают гарантированную запись информации или ее продвижение для всех информационных регистров при любой степени

1 заполнения буферного запоминающего устройства.

Элементы И 23 и 24 через элемент

ИЛИ 27 и элемент 33 задержки обеспечивают формирование сигнала синхронизации на входах триггеров 31 и 32 при поступлении на,любой из входов

14 и 15 устройства сигналов "Загрузка" / "Разгрузка" и разрешающих уровнях, - 20 сигналов на выходах элемента HE 29 и 30 и выходе 18 устройства или при

Ф ниличии сигналов на входах 14 и 15 устройства и снятия запрещающих уровней сигналов. Элемент ИЛИ 28 обеспечивает формирование сигнала логической "1" на входе элемента 34 задержки при переключении любого иэ триггеров 31 или 32 в логическую "1".

Элементы И 25 и 26 обеспечивают формирование сигналов ответов по сов. падению наличия признаков соответственно записи и чтения на выходах триггеров 31 и 32 и сигнала на выходе элемента 34 задержки, что обеспе35 чивает выработку сигналов ответов тольКо после того, как соответствующая операция выполнена устройством. .Буферное запоминающее устройство работает в двух режимах: режиме "Первый вошел и первый вышел" с заполнением, начиная с выходного информационного регистра, и продвижением информации. по мере считывания и режиме буфера с программируемой глубиной бу45 фериз ации.

При функционировании устройства ,в режиме "Первый вошел " первый вы-. шел" на вход 13 записи кода глубины буферизации и первьп» информационнъ»й вход 12 подается нулевой сигнал, а . на второй информационный вход 19— единичный.

Работа устройства начинается с. подачи на вход 20 начальной установки короткого сигнала логического "0", после чего на этом входе устанавливается сигнал логической "!". При этом на всех разрядных выходах регистра

384

2 должны установиться сигналы логического "0", разрешающие пропускание информации через все информационные регистры 1.

В исхоцном состоянии на входе 20 устройства должен присутствовать уровень логической "1", на входах 14 и

15 и выходах 17 и 21 — уровень лог»»ческого "0", при этом триггеры 31 и

32 установлены в ноль, на выходах элементов И 23 и 24 и ИЛИ 27 и 28, элементов 33 и 34 задержки должен быть уровень логического 0", .а на выходах элементов HE 29 и 30 — уровень логической "1".

Сигнал низкого уровня на первом разрядном выходе регистра 2 инвертируется элементом HE 29 и разрешает прохождение сигнала загрузки через элемент И 23.

Сигнал низкого уровня с последнего разрядного выхода регистра 2 запрещает прохождение сигнала разгрузки через элемент И 24.

Устройство готово к записи данных, сигналы записи и чтения должны подаваться на соответствукпцие входы уст-. ройства уровнем логической "1". Порядок следования сигналов иллюстри- руется временными диаграммами (фиг.2 и 3).

Сигнал записи подается на. вход 14 устройства не ранее подачи соответ-. ствующей информации на группу 9 информационных входов устройства. При поступлении информации на группу 9 информационных входов устройства цепочка информационных регистров 1 транслирует ее на группу 1б выходов.

Сигнал логической " 1" на входе 14 устройства разрешает запись логической "!" в триггер 31. Так как на остальных входах элемента И 23 имеется уровень логической "!", сигнал загрузки поступает через элементы И 23, ИЛИ 27 .на вход элемента 33 задержки.

Задержанный сигнал осуществляет запись логической "1" в триггер 31, триггер запоминает признак операции загрузки. Сигнал логической "1" через элементы И 5, ИЛИ 3 поступает на первый вход задания режима регистра

2, что соответствует (таблица) режиму "сдвиг влево" регистра 2 управления °

Сигнал логической "!" с выхода триггера:3! поступает через элемент

ИЛИ 28 и элемент 34 задержки на вход!

332384 8

Полной загрузке буфера соответствует наличие запомненной информации в каждом из информационных регистров

1. При этом на всех разрядных выхо- . дах регистра 2 управления присутствует уровень логической "!". Уровень логической "1" с первого разрядного выхода поступает на выход 11 сигнала загруженности устройства и через элемент НЕ 29 блокирует выполнение последующих операций записи (сигнал логического "0" с выхода элемента

НЕ 29 запрещает прохождение сигнала записи с входа 14 через элементы

И 23, ИЛИ 27,.элемент 33 задержки на вход синхронизации триггера 31).

Сигнал ответа при записи в этом случае s ответ на поступление сигнала записи загрузки не выдается до освобождения первого информационного регистра I.

При поступлении сигнала чтения на вход 15.он разрешает запись логической "!".в триггер 32 и поступает на один иэ входов элемента И 24. Если к этому моменту времени на остальных входах элемента И 24 имеется уровень логической "1", то сигнал разгрузки через элемент ИЛИ 27 поступает на вход элемента 33 задержки.

Задержанный сигнал осуществляет запись логической "1" в триггер 32.

Перепад уровня на инверсном выходе триггера 32, поступая на первый вход синхронизации последнего информационного регистра 1, инициирует запись в этот регистр информации с выхода предыдущего регистра и на группу 16 выходов устройства поступает новая информация (если она записана перед чтением в предыдущий регистр). синхронизации регистра 2. Регистр 2 производит сдвиг логической "1" с входа 19 в последний разряд, переключая тем самым последний информационный регистр в режим записи (защелки-

ll .5 вания") информации. Одновременно сигнал логической "I" с выхода элемента

34 задержки разрешает выдачу сигналов ответа и сигнал логической "III 10 с выхода триггера 3! поступает на выход 17 ответа при записи. Сигнал логической "1" с выхода элемента 34 задержки, кроме того, инвертируется элементом HE 30 и запрещает прохожде- !5 ние сигнала через элемент И 23, на выходе которого формируется сигнал .логичекого "0", который вызывает по- явление логического "0" на выходе элемента ИЛИ 27, и через интервал времени Т! — на выходе элемента 33 задержки.

После появления сигнала ответа при записи на выходе !7 сигнал записи загрузки на входе 14 может быть . 25 снят.

При сбросе сигнала записи триггер

31 устанавливается в исходное состояние и соответственно на выходе элемента ИЛИ 28 и через интервал времени Т2 на выходе элемента 34 задержки устанавливается логический "0" а на выходе элемента НЕ 30 — логическая

It1II

Последнее обеспечивает разрешаю" щий уровень на входах элементов 23 и 24.

Так как на последнем разрядном выходе регистра 2 управления после операции загрузки появился уровень логической 1, то на двух из трех, и и 40 входов элементов И 23 и 24 присутствует уровень логической "1", разрешающий прохождение сигнала как с входа 14, так и с входа 15. Тем самым, после первой операции записи устройство готово как к записи следующего информационного слова, так и к считыванию записанного информацйонного слова.

Запись данных может продолжаться путем повторения описанной процедуры до заполнения всех регистров. При каждой следующей записи логическая

"1" сдвигается в регистре 2 на один шаг влево, поочередно заполняя раз- 55 ряды регистра 2 и осуществляя "защел кивание" в информационных регистрах

I соответствующих этим разрядам.

Сигнал с первого входа синхронизации последнего информационного регистра 1 передается на его управляющий выход и соответственно на соединенный с ним первый вход синхронизации предыдущего информационного регистра 1. Распространяясь таким обраsoM по цепочке от последнего к первому информационному регистру, этот сигнал осуществляет поочередную перепись информации в калдый информационный регистр из предыдущего. После прохождения сигнала через все информационные регистры 1, на втором вхо-. де синхронизации которых имеется уровень логической "!", информация в

13323

10 устройстве окажется сдвинутый на один шаг в сторону выхода 16.

Сигнал логической "1" с прямого выхода триггера 32 поступает через элемент ИЛИ 28 на вход элемента 34 задержки и через элементы И 6, ИЛИ

4 — на второй вход задания режима регистра 2 управления, что соответствует (таблица) режиму "Сдвиг вправо" регистра 2 управления. Через эле" мент 34 задержки сигнал логической

"1" поступает на вход синхронизации регистра 2 управления и осуществляет последовательный сдвиг кода на его разрядных выходах на один шаг вправо.

Крайний левый (фиг.1) разрядный выход регистра 21на котором имелся уровень логической "1",переключается в

"О", а соответствующий ему информаци- 2р онный регистр переключается на пропускание информации.

Одновременно сигнал логической "

"1" с выхода элемента 34 задержки разрешает прохождение сигнала логи- 25 ческой "1", с прямого выхода триггера

32 через элемент И 26 на выход 21 ответа при чтении и через элемент НЕ

30 запрещает прохождение. сигнала через элементы И 23 и 24 на выходе эле- 30 мента И 24, соответственно на выходе элемента ИЛИ 27 появляется логический "О", а через интервал времени Т1 логический "0" появляется и на выходе элемента 33 задержки.

После появления сигнала квитирова35 ния разгрузки на выходе 21 сигнал разгрузки на входе 15 может быть снят, после чего триггер 32 возвращается в исходное состояние, на выходах элемента ИЛИ 28 и через интервал . времени Т2 на выходе элемента 34 задержки устанавливается логический

"0", а на выходе элемента НЕ 30 — логическая "1".

По!:леднее обеспечивает разрешабщий уровень на входах элементов И 23 и 24. Устройство готово к следующей операции.

Операция чтения может, повторяться до тех пор, пока на последнем разрядном выходе регистра 2 управления не окажется уровень логического "О", т.е. пока последний информационный регистр не переключится в режим пропускания информации. В этом случае

55 уровень логического "0" с последнего разрядного выхода регистра 2 управления поступит на выход 18 устройства и запретит прохождение следующих сигналов чтения разгрузки через элемент И 24 до тех пор, пока не будет произведена. запись в последний информационный в последний информационный регистр 1, т.е, пока на соответствующем выходе регистра 2 управления не появится уровень логической

"1", Сигнал ответа при чтении при поступлении сигнала чтения в полностью освобожденное устройство выдаваться не будет до загрузки хотя бы одного информационного слова.

В предлагаемом устройстве сигналы загрузки и разгрузки могут поступать независимо друг от друга в произвольные моменты времени.

Если второй по времени из пришедших на входы устройства сигналов чтения и записи появился до момента записи признаков операции в триггеры

31 и 32, т.е. до появления сигнала логической "1" на выходе элемента 33 задержки, то уровень логической "1" записывается в оба триггера только в том случае, если устройство полностью не загружено и полностью не разгружено. В обратных случаях выполняется только одна операция — соответственно чтение или запись. Так как сигнал логической "1" взаимно блокируется элементами НЕ 7 и 8 и И 5 и 6, то на входах задания режима регистра

2 управления установится комбинация

00 — нет операции (таблица).

Сигнал синхронизации с выхода элемента 34 задержки не изменит состояние регистра 2 управления. В устройстве произойдет сдвиг записанной информации на один разряд и будут выданы оба сигнала ответа. Вновь поступившая информация запишется в крайний левый (фиг.1) информационный регистр, на втором входе синхронизации которого имеется уровень логической

"1", а на группе 16 выходов произойдет смена информации.

Если второй по времени из пришедших на входы устройства сигналов записи и чтения появился после записи признака операции в триггеры 31.и 32, то первой выполняется та из операций, сигнал которой поступил на вход устройства первым. Так как сигнал синхронизации поступает на входы триггеров через элемент ИЛИ 27, то повторная запись в триггеры не может произойти до сброса сигнала на выходах

11 13323 элементов И 23 и 24, который осуществляется по окончании первой из операций, т.е. формирования сооветствующего сигнала ответа и соответственно сигнала логического "0" на выходе элемента НЕ 30.

Выполнение второй операции разре" шается после снятия сигнала первой операции, соответственно появления 10 логической "1" на выходе элемента

НЕ 30.

Для организации работы устройства в режиме буфера с программируемой глубиной буферизации необходимо в ка- 15 честве входа управления использовать соединенные вместе входы 14 и 15.

Предварительно необходимо записать в регистр 2 управления код глубины буферизации с группы входов 22, для . чего на вход 13 устройства подается сигнал логической "1 после чего на соединенные вместе входы 14 и 15 по дают сигнал логической "1". После записи кода глубины буферизации на вхо- 25 де 13 вновь устанавливается уровень логического "0".

Формула изобретения

Буферное запоминающее устройство 30 по авт. св. У 1138835, о т л и ч а ющ е е с я тем, что, с целью расширения .области применения за счет обеспечения возможности асинхронных записи и считывания данных оно содержит первый и .второй триггеры, первый и второй элементы задержки, третии, четвертын, пятый и шестой элементы И, третий и четвертый элементы ИЛИ и третий и четвертый элементы НЕ, причем выход первого триггера подключен к входу первого элемента НЕ, к первому входу третье-, 84 12 го элемента ИЛИ и к первому входу пятого элемента И, выход которого является выходом сигнала ответа при записи, прямой выход второго триггера подключен к входувторого элемента НЕ, к второму входу четвертого элемента

ИЛИ н к первому входу шестого элемента И, выход которого является выходом сигнала ответа при чтении, ин-.. версный выход второго триггера подключен к управляющему входу последнего информационного регистра, выход четвертого элемента ИЛИ подключен к входу второго элемента здержки, выход которого подключен к синхровходу реверсивного сдвигового регистра управления, к вторым входам пятого и шестого элементов И и к входу треФ тьего элемента НЕ, выход которого подключен к вторым входам третьего и четвертого элементов И, первые входы которых подключены к входам сбРоI са соответственно первого и второго триггеров и являются сортветственно входом сигнала записи и входом сигнала чтения устройства, третий вход третьего элемента И подключен в выходу четвертого элемента НЕ, вход которого подключен к выходу первого разряда реверсивного сдвигающего регистра управления, третий вход четвертого элемента И подключен к выходу последнего разряда реверсивного сдвигового регистра управпения, вь1ходы третьего и четвертого элементов И подключены к входам третьего элемента

ИЛИ, выход которого подключен к входу первого элемента задержки, выход которого подключен к С-входам первого и второго триггеров, D-входы которых подключены к шине, единичного логического сигнала устройства.

1332384

I РДНр

М

tf и

Ь

У

P f(nt)

1332384

Составитель С. Шустенко

Техред Л.Сердюкова Корректор С. Шекмар

Редактор Л. Гратилло

Тираж 589 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская иаб., д. 4/5

Заказ 3839/48

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4