Устройство для контроля постоянной памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для повышения надежности в работе полупроводниковых БИС постоянных запоминакнцих устройств с многоразрядной организацией. Целью изобретения является упрощение устройства . Устройство содержит блок 1 кодирования , селектор 4, ком1 татор 7, формирователи частности 9, 11 и блок 13 мажоритарных элементов. В устройстве используется модифицированная проверочная матрица кода Рида-Маллера. 3 нл. V

СОЮЗ СОВЕТСНИХ

Ц

РЕСПУБЛИН

Ai (19) (И) (51) 4 G 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ(СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTPM (21) 4013753/24-24 (22) 21.01.86 (46) 23.08.87. Бюл. У 31 (71) Минский радиотехнический институт (72) В.К.Конопелько, Ю.И.Щетинин и П.С.Приходько (53) 681.327.6(088.8) (56) Авторское свидетельство СССР

)) 1029231, кл. С 11 С 29/00, 1983.

Сагалович Ю.П., Щербаков Н.С.Выбор системы кодирования для защиты ЗУ от ошибок. — Проблемы передачи информа- ции, 1984 т. 20, вып. 1, с. 19-27. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСТОЯННОЙ ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано для повьппения надежности в работе полупроводниковых БИС постоянных запоминакицих устройств с многоразрядной организацией. Целью изобретения является упрощение устройства. Устройство. содержит блок 1 кодирования, селектор 4, коммутатор 7, формирователи частности 9, 11 и блок

13 мажоритарных элементов. В устройстве используется модифицированная проверочная матрица кода Рида-Маллера. 3 ил.

1 133

Изобретение относится к вычислительной технике и может быть использовано для повышения надежности работы полупроводниковых БИС постоянных запоминающих устройств с многоразрядной организацией.

Цель изобретения — упрощение устройства.

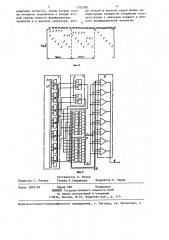

На фиг.1 представлена схема устройства для контроля постоянной памяти; на фиг.2 и 3 — проверочная матрица кода (23; !6) и конкретная реализация блока кодирования, коммутатора, первого и второго формировате,лей четности для этого кода. .Устройство (фиг.1) содержит блок ,! кодирования, входы контрольных 2 и информационных 3 разрядов, селек,тор 4 с управляющим вхоцом 5, вход б выборки байта, коммутатор 7 с информационными входами 8, первый формирователь 9 четности, входы 10 первой группы второго формирователя 11 четности, входы 12 первой группы. блока

13 мажоритарных элементов, его входы

14 и 15 соответственно второй и третьей групп и выходы 16.

В устройстве используется модифицированная проверочная матрица кода

Рида-Маллера (фиг.2). В примере конкретного исполнения (фиг.3) рассматривается устройство для работы с

16-разрядными информационными словами, считываемыми из накопителя ПЗУ и с выдачей на выход БИС ПЗУ 8-разрядных слов. На фиг.3 обозначены элементы 17 — 23 сложения по модулю два, элементы И-ИЛИ 24 и 25 и элементы

ИСКЛ!0ЧАЮЦЕЕ ИЛИ 26 — 41.

Устройство работает следующим образом .

При считывании сигналы информационных 3 и проверочных 2 разрядов с блока постоянной памяти (не показан) поступают на селектор 4 и блок

1 кодирования, на выходах 8 которого образуются контрольные соотношения

С„ . .применяемого кода (фиг,?).

Наряду с этим в зависимости от сигнала на входе 5 селектор 4 выделяет на свои выходы 12 считываемую информацию первого байта (разряды а, ) или второго байта (разряды а д ), которая поступает на входы первой группы блока 13 мажоритарных элементов и входы второй группы первого 9 и второго 11 формирователей четности. На входы 8 первой группы

2385

20

55 блока 9 поступают сигналы с выходов блока 1 (С . для кода фиг.2), а на входы 10 первой группы блока 11 сигналы с выходов коммутатора 7 (С

Св или С, С для кода фиг.2) в зависимости от сигнала с входа 6, т.е. на выходе !6 устройства спрашивается первый или .второй байт информации.

Таким образом, на входы первой 12, второй 14 и третьей 15 групп блока мажоритарных элементов поступают сигналы, реализующие системы разделенных контрольных соотношений при мажоритарном декодировании. Например, значение символов в первом разряде

m блока 13 мажоритарных элементов равно! ш, = а„, +ас+а +ав+аз+а +

1в

+ а аь + > + ав + аз + 9 а4 а5 а1т

+ а = а + ав + а + а + а

2 + к и

При этом, поскольку любой сигнал а входит не более одного раза в кажt дую систему, то любая одиночная ошибка нарушит не более одного уравнения и безошибочное значение считываемого сигнала определится в блоке 13 с помощью мажоритарного элемента на три входа.

Ф ор мула изобретений

Устройство для контроля постоянной памяти, содержащее блок кодирования, входы первой группы которого . являются контрольными входами устройства, входы второй группы являются информационными входами устройства и соединены с соответствующими входами селектора, управляющие входы которого являются входами выборки байта устройства, а выходы подключе— ны к входам первой группы блока мажоритарных элементов, выходы которого являются информационными выходами устройства, о т л и ч а ю щ е ес я тем, что, с целью упрощения устройства, в .него введены коммутатор, первый и второй формирователи четности, причем выходы блока кодирования соединены с входами первой группы йервого формирователя четности и с информационными входами коммутатора, управляющие входы которого подключены к входам выборки байта устройства, а выходы соединены с входами первой группы второго формиз 1332385

4 рователя четности, входы второй груп- ды второй и третьей групп блока мапы которого подключены к входам вто- жоритарных элементов соединены соотрой группы первого формирователя ветственно с выходами первого и вточетности и к выходам селектора вхо- рого формирователей четности.

5 а1 абабааабаб а7 аб аба Яа арааиюанааадоаа бауаЯа22а?3

1

/

Составитель О. Исаев

Редактор С. Пекарь Техред Л.Сердюкова Корректор С. Черни

Тираж 589 Подписное

ВНИИПИ Государственного комитета СССР по деЛам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 3839/48

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4