Адаптивный дельта-модулятор

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и технике связи. Использование изобретения в различных системах передачи данных позволяет повысить точность работы дельта-модулятора путем уменьшения искажений по перегрузке . Адаптивный дельта-модулятор содержит компаратор 1, D-триггер 2, полусумматор 3, счетчик 4 задержки, реверсивный счетчик 6, управляемые ключи 7, резистивную матрицу 8 и интегратор 9. Введение управляемого делителя 5 частоты обеспечивает сохранение большой крутизны приращений при больших уровнях сигнала. 1 ил. i

СОЮЗ СОВЕТСКИХ СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (5D 4 Н 03 К 3/02

NCECO+3lfl g

13 " "" """ п.ii(g„, 13

saaw „

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1246379 (21) 4044426/24-24 (22) 28.03.86 (46) 23.08.87.Бюл. Р 31 (71) Электромонтажно-наладочное управление В 9 МПС СССР и Московская железная дорога (72) П.И. Варкан,А.Я.Гении, С.А.Макаркин и М.Х.Тажиров (53) 621.376.56 (088.8) (56) Авторское свидетельство СССР

9 1246379, кл. Н 03 М 3/02; 1984.

ÄÄSUÄÄ 1332522 А 2 (54) АДАПТИВНЫЙ ДЕЛЬТА-МОДУЛЯТОР (57) Изобретение относится к автоматике и технике связи. Использование изобретения в различных системах передачи данных позволяет повысить точность работы дельта-модулятора путем уменьшения искажений по перегрузке. Адаптивный дельта-модулятор содержит компаратор 1, 0-триггер 2, .полусумматор 3, счетчик 4 задержки. реверсивный счетчик 6, управляемые ключи 7, резистивную матрицу 8 и интегратор 9. Введение управляемого делителя 5 частоты обеспечивает сохранение большой крутизны приращений при больших уровнях сигнала. 1 ил.

1332522

Изобр тение относится к автоматике и технике связи, может быть использовано в различных системах передачи данных и является усовершенствованием изобретения по авт. св.

У 1246379.

Цель изобретения — повышение точности работы устройства путем уменьшения искажений по перегрузке.

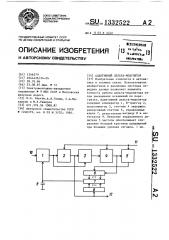

На чертеже приведена функциональная схема адаптивного дельта-модулятора.

Адаптивный дельта-модулятор содержит компаратор I,О-триггер 2, полусумматор 3, счетчик 4 задержки, управляемый делитель 5 частоты, реверсивный счетчик 6, управляемые ключи 7, резистивную матрицу 8 и интегратор 9. На чертеже обозначены информационный и тактовый входы 10 и

11 и выход 12.

Адаптивный дельта-модулятор работает следующим образом.

На первый вход компаратора 1 с входа 10 поступает входной аналоговый сигнал, одновременно на второй вход, к которому подключен интегратор 9, поступает аппроксимирующее напряжение, определяемое тем, какие из ключей 7 коммутируют выводы реэистивной матрицы 8. Сигнал ошибки, возникающий при сравнении входного аналогового сигнала и аппроксимирующего напряжения, квантуется по уровню компаратором 1 и поступает на первый вход полусумматора 3 и на информационный вход D-триггера 2. С выхода 0-триггера 2 информация поступает на общую точку резистивной матрицы 8 для управления полярностью приращений и на второй вход полусумматора 3, где происходит логическое сложение по четности информации, образуемой на выходе компаратора 1, с задержанной на такт информацией с

О-триггера 2.

В случае одинакового значения информационных сигналов (нарастание или убывание входного аналогового сигнала} полусумматор 3 выдает сигнал разрешения счета в счетчик 4 задержки. Длительность счета (времени задержки) счетчика 4 задержки устанавливается заранее в зависимости от целевого назначения дельта-модулятора. По достижении счетчиком 4 задержки установленного значения он блокируется по запрещающему входу и

Формула изобретения

Адаптивный дельта-модулятор, по авт.св.Р 1246379, о т л и ч а ю— шийся тем, что, с целью повышения точности работы устройства путем уменьшения искажений по перегрузке, введен управляемый делитель частоты, счетный и управляющий входы

55 с, 10

45 с его выхода поступает сигнал разрешения счета на управлякщий вход реверсивного счетчика 6. Этот же сигнал устанавливает на управляемом делителе 5 частоты коэффициент деления, равный единице. Таким образом, поступающие на счетный вход делителя

5 импульсы с тактового входа 11 транслируются на счетный вход реверсивного счетчика 6, которому разрешен счет в ключ. Изменение числа в реверсивном счетчике 6 приводит к изменению положения ключей 7 и, следовательно, к изменению суммарного значения сопротивления реэистивной матрицы 8, т.е. к изменению постоянной времени интегратора 9.

В результате происходит приращение аппроксимирующего напряжения с соответствующей амплитудой и полярностью.

В случае последовательности информационных сигналов разного значения (отсутствие изменения входного аналогового сигнала) на выходе полусуиматора 3 формируется сигнал логической единицы, обнуляющий счетчик 4 задержки. При этом в управляе— мом делителе 5 происходит изменение коэффициента деления на заданное установленное число (n),à в реверсивном счетчике 6 устанавливается вычитающее положение счета, что приводит к уменьшению записанного числового кода с частотой, в и раз меньшей тактовой частоты. Таким образом, уменьшение величины числового кода в реверсивном счетчике 5 происходит в выбранное количество раз медленнее, что позволяет сохранить большую крутизну приращений при больши.: уровнях сигнала.

Таким образом, уменьшаются искажения по перегрузке при резких изменениях входного сигнала, что приводит к повышению точности в работе адаптивного дельта-модулятора.

1332522 чика.

Составитель О.Ревинский

Редактор Н.Лазаренко Техред Л.Сердюкова

Корректор E.рощко

Заказ 3848/55 Тирах 901 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, r.укгород, ул. Проектная, 4 которого подключены соответственно к тактовому входу устройства и к выходу счетчика задержки, выход управляемого делителя частоты соединен со счетным входом реверсивного счет- °