Параллельный аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике и предназначено для преобразования широкополосных аналоговых сигналов с разрешающей способностью k-разрядного устройства при одном и (k-1)разрядного устройства при двух входных сигналах. Целью изобретения является расширение области применения за счет возможности одновременного преобразования большего числа сигналов. В преобразователь , содержаЕций шифратор 16, дели г -/ 152--/ 7г«- -/ Чп. с (Л I-J I -i /5, V- -; W f- -, 2 1 /6 0 X) ю У1 : :о

СОЮЗ СОВЕТСНИХ

СОИИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

А1 (19) (И) (594НОЗМ1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

<и

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 4042013/24-24 (22) 25.03.86 (46) 23.08.87. Бюл. - 31 (7l) Институт теплофиэики СО АН СССР (72) E.Â.Êîæóõîâà (53) 681.325(088.8) (56) Преобразование информации в аналого-цифровых вычислительных устройствах и системах./Под ред. Г.M,Ïåòðoва. М.: Машиностроение, 1973, с, 172-265 .

Балакай В.Г. и др. Интегральные схемы АЦП и ЦАП. — М.: Энергия, с. 220-221, рис, 6-10. (54) ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ

ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к измерительной технике и предназначено для преобразования широкополосных аналоговых сигналов с разрешающей способностью k-разрядного устройства при одном и (1 -))-разрядного устройства при двух входных сигналах. Целью изобретения является расширение области применения за счет воэможности одновременного преобразования большего числа сигналов, В преобразователь, содержащий шифратор 16 дели133253 тель 3 напряжения, группу 1 компара- 4, блок 2 управления, дне группы 14 торов с памятью введены пять муль- и 15 элементов ЗИ-НЕ, инвертор 13, Ф к-< типлексоров 5-9, два аналоговых сум- элемент 12 (2 матора 10 и 11, буферный усилитель — 1) резисторов 17. 1 э.п. ф-лы, 3 ил, Изобретение относится к измерительной технике и предназначено для преобразования параллельным методом широкополосных аналоговых сигналов с методической погрешностью k-разрядного устройства при одном входном сигнале и (k-1)-разрядного устройства при двух входных сигналах, измеряемых одновременно.

Целью изобретения является расширение области применения эа счет возможности одновременного преобразования большего числа сигналов;

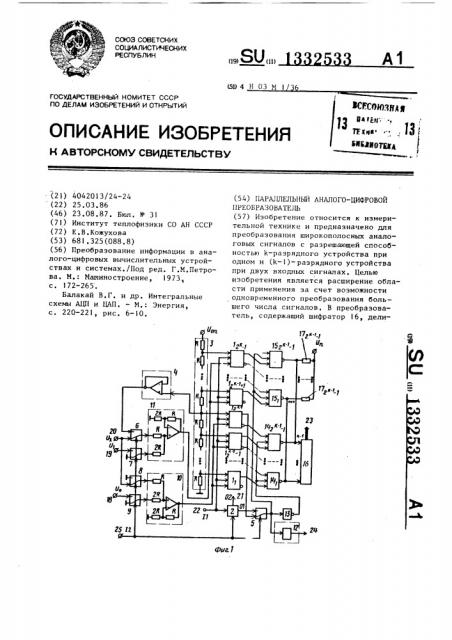

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 — функциональная схема блока управления; на фиг. 3 — временные диаграммы, поясняющие работу устройства, Параллельный аналого-цифровой преобразоват«ль содержит группу 1 соск тоящую из (2 — 1) компараторов с памятью, блок 2 управления, делитель 3 напряжения, буферный усилитель 4, с первого по пятый мультиплексоры 5-9, первый 1О и второй 11 сумматоры, элемент 12 задержки, инвертор 13, первую 14 и вторую 15 группы, состоящие к- из (2 — 1) элементов ЗИ-НЕ каждая, шифратор 16, группу токоограничивающих элементов, выполненных на резисторах 17, первую 18, вторую 19 и третью 20 входные шины, шины 21 и 22 соответственно Готовность" и "Пуск ! первые 23 и вторую 24 выходные шины и шину 25 "Режим".

Блок управления содержит с первого по четвертый одновибраторы 26-29, первый 30 и второй 3! элементы И-НЕ.

На временных диаграммах отмечены ( моменты времени t, и t прихода запускающего сигнала Il, моменты врем«ни г,, с, и С выработки сигнала

I 1

02 готовности результата и момент смены кода I2 режима работы устг ройства. Кроме того, на временных диаграммах показаны величина С задержки сигналов элементом 12, величины и „ времени преобразования одного го U и двух U u U измеряемых сиг5 налов, величина U Ä сигнала опорного

1 1 источника, сигналы П и U, на выходах аналоговых сумматоров 1О и ll соответственно и сигналы 01, 03 и 04 на первом выходе блока 2, на выходах мультиплексора 5 и элемента 12 задержки соответственно.

Преобразователь работает следующим образом.

Двоичный код 12 источника кода режима управляет двоичным 5 и аналоговыми 6-9 мультиплексорами и обеспечивает в одноканальном режиме измерения сигнала U„ прохождение на выходы мультиплексоров сигналов U а в двух20 канальном режиме измерения сигналов

U u U — прохождение сигналов U u

П, . Таким образом, в одноканальном режиме работы на первые входы сумматоров 10 и 11 поступают нулевые сиг25 палы, а на их вторые входы — измеряемый сигнал U Это обеспечивает формирование на выходах сумматоров 10 и

I I

11 сигналов 11 и U равных измеря«мому сигналу U„, которые поступают

30 на третьи входы компараторов и сравниваются с опорными напряжениями шкалы эквидистантных напряжений, сформированной на первых входах компараторов с помощью источника опорного

35 игнала Uo. и делителя 3 напряжения, В момент t по строб-сигналу Il в о к компараторах запоминается (2 — 1)-разрядный унитарный эквивалент сигнала

U„ (,) .

4р Выходные сигналы младших компараторов поступают на вторые и третьи

:входы элементов ЗИ-НЕ первой группы

14, выходные сигналы старших компараторов — на вторые и третьи входы

45 элементов ЗИ-НЕ второй группы 15, а к- выходной сигнал 2 -ro компаратора проходит через мультиплексор 5 и по1332533 ступает на вход элемента 12 задержки, на первые входы элементов ЗИ-НЕ первой группы через инвертор 13, а на первые входы элементов ЗИ-НЕ второй группы 15 непосредственно. Это обеспечивает формирование на входах шифратора 16 единичного позиционного кода из унитарного кода младших компараторов в случае Б„ -Б „ /2 или иэ унитарного кода старших компараторов в случае U„>U,„ /2. На выходах шифратора 16 формируется значение (k-1) младших разрядов двоичного эквивалента сигнала U а на выходе элемента 12 задержки — значение его старшего разряда. В двухканальном режиме измерения сигналов U и 1 < на входы сумматора 10 поступают измеряемый сигнал Uo и нулевой сигнал с выходов мультиплексоров 9 и 8, а

I на его выходе образуется сигнал Uo, равный Б, /2, который поступает на ктретьи входы с первого по (2 — 1)-й младших компараторов и сравнивается с эталонными напряжениями младшей половины шкапы опорных напряжений.

На входы сумматора ll поступают измеряемый сигнал U и выходной сигнал буферного усилителя 4 с выходов мультиплексоров 7 и 6, а на его выходе формируется сигнал П,, равный

U,/2+V /2, который поступает на треоп Э к< к тьи входы с (2 -1)-ro по (2 — 1)-й старших компараторов и сравнивается с эталонными напряжениями старшей половины шкалы опорных напряжений.

В момент t, по строб-сигналу Il в младших компараторах запоминается (2" -1)-разрядный унитарный эквивалент сигнала Uo(t. ), а в старших компараторах — (2" -1)-разрядный унитарный эквивалент сигнала U<(tд)..

В двухканальном режиме работы на выход мультиплексора поступает сигнал

01 с первого выхода блока 2 управления, который вырабатывает на интервале t, — нулевой код, а на интервале tz-t — единичный код. На входах шифратора 16 формируется единичный код из унитарного эквивалента сигнала U на интервале t -tp u

<,0 из унитарного эквивалента сигнала

< на- интервале С -t с помощью соответственно первой и второй групп элементов ЗИ-НЕ. Шифратор 16 формирует (k-1)-разрядные двоичные эквиI валенты сигнала U к моменту t u сигнала U к моменту t, а выходной сигнал 01 блока 2 задерживается элементом 12 на время t, что обеспечи<д

< вает на его выходе в момент t, номер нулевого канала, а вмомеHT tz — номер

5 первого канала двухканального устройства. Таким образом, предлагаемый преобразователь обеспечивает формирование параллельным методом как

k-разрядного результата преобразования сигнала U â одноканальном режиме, так и последовательности (k-1)— разрядных результатов преобразова" ния сигналов U u U номеров их каналов в двухканальном режиме.

В предлагаемом преобразователе обеспечивается одноканальный режим измерения параллельным методом сигнала U одного источника и двухка20 нальный режим измерения параллельным методом сигналов U V„ двух источников одновременно, что расширяет его функциональные возможности и область применения по сравнению с известным. Предлагаемое устройство позволяет также получить существенный экономический эффект-, так как устройство с гибкими, программно измененными параметрами заменяет собой три отдельных известных устройства с жесткими параметрами, что обеспечивает сокращение затрат на разработку и изготовление, формула изобретения

1. Параллельный аналого-цифровой преобразователь, содержащий первую входную шину, шифратор, делитель напряжения, с первого по (2 — 1)-й ком40 параторы с памятью, первые входы которых объединены и являются шиной

"Пуск«, а вторые входы соединены соответственно с выходами делителя напряжения, первый и второй входы кото45 рого являются соответственно шиной нулевого потенциала и шиной опорного напряжения, а выходы шифратора являются первыми выходными шинами, отличающийся тем, что, 50 с целью расширения Области применения эа счет возможности одновременного преобразования большего числа сигналов, в него введены с первого по пятый мультиплексоры, первый и второй аналоговые сумматоры, буферный усилитель, блок управления, первая и вторая группы из (2" — 1) элементов ЗИ-НЕ каждая, инвертор, элемент задержки, 1332533 вход последнего из которых объединен с первым информационным входом второго мультиплексора и является первой

К-1 входной шиной, третьи входы с (2 +

+1)-го по (2 — 1)-й компараторов с памятью объединены и подключены к выходу второго сумматора, первый вход ко,"орого соединен с выходом третьего

10 мультиплексора, а второй вход подключен к выходу второго мультиплексора, второй информационный вход которого соединен с выходом буферного усилителя, вход которого соединен с вторым квходом 2 -го компаратора с памятью, вторые входы с первого по (2 — 1)-й кэлементов ЗИ-HE второй группы соединены соответственно с прямыми выхок- к дами с (2 +1)-ro по (2 — 1)-й компа20 раторов, а третьи входы с первого по (2 -2)-й элементов ЗИ-НЕ второй группы подключены соответственно к инверсным выходам с (2" +l)-го по

K (2 -1)-й компараторов с памятью.

25 с первого по (2 — 1) токоограничива) к-1 ющие элементы, выполненные на резисторах,,первые выводы которых объединены и являются шиной питания, а вторые выводы подключены к соответствующим выходам одноименных элементов

ЗИ-HF. первой и второй групп и объединены с соответствующими входами шиф ратора, первые входы элементов ЭИ-НЕ второй группы объединены с входом инвертора и элемента задержки и подключены к выходу первого мультиплексора, выход элемента задержки является второй выходной шиной, первые входы элементов ЗИ-HF первой группы объединены и подключены к выходу инвертора, вторые входы соединены соответственно с прямыми выходами с первого по (2

-1)-й компараторов с памятью, а третьи входы соединены соответственно с инверсными выходами с второго по к- (2 )-й компараторов с памятью„прямой выход последнего иэ которых соединен с первым информационным входом первого мультиплексора, второй информационный вход которого подключен к первому выходу блока управления, второй выход которого является шиной Готовность, первый вход явля30 ется шиной "11уск, а второй вход объединен с входами управления с первого по пятый мультиплексоров и является шиной "Режим, первые информационные входы третьего, четвертого и пятого мультиплексоров объединены и являются шиной нулевого потенциала, вторые информационные входы третьего и пятого мультиплексоров являются соответственно второй и третьей входными шинами, третьи входы с пер- 40

Н-1 вого по 2 -й компараторов с памятью объединены и подключены к выходу первого сумматора, первый и второй входы которого соединены соответственно с выходами пятого и четвертого муль- 4 э типлексоров, второй информационный

2. Преобразователь по п. 2, о тл и ч а ю шийся тем, что блок управления выполнен на первом, втором, третьем и четвертом одновибраторах и первом и втором элементах И-HE выход последнего из которых является вторым выходом блока управления, первый вход соединен с выходом четвертого одновибратора, а второй вход подключен к выходу второго одновибратора, вход которого объединен с первым входом первого элемента И-НЕ, подключен к выходу первого одновибратора и является первым выходом бло ка управления, первым и вторым входами которого являются соответственно вход первого одновибратора и второй вход первого элемента И-НЕ, выход которого соединен с входом третьего одновибратора, выход которого подключен к входу четвертого одновибратора.

1332533 и, Составитель Ю,Спиридонов

Редактор И.Нулла Техред Л.Сердюкова Корректор Е.Рошко

Заказ 3848/55

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 и, 1

Уиг. 2

4 4

Тираж 901 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5