Устройство цикловой синхронизации

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи . Цель изобретения - сокращение времени синхронизации. Устр-во содержит тактовый г-р 1, опорный г-р 2 функций Уолша, блок принятия 3 решения , счетчик 4, АЦП 5, ЦАП 6, входные регистры 7, мультиплексоры 8 и регистр 9 памяти. В устр-ве последовательно осуществляется прием отсчетов входного группового сигнала четного , а затем нечетного ансамблей сигналов. В момент прихода импульса конца цикла происходит разблокировка каналов приема и в устр-ве осуществляется временной сдвиг входного группового сигнала относительно опорных функций Уолша на величину исходной ошибки синхронизации без затрат времени. Цель достигается введением ЦАП 6, регистров 7 и 9 и мультиплексоров 8. 2 ил. % (Л вх. N 1 7, гЗ ; Р -. . . - п. Н Вых.1 со со to ел 01 СП

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

@ ге. (50 4 Н 04 L 7/08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3891110/24-09 (22) 30.04.85 (46) 23.08.87. Вюл. № 3 1 (72) Н.П. Суворов и В.И. Корыстин (53) 621.394.662(088.8) (56) Авторское свидетельство СССР

¹ 1190531, кл. Н 04 L 7/08, 1985. (54) УСТРОЙСТВО ЦИКПОВОЙ СИНХРОНИЗА|ЦИИ (57) Изобретение относится к электросвязи. Цель изобретения — сокращение времени синхронизации. Устр-во содержит тактовый г-р 1, опорный г-р 2 функций Уолша, блок принятия 3 реше„,80„„1332555 А 1 ния, счетчик 4, АЦП 5, ЦАП 6, входные регистры 7, мультиплексоры 8 и регистр 9 памяти. В устр-ве последовательно осуществляется прием отсчетов входного группового сигнала четного, а затем нечетного ансамблей сигналов. В момент прихода импульса конца цикла происходит разблокировка каналов приема и в устр-ве осуществляется временной сдвиг входного группового сигнала относительно опорных функций Уолша на величину исходной ошибки синхронизации беэ затрат времени. Цель достигается введением

ЦАП 6, регистров 7 и 9 и мультиплек соров 8. 2 ил.

1332

45

Изобретение относится к электросвязи и может быть использовано в системах многоканальной связи с кодовым разделением, использующих в

5 качестве канальных несущих функции

Уолша.

Целью изобретения является сокращение времени синхронизации.

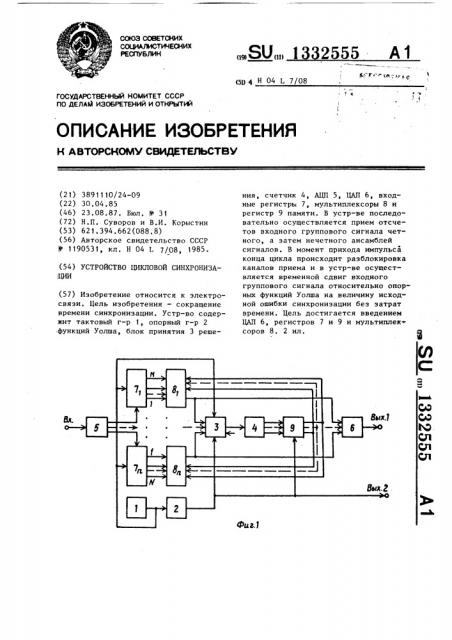

На фиг. 1 представлена блок-схема предлагаемого устройства, на фиг. 2 — временные диаграммы работы устройства.

Устройство цикловой синхронизации содержит тактовый генератор 1, опорный генератор 2 функций Уолша, блок 3 принятия решения, счетчик 4, аналого-цифровой преобразователь (АЦП) 5, цифроаналоговый преобразователь (ЦАП) 6, входные регистры

7„, ..., 7„, мультиплексоры

8,, ..., 8„, регистр 9 памяти.

Устройство работает следующим образом.

Последовательность чередующихся 25 многоуровневых групповых сигналов (четных и нечетных) (фиг. 2а) поступает на вход АЦП 5. Первый принятый отсчет входного группового сигнала на выходе АЦП 5 представляется соот- 30 ветствующим кодом (фиг. 2б, в, г), каждый разряд которого поступает на вход соответствующего входного регистра 7. На управляющий вход регистра 7 поступает тактовый импульс с вы35 хода тактового генератора 1 (фиг. 2д) .

ПРИ этом первый принятый отсчет входного сигнала в и-значком двоичном коде записывается параллельно в первые ячейки и входных регистров 7 ° 40

В исходном состоянии на адресных входах мультиплексоров 8 присутствует код ошибки синхронизации 000, под действием которого на выходы мультиплексоров 8 (фиг. 2 д, е, ж) коммутируются их первые входы. Следовательно, параллельный код первого отсчета, записанный в первых ячейках регистров 7, поступает на входы блока 3 принятия решения и ЦАП 6.

По первому принятому отсчету блок 3 настраивается на прием отсчетов только одного типа групповых сигналов (четного или нечетного). На стробирующий ВХОД блОка 3 принЯтиЯ решения с выхода тактового генератора подается тактовый импульс, который поступает через открытый канал приема в блоке 3 (фиг. 2н) на вход

555 2 обратного счета счетчика 4. На выходе счетчика 4 в этом случае появляется двоичное число III (фиг. 2 о,п,р).

Под воздействием второго тактового импульса происходит запись в первые ячейки входных регистров 7 кода второго отсчета группового сигнала и переэапись кода первого ОТСчета входного сигнала во вторые ячейки регистров 7. Код второго отсчета с первых выходов регистров 7 через мультиплексор 8 поступает в блок 3 принятия решения. Если второй отсчет входного группового сигнала принадлежит к тому же ансамблю сигналов, что и первый, то второй тактовый импульс проходит через блок 3 на вход обратного счета счетчика 4. Состояние счетчика 4 изменяется, на его выходах появляется двоичный код 110 (фиг. 2 о, и, р).

Аналогично происходит прием последующих отсчетов входного группового сигнала, одного ансамбля сигналов (в данном случае четного). После прихода третьего тактового импульса в счетчике 4 записывается двоичное число 101, а после четвертого импульса (четвертый принятый отсчет четного сигнала) — число 100. После этого на входы блока 3 принятия решения поступают отсчеты нечетного группового сигнала. Канал приема нечетного группового сигнала в блоке

3 закрыт, следовательно, тактовые импульсы с выхода тактового генератора 1 не проходят на вход обратного счета счетчика 4.

По окончании цикла интегрирования из опорного генератора 2 (фиг. 2 и) на управляющие входы блоков 3 и 9 поступает импульс конца цикла (ИКЦ).

В блоке 3 принятия решения ИКЦ разблокирует каналы приема. В регистре

9 памяти происходит перезапись кода ошибки синхронизации с выходов счетчика 4 (фиг. 2 к, д, м). В результате этого состояние мультиплексора 8 изменяется. Код ошибки синхронизации, поступающий на адресные входы мультиплексоров 8 становится равным 100. Под воздействием этого кода на выходы мультиплексоров 8 коммутируются пятые входы (входы мультиплексоров 8 нумеруются числами от 0 до (М-1) (фиг. 2 б, в, г, д, е, ж), процесс смены состояния мультиплексора 8 показан стрелками). Таким об1332555 разом, в момент прихода ИКЦ в устройстве происходит временной сдвиг входного группового сигнала относительно опорных функций Уолша на ве5 личину исходной ошибки синхронизации †. 4 7ь, без затрат времени.

На следующем цикле интегрирования входного группового сигнала на адресных входах мультиплексора 8 присутствует код 100. Считывание кодов отсчетов сигнала происходит с пятых ячеек входных регистров 7. По окончании второго цикла интегрирования на выходах счетчика 4 а момент прихода ИКЦ вновь записывается число !00 — код первоначальной расстройки синхронизации, который переписывается в регистр 9 памяти, и состояние коммутаторов не изменяется. Система находится в синхрониэме.

Если в процессе передачи информации происходит сбой синхрониэма, то поиск группового сигнала осуществляется аналогично описанному алгоритму. 26

Разница заключается в том, что исходное состояние счетчика 4 определяется величиной предыдущей расстройки синхрониэма и новый код ошибки вычитается из записанного в счетчике 4. gp

Формула и э о б р е т е н и я

Устройство цикловой синхронизации многоканальных систем связи, содержащее тактовый генератор и соединенные последовательно опорный генератор функций Уолша, блок принятия решения и счетчик, а такие аналогоцифровой преобразователь, вход которого является входом устройства, при этом выход тактового генератора соединен с тактовым входом блока принятия решения, о т л и ч а ю щ е— е с я тем, что, с целью сокращения времени синхронизации, введены цифроаналоговый преобразователь, и входных регистров (и log

1332555 б ф

О

9 б

Ю и

6 и

1-3

3 Л и 8

О 5П 5g

Составитель А.Андрианов

Техред Л.Сердюкова

Корректор И.Муска

Редактор Л.Лангазо

Заказ 3850/56

Тираж 638 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 г

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4