Устройство формирования сигнала отсчета для дифференциального кодера изображений

Иллюстрации

Показать всеРеферат

Изобретение относится к телевидению . Цель изобретения - повышение помехоустойчивости. Устр-во содержит эл-ты задержки 1-4, блоки сравнения (БС) 5 и 6, эл-ты ИЛИ-НЕ 7-10, ключи 11-14 и сумматор 15. Цель достигается введением БС 6 и эл-тов ИЛИ-НЕ 7- 10, с помощью которых на выходе устрва формируется предсказанное значение отсчета, равное полусумме двух средних по величине отсчетов среди отсчетов . Дана ил. выполнения БС. 3 ил. (Л fZ 15 Butod

СООЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 Н 04 N 7 137 5 93

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4035565/24-09 (22) 10.03.86 (46) 23.08.87. Бюл. Н - 31 (71) Ленинградский электротехнический институт связи им. проф. М.А.БончБруевича (72) Д.А.Копылов и М.К.Райхельсон (53) 621.397.3(088.8) (56) Харатишвили Н.Г. Дифференциальная импульсно-кодовая модуляция в системах связи. — М: Радио и связь, 1982, с. 74.

Авторское свидетельство СССР

В 906033, кл. H 04 N 7/13, 1982.

„„SU„„1332562 А 1 (54) УСТРОЙСТВО ФОРМИРОВАНИЯ СИГНАЛА

ОТСЧЕТА ДЛЯ ДИФФЕРЕНЦИАЛЬНОГО КОДЕРА

ИЗОБРАЖЕНИЙ (57) Изобретение относится к телевидению. Цель изобретения — повышение помехоустойчивости. Устр-во содержит эл-ты задержки 1-4, блоки сравнения (БС) 5 и 6, эл-ты ИЛИ-НЕ 7-10, ключи

11-14 и сумматор 15. Цель достигается введением БС 6 и эл-тов ИЛИ-НЕ 710, с помощью которых на выходе устрва формируется предсказанное значение отсчета, равное полусумме двух средних по величине отсчетов среди отсчетов. Дана ил. выполнения БС. 3 ил.

1 1332

Изобретение относится к технике цифрового телевидения, преимущественно к системам с дифференциальной импульсно-кодовой модуляцией.

Цель изобретения — повышение помехоустойчивости.

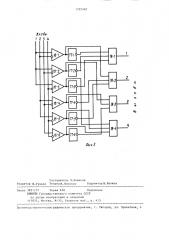

На фиг. 1 представлена электрическая структурная схема устройства для формирования сигнала отсчета для диф- 1и ференциального кодера изображений, на фиг. 2 — пространственные диаграммы, поясняющие работу устройства, на фиг. 3 — электрическая структурная схема первого блока сравнения. !5

Устройство для формирования сигнала отсчета для дифференциального кодера иэображений содержит первый— четвертый элементы 1-4 задержки, первый и второй блоки 5 и 6 сравнения, первый — четвертый элементы ИЛИ-НЕ

7-10, первый — четвертый ключи 11 — 14, сумматор 15.

Первый блок 5 сравнения (фиг. 3) содержит компараторы 16-1 — 16-6, элементы ИЛИ-HE 17-1 — 17-6, элементы И

18-1 — 18-4.

Устройство для формирования сигнала отсчета для дифференциального кодера изображений работает следующим образом.

На вход устройства поступают восстановленные значения отсчетов S(m,п), где m — номер элемента изображения в строке, n — номер строки изображения. Время задержки для первого, второго и четвертого элементов 1, ? и

4 задержки составляет 1 такт дискретизации, а время задержки третьего элемента 3 задержки равно (М-3) тактов, где М вЂ” число тактовых интерва40 лов за период строки развертки. Поэтому на выходах первого — четвертого элементов 1-4 задержки отсчеты задержаны относительно входных восстановленных отсчетов соответственно на 1 такт дискретизации, на 2 такта, на (M-1) тактов и на М тактов. Таким образом, на выходах первого — четвертого элементов 1-4 задержки присутствуют значения отсчетов соответственно S(m — 1,п); S(m-2,п); S(m+1,п-1) и

S(m,п-1) (фиг. 2).

Первый блок 5 сравнения вырабатывает сигнал логической единицы на

55 том из выходов, номер которого соответствует номеру входа, на котором присутствует минимальное значение сигнала. На остальных выходах первый

562 2 блок 5 сравнения формирует сигнал ло- гического нуля.

Второй блок 6 сравнения формирует сигнал логической единицы на том из выходов, номер которого соответствует номеру входа, на котором присутствует максимальное значение сигнала. На остальных выходах второй блок

6 сравнения формирует сигналы логического нуля.

Поскольку каждый из выходов первого блока 5 сравнения подключен к первому входу соответствующего логического элемента ИЛИ-НЕ 7-10, а каждый из выходов второго блока 6 сравнения подключен к второму входу соответствующего логического элемента ИЛИ-НЕ

7-10, то на выходах первого — четвертого логических элементов ИЛИ-HE 710 формируются два сигнала логического нуля и два сигнала логической единицы, причем логические нули формируются на выходах тех логических элементов ИЛИ-НЕ 7-10, номера которых соответствуют номерам выходов первого и второго блоков 5 и 6 сравнения с сигналами логической единицы.

Таким образом, на управляющие входы первого — четвертого ключей 11-14 подаются два сигнала логического нуля и два сигнала логической единицы, причем максимальному и минимальному отсчетам среди четырех отсчетов, подаваемых на информационные входы ключей 11-14, соответствуют сигналы логических нулей, а двум средним по величине отсчетам — сигналы логических единиц. Каждый из ключей 11-14 пропускает на свой выход информационный входной сигнал, когда на управляю" щем входе присутствует сигнал логичес« кой единицы, а при наличии на управляющем входе логического нуля сигнал с информационного входа не пропускается. Поэтому, на двух входах сумматора

15 присутствуют информационные сигналы двух средних по величине отсчетов, а на двух остальных входах сумматора

15 сигналы отсутсвуют. Таким образом, на выходе сумматора 15 образуется псмлусумма двух средних по величине отсчетов. Следовательно, на выходе устройства формируется предсказанное . значение отсчета, равное полусумме двух средних по величине отсчетов среди отсчетов.

Ф о р м у л а и з о б р е т е н и я

Устройство формирования сигнала отсчета для дифференциального кодеAldglgoJt щелока

7екущау строка

Фи@2 з 133256 ра изображений, содержащее последовательно соединенные первый, второй, третий и четвертый элементы задержки, первый блок сравнения, сумматор и первый, второй, третий и четвертый

5 ключи, сигнальные входы которьщ соединены с выходами соответствующих элеэлементов задержки, о т л и ч а ю— щ е е с я тем, что, с целью повьппения помехоустойчивости, введены второй блок сравнения, первый, второй, третий и четвертый входы которого объединены соответственно с первым, вторым, третьим и четвертым входами первого блока сравнения и с сигнальными входами первого, второго, третьего и четвертого ключей, первый, 2

4 второй, третий и четвертый элементы

ИЛИ-НЕ, выходы которых подключены к управляющим входам соответственно первого, второго, третьего и четвертого ключей, при этом первый, второй, третий и четвертый выходы первого блока сравнениня соединены с первыми входами соответственно первого, второго, третьего и четвертого элементов ИЛИ-НЕ, первый, второй, третий и четвертый выходы второго блока сравнения соединены с вторыми входами соответственно первого, второго, третьего и четвертого элементов ИЛИ-НЕ, а входы сумматора соединены с выходами ключей.

1337 562

Входы

1 234

Фиг. У

Составитель Э. Борисов

Редактор Н. Гунько Техред И.!1опович Корректор В.Бутяга

Заказ 3851/57 Тираж 638 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4