Устройство для управления транзисторным инвертором

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике и может быть использовано во вторичных источниках питания для управления генераторами, работающими на переменную нагрузку. Целью изобретения является повышение надежности и КПД. Поставленная цель достигается благодаря введению блоков управления 11 и 14 и блоков защиты 10 и 13. При возникновении аварийного режима ограничивается мощность, вьщеляемая в транзисторах 2 и 3, науровне, обеспечивающем их нормальный режим работы . 2 з.п, ф-лы, 6 ил. (Л с bo САЭ 4 00 1чЭ фиг. 7

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 Н 02 Г1 7!537

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4059708/24-07 (22) 22.04,86 (46) 30.08.87. Бюл. № 32 (71) Уфимский авиационный институт им. Серго Орджоникидзе (72) А.В.Иванов, А.Х.Узянбаев, С.Т.Буртан и А.А.Фаткуллин (53) 621.316.727(088.8) (56) Авторское свидетельство СССР № 521642, кл. H 02 M 7/537, 1976.

Авторское свидетельство СССР

¹ 788313, кл. H 02 M 7/537, 1980,, (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ТРАНЗИСТОРНЫМ ИНВЕРТОРОМ

„„80„1334327 А 1 (») Изобретение относится к электротехнике и может быть использовано во вторичных источниках питания для управления генераторами, работающими на переменную нагрузку, Целью изобретения является повьппение надежности и

КПД. Поставленная цель достигается благодаря введению блоков управления 11 и 14 и блоков защиты 10 и 13.

При возникновении аварийного режима ограничивается мощность, выделяемая в транзисторах 2 и 3, на уровне, обеспечивающем их нормальный режим работы. 2 з.п. ф-лы, 6 ил.

1334327

Изобретение относится к электроТехнике и может быть использовано во вторичных источниках .питания для управления генераторами, работающими

) на переменную нагрузку.

Цель изобретения — повьш ение надежности и КПД.

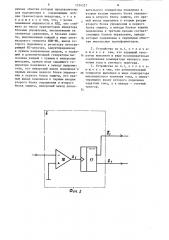

На фиг.1 представлена функциональНая схема устройства; на фиг.2 — схе- ip ма задающего генератора; на фиг.3 схема дополнительного генератора; на фиг.4 — схема блока управления; на фиг.5 — схема блока защиты, на фиг.б — временные диаграммы.

Устройство для управления транзисторным инвертором 1, выполненным IIQ полумостовой схеме на транзисторах 2 и 3 с нагрузкой 4, подключенной к вторичной обмотке выходного трансфор- 2р матора 5, содержит задающий 6 и дополнительный 7 генераторы, входы которых через выпрямитель 8 подключены к датчику 9 тока инвертора i. Инверсный выход генератора 6 подключен к 25 первым входам первого блока 10 защиты и первого блока 11 управления, выход которого через импульсный трансформатор 12 подключен к управляющему входу транзистора 2. Прямой выход ге- 3р нератора 6 подключей к первым входам второго блока i3 защиты и второго блока 14 управления, выход которого через импульсный трансформатор 15 подключен к управляющему входу тран- 35 зистора 3. Инверсный выход генератора

7 подключен к вторым входам блока 11 управления и блока 13 защиты, выход которого подключен к третьему входу блока 14 управления. Прямой выход ге- 1о нератора 7 подключен к вторым входам блока 14 управления и блока 10 защиты, выход которого подключен к третьему входу блока 11 управления. 3адающий генератор 6 выполнен на ком- 45 параторе 16, прямой вход которого соединен с общей шиной, а выход подключен к счетному входу триггера 17.

Дополнительный генератор 7 содержит компаратор 18, инвертирующий вход 5р которого подключен к зацатчику 19 тока, а выход — к счетному входу триггера 20.

Блоки 11 и 14 управления образованы последовательно соединенными трехвходовым элементом ИЛИ-HE 21 и усилителем 22, Блоки защиты выполнены в виде двухвходового элемента ИЛИ-НЕ 23, выход которого подключен к резистору

24 интегрирующей RC-цепочки 25, зашунтированному в прямом направлении диодом 26.

Устройство работает следующим образом.

При подаче. питания (фиг. 1) с выхода триггера 17 задающего генератора

6 поступают противофазные сигналы

Q, и Q>, с вьгхода триггера 20 дополнительного генератора 7 — сигналы

Я и Я, также находящиеся в противофазе, сигналы единичного уровня, сигналы нулевого уровня (фиг.б г, д).

Сигналы Q, и Я (сигналы нулевого уровня в момент t = t,) поступают на два входа элемента ИЛИ-НЕ 21 блока

11 управления, сигналы Q< и Q (сигналы единичного уровня в момент — t ) — также на два входа элемента

ИЛИ-НЕ 21 блока 14 управления. Одновременно на входы элемента ИЛИ-НЕ

23 первого блока 10 защиты по току поступают сигналы Q< и Q а на входы второго элемента ИЛИ-НЕ 23 блока 13 защиты по току — сигналы Q„ Q . На выходах первого и второго блоков 10 и 13 защиты по току формируются сиг" налы U и U . При уровне, большем порога срабатывания элементов ИЛИ-НЕ

23, эти сигналы являются запрещающими, а при уровне, меньшем порога срабатывания элементов 23,- разрешающими для соответствующих блоков управления. Сигналы.U u U, являющиеся на данный момент времени разрешающими, подаются на третьи входы соответственно блоков 11 и 14 управления. В результате на базовый вывод транзистора 2 подается отпирающий сигнал, длительность которого равна времени существования логического сочетания

Е, = Ц, + Ц (фиг.б к) . По диагонали моста, образованной последовательным соединением датчика 9 тока и первичной обмоткой трансформатора 5, через транзистор 2 течет ток Е:. Сигнал с датчика 9 через выпрямитель 8 (инвертирующий вход компаратора 16) подается на инвертирующий вход компаратора

16 задающего генератора 6 и на прямой вход компаратора 18 дополнительного генератора 7. При достижении в мо. мент t = t сигналом величины I o ( дополнительный генератор 7 инвертирует свои сигналы, отключается сигнал

Е, на отпирание транзистора 2, а на выходе первого блока 10 защиты по то1334327

1. Устройство для управления транзисторным инвертором, содержащее задающий генератор, дополнительный генератор, вход которого через выпрямитель подключен к датчику тока нагрузки, и импульсные трансформаторы, вто55 ку появляется на время „ сигнал запрета Б, образованный по логическому сочетанию сигналов генераторов

+ г

Длительность t » выбрана исходя иэ условия ограничейия мощности, выделяемой в транзисторах инвертора 1 при работе схемы на переменную нагрузку: tsanp = Тьь,ап,(где К ал, = 0,5-0,9 в зависимости от условий допустимого изменения нагрузки 4) .

Одновременно ток транзистора 2 начинает убывать. В момент (t = t„) достижения сигналом с датчика 9 тока нулевого значения задающий генератор

6 также инвертирует свои сигналы. С этого времени во втором блоке 14 управления начинает формирояаться отпирающий транзистор 3 сигнал, длительность которого равна времени существования логического сочетания Е

= Q + Q (фиг.6 л) . По диаго àëè мо2 ста, образованной последовательным . соединением датчика 9 тока и первичной обмоткой трансформатора 5, через транзистор 3 течет ток I но уже в противоположном направлении. Сигнал с датчика 9 через выпрямитель 8 подается на вход задающего генератора 6 и на вход дополнительного генератора 7.

При достижении в момент t сигналом величины I дополнительный генератор 7 вновь инвертирует свои сигналы, отключается сигнал Ег на отпирание транзистора 3, а на выходе второго блока 13 защиты по току на время t»„ появляется сигнал запрета U образованный по логическому сочетанию сигналов генераторов 6 и

7: F = Q, + Ц (фиг.6 ж, и) . Ток через транзистор 3 начинает убывать. В момент (t = t,) достижения сигналом с датчика 9 тока нулевого значения задающий генератор 6 вновь инвертирует свои сигналы.. К этому времени на ,вход первого блока 11 управления с выхода первого блока 10 защиты по току уже подан сигнал логического разрешения U,, а на вход второго блока

14 управления с выхода второго блока

13 защиты по току — сигнал логического запрета U . В дальнейшем процессы в схеме повторяются.

Пусть теперь в момент t = t резко падает сопротивление нагрузки 4. В результате возрастает амплитуда тока в диан пали моста, например, через транзистор 3. Сигнал с датчика 9 тока через выпрямитель 8 достигает значения I в момент t = t „,, быстрее на время 4 = („— „, ) — (t + — „).

Соответственно, все процессы на включение и выключение транзистора 3 происходят раньше на это же время . Однако в момент t = t„+ транзистор 2 не включается, хотя задающий генератор 6 и инвертирует свои сигналы, так как на третьем входе первого блока 11 управления находится сигнал логического запрета U,, сформированный в первой волоке 10 защиты по току за время (t „ — t „, ) в предыдущий цикл работы транзистора 2 по логическому сочетанию F, = Q, + Q (фиг.6 е, э).

Транзистор 2 включается в работу лишь по поступлении в момент и = t„+, логического разрешения U из блока защиты в первый блок 11 управления и выключится по достижении сигналом с датчика 9 тока значения I > (в это время отключается сигнал Е, на отпирание транзистора 2, а на выходе первого блока 10 защиты по току появляется сигнал запрета U который запрещает прохождение сигнала на включение транзистора 2 сразу после срабатывания транзистора 3). В момент достижения сигналом с датчика 9 тока нулевого значения начинает формироваться сигнал Ег на включение транзистора 3, так как во второй блок 14 управления уже поступил сигнал логического разрешения U с выхода второго блока 13 защиты по току. По достижении сигналом с датчика 9 тока значения I сигнал на его отпирание Е прекращается. Транзистор 3 выключается. Дальнейшая работа инвертора 1 в этом режиме происходит аналогично.

Таким образом, благодаря введению блоков управления и блоков защиты при возникновении аварийного режима ограничивается мощность, выделяемая в транзисторах, на уровне, обеспечивающем их нормальный режим работы, что повьппает надежность и КПД устройства.

Формула изобретения

1334327 ричные обмотки которых предназначены для подключения к управляющим вхбдам транзисторов инвертора, о т л и ч а ю щ е е,с я тем, что, с целью повышения надежности и КПД, оно снабжено по числу транзисторов инвертора блоками управления, выполненными на элементах сравнения, и блоками защиты, выполненными каждый в виде двухвходового элемента ИЛИ-НЕ, выход которого подключен к резистору интегрирующей КС-цепочки, зашунтированному в прямом направлении диодом, а задающий и дополнительный генераторы выполнены каждый с прямым и инверсным выходами, причем вход задающего генератора подключен к выходу выпрямителя, его инверсный выход подключен к первым входам первого. блока управления и первого блока защиты, его прямой выход подключен к первым входам второго блока управления и второго блока защиты, инверсный выход дополнительного генератора подключен к вторым входам первого блока управления и второго блока защиты, его прямой выход подключен к вторым входам второго блока управления и первого блока защиты, а выходы блоков защиты подключены к третьим входам соответствующих блоков управления, выходы

10 которых подключены к первичным обмоткам импульсных трансформаторов.

2 ° Устройство по п.1, о т л и ч аю щ е е с я тем, что задающий гене15 ратор выполнен в виде последовательно соединенных компаратора нулевого значения тока и счетного триггера.

3. Устройство по п.1, о т л и ч аю щ е е с я тем, что дополнительный

20 генератор выполнен в виде компаратора максимального значения тока, к инвертирующему входу которого подключен эадатчик тока, а к выходу — счетный триггер.

1334327

Рие. 5

i334327

,! Р I Р 9Р

9:

)(1 Р

@9Р9 P g

Р e pa к тор,Й, П . (оп r.=. = а.:r

Тираж 659 Подписное

ВН !ИПЯ Государственного комитета СССР л изобретений и открытий

1I3035,,:Москва, Ж-: з,, аушская нао., д, 4/5

Заказ 397б/54

Производственно †полиграфическ предприятие, г. Ужгород, ул. Проектная, 4

Р

Co c t àL Hòåëü В . Жмур ов

Техред И.Ходанич Корректор А.Зимокосов