Генератор случайных процессов

Иллюстрации

Показать всеРеферат

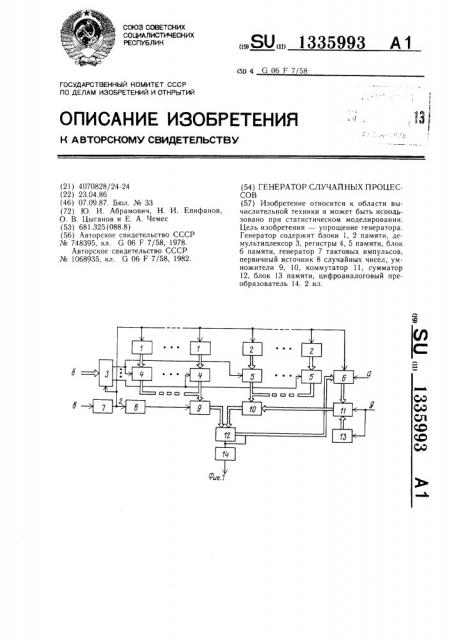

Изобретение относится к области вычислительной техники и может быть использовано при статистическом моделировании. Цель изобретения - упрощение генератора. Генератор содержит блоки 1, 2 памяти, демультиплексор 3, регистры 4, 5 памяти, блок 6 памяти, генератор 7 тактовых импульсов, первичный источник 8 случайных чисел, умножители 9, 10, коммутатор 11, сумматор 12, блок 13 памяти, цифроаналоговый преобразователь 14. 2 ил. 9 со со СП со со оо

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5ц 4 G 06 F 7 58

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К АBTOPCKOMY СВИДЕТЕЛЬСТВУ (21) 4070828/24-24 (22) 23.04.86 (46) 07.09.87. Бюл. № 33 (72) Ю. И. Абрамович, Н. И. Епифанов, О. В. Цыганов и Е. А. Чемес (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 748395, кл. G 06 F 7/58, 1978.

Авторское свидетельство СССР № 1068935, кл. G 06 F 7/58, 1982.

„„SU„„1335993 А 1 (54) ГЕНЕРАТОР СЛУЧА| |НЪ|Х ПРОЦЕССОВ (57) Изобретение относится к области вычислительной техники и может быть использовано при статистическом моделировании.

Цель изобретения — упрощение генератора.

Генератор содержит блоки 1, 2 памяти, демультиплексор 3, регистры 4, 5 памяти, блок

6 памяти, генератор 7 тактовых импульсов, первичный источник 8 случайных чисел, умножители 9, 10, коммутатор 11, сумматор

12, блок 13 памяти, цифроаналоговый преобразователь 14. 2 ил.

1335993

Изобретение относится к вычислительной технике и может быть использовано при статическом моделировании.

Цель изобретения — упрощение генератора.

На фиг. 1 дана блок-схема генератора; на фиг. 2 — временная диаграмма работы генератора.

Генератор содержит две группы блоков

1 и 2 памяти, демультиплексор 3, две группы регистров 4 и 5 памяти, блок 6 памяти, генератор 7 тактовых импульсов, первичный источник 8 случайных чисел, умножители 9 и 10, коммутатор !1, сумматор 12, блок 13 памяти, цифроаналоговый преобразователь 14.

До начала формирования случайного процесса, опережая его на интервал времени, достаточный для обнуления содержимого блока 6 памяти, на вход блока 6 поступает импульс, обнуляющий его содержимое.

В это же время на вход демультиплексора 3 поступает команда, определяющая номер канала, по которому на входу регистров 4 и 5 выхода генератора 7 импульсов должны поступать сигналы, разрешающие прохождение сигналов с выходов блоков 1 и

2 памяти через регистры 4 и 5 на входы умножителей 9 и 10. Выбор номера канала определяется требуемой спектральной плотностью генерируемого случайного процесса.

В момент начала формирования случайного процесса. на вход генератора 7 тактовых импульсов поступает управляющий сигнал, длительностью равный длительности формируемого случайного процесса. При этом осуществляется привязка первого синхроимпульса к переднему фронту управляющего сигнала.

Одновременно с этим на вход коммутатора 11 и на вход блока 13 памяти поступает управляющий импульс, разрешающий считывание информации с блока 13 и переводящий коммутатор 11 в состояние, при котором на его вход поступает информация с выхода блока 13 памяти.

Первый синхронизируюший импульс с выхода генератора 7 тактовых импульсов поступает на вход первичного источника 8 случайных чисел, блоков 1, 2 и 6 памяти и демультиплексор 3, через который по выбранному каналу он поступает на входы регистров 4 и 5. Начинается формирование первого отсчета случайного процесса.

После поступления первого синхронизирующего импульса на управляющий вход первичного источника 8 случайных чисел на его выходе формируется значение первого случайного числа, поступающее на вход умножителя 9, на второй вход первого умножителя 9 поступают значения вектора весовых коэффициентов, считываемые после поступления на входы блоков 1 первого синхроимпульса с выхода того блока 1, который подключен к открытому регистру 4.

Формула изобретения

5

Этот же синхроимпульс дает разрешение на считывание значений матрицы весовых коэффициентов с выходов блоков 2, которые соединены с регистрами 5. В связи с тем, что из N регистров 5 открыт только один, на вход умножителя 10 поступают значения матрицы весовых коэффициентов только с того блока 2, который соединен с открытым регистром 5. На второй вход умножителя 10 через коммутатор 11 поступают значения начального случайного вектора с выхода блока 13 памяти. Результаты перемножений случайного числа с выхода генератора 8 случайных чисел и вектора весовых коэффи циентов с выхода выбранного блока 1, а также матрицы весовых коэффициентов с выхода выбранного блока 2 и начального вектора с выхода блока 13 с выходов умножителей 9 и 10 в виде значений векторов поступают на входы сумматора 12. К моменту окончания суммирования синхроимпульс из единичного состояния переходит в нулевое, при котором осуществляется запись значений векторного сигнала с выхода сумматора 12 в блок 6. Первая компонента этого векторного сигнала является первым отсчетом случайного процесса и поступает на вход преобразователя 14.

К моменту появления на выходе генератора 7 тактовых импульсов второго синхроимпульса управляющий импульс на входе коммутатора ll и блока 13 оканчивается, коммутатор 11 переходит в состояние, при котором на его выход поступают записанные перед этим в блок 6 значения векторного сигнала.

С приходом второго синхроимпульса операции предыдущего такта повторяются за исключением того, что на второй вход умножителя 10 через коммутатор 11 поступают значения векторного сигнала не с выхода блока 13, а с выхода блока 6, считывание с которого осуществляется в течение действия на их управляющих входах единичного значения синхроимпульса. С выхода преобразователя 14 случайный процесс в аналоговой форме поступает на выход устройства. Этот процесс продолжается до тех пор, пока на управляющем входе генератора тактовых импульсов действует управляющий сигнал.

Генератор случайных процессов, содержащий первичный источник случайных чисел первый умножитель, сумматор, генератор тактовых импульсов, коммутатор, первый блок памяти, первую группу блоков памяти, цифроаналоговый преобразователь, первую группу регистров, памяти, отличающийся тем, что, с целью упрощения, он содержит второй блок памяти, вторую группу блоков памяти, вторую группу регистров памяти, 1335993

Составитель A. Карасов

Редактор Л. его ров а Техред И. Верес Корреектор С. Черни

За каз 3803/44 Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 второй умножитель и демультиплексор, выходы которого соединены с синхронизирующими входами регистров памяти первой и второй групп соответственно, а управляющий вход демультиплексора является входом задания спектральной плотности генератора, входом «Пуск» которого является вход «Пуск» генератора тактовых импульсов, выход которого соединен с информационным входом демультиплексора, со считывающим входом первого блока памяти, со считывающими входами блоков памяти первой и второй групп и с входом «Опрос» первичного источника случайных чисел, выход которого соединен с первым входом первого умножителя, выход которого соединен с первым входом сумматора, выход которого соединен с информационным входом первого блока памяти и с входом цифроаналогового преобразователя, выход которого является выходом генератора, входом «Подготовка» которого является вход обнуления первого блока памяти, выход которого соединен с первым информационным входом коммутатора, управляющий вход которого является входом «Начало цикла» генератора и соединен с считывающим входом второго блока памяти, выход которого соединен с вторым информационным входом коммутатора, выход которого соединен с первым входом второго умножителя, выход которого соединен с вторым входом сумматора, выходы блоков памяти первой группы соединены с информационными входами соответствующих регистров памяти первой группы, выходы которых соединены с вторым входом первого умножителя, выходы блоков памяти второй группы соединены с информационными входами соответствующих регистров памяти второй группы, выходы которых соединены с вторым входом второго у множителя.